Multi-rate decoder for binary QC-LDPC codes and decoding method thereof

A multi-bit-rate, decoder technology, applied to coding elements, error detection coding and coding using multi-bit parity bits, etc., can solve complex on-chip interconnection, unoptimized algorithm mapping process, and low efficiency of hardware resource usage and other issues to achieve the effect of improving decoding efficiency and utilization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] The present invention will be further explained below in conjunction with the drawings.

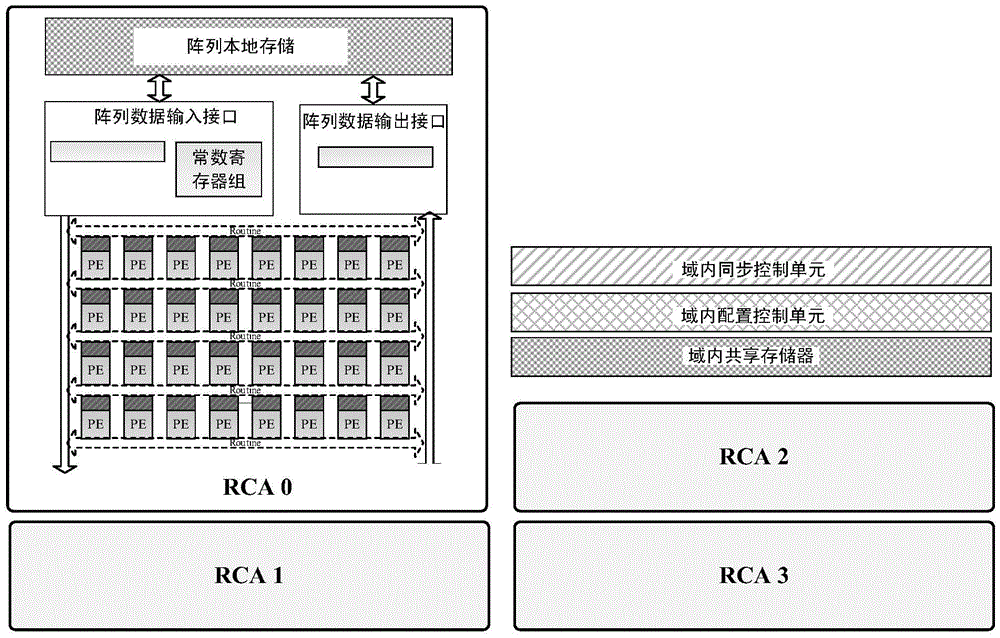

[0026] In the multi-rate QC-LDPC decoding system, the reconfigurability of the computing unit array is the key to multi-rate decoding in the wireless communication field, and determines the efficiency of decoding completion; through the reconfigurable computing unit array, Real-time decoding; in the present invention, after a decoding is completed, the configurable computing unit array is reconfigured according to different pre-configuration information.

[0027] A multi-rate binary QC-LDPC code decoder based on a configurable computing array architecture includes a main controller, a main decoding arithmetic unit, a data storage unit and a data transmission path. The main controller is used to receive decoding requests and extract decoding rate information; the main decoding arithmetic unit includes a configurable calculation unit array, an array configuration control logic unit and a ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More