Automated testing method for fpga local interconnect resource based on reconfigurable unit

A technology of automated testing and partial interconnection, applied in error detection/correction, faulty computer hardware, instrument detection, etc., can solve problems such as increased complexity, reduce wiring requirements, reduce configuration generation difficulty, and high fault coverage rate effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] There are many ways to repeat the construction of the configuration unit, and the configuration methods are as follows:

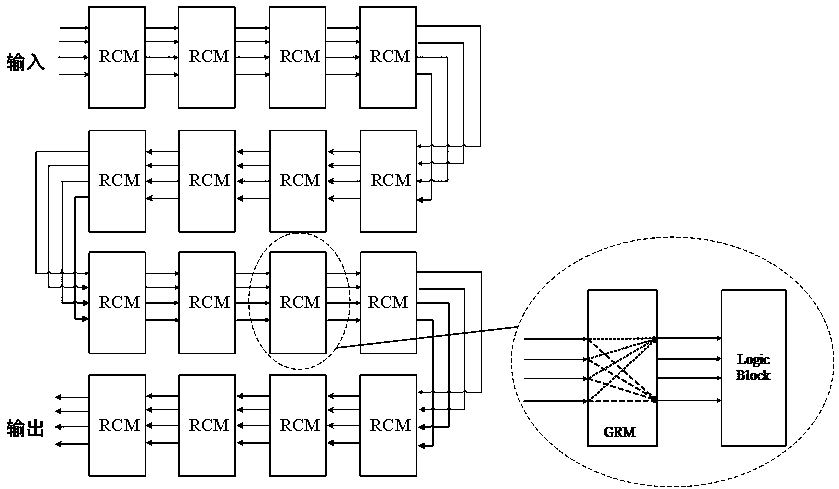

[0036] For the repeated configuration unit composed of CLB and local interconnection, the lookup table in CLB is divided into Figure 4 Configured in the manner shown 8 , specifically, configure the adjacent eight LUTs into a specific operation form, and all input signals are connected to the input terminals of the first four LUTs. For the last four LUTs, one of the input signals comes from a specific front-end LUT. output (for example, an input of the fifth LUT comes from the output of the first LUT, an input of the sixth LUT comes from the output of the second LUT, and so on), other input signals are connected to the first four LUT inputs The signals are exactly the same. The result of logical operation among them ensures that the output signal is completely consistent with the input signal. For other input terminals in CLB, such as enable input...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com