Timing sequence netlist management method and device

A management method and a management device technology, which are applied in the field of timing netlist management methods and devices, and can solve the problems of large memory usage and large timing netlist contents, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

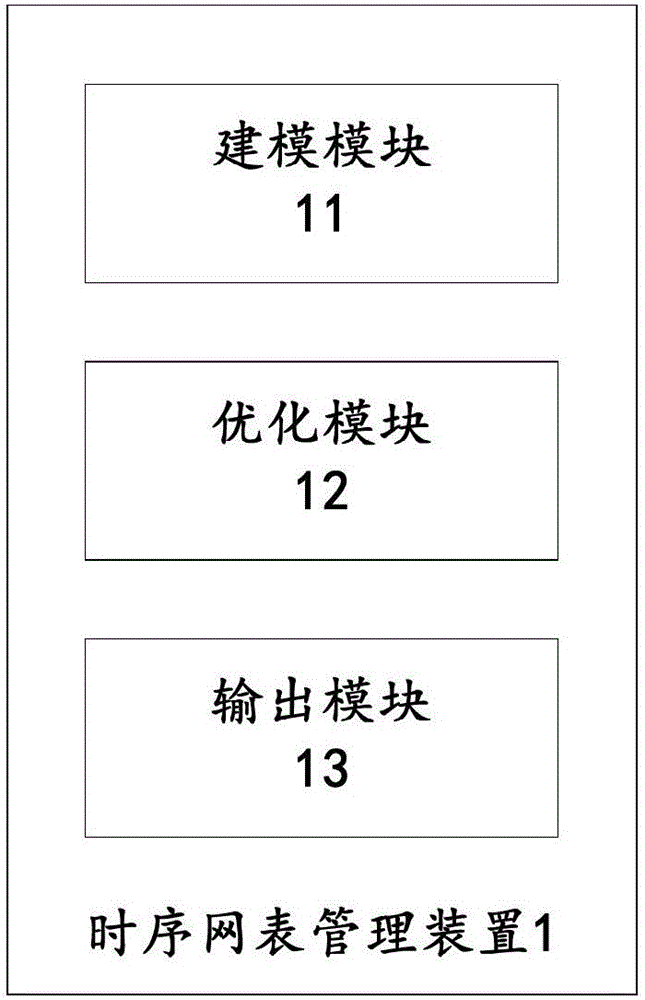

[0032] figure 1 It is a schematic structural diagram of the sequential netlist management device provided in the first embodiment of the present invention, which is composed of figure 1 It can be seen that in this embodiment, the timing netlist management device 1 provided by the present invention includes:

[0033] The modeling module 11 is used to obtain the timing netlist according to the design file, search the timing model of each device in the timing netlist, and establish a sub-timing netlist for each device; the sub-timing netlist includes all nodes of the device, each node and other nodes Connection relationship, the node includes the pin of the device;

[0034] The optimization module 12 is used to obtain the path delay information of the input node and its forward path in the sub-sequence netlist, add the path delay information of the forward path to the backward path of the input node, and delete the sub-sequence netlist Input nodes and their forward paths;

[0...

no. 2 example

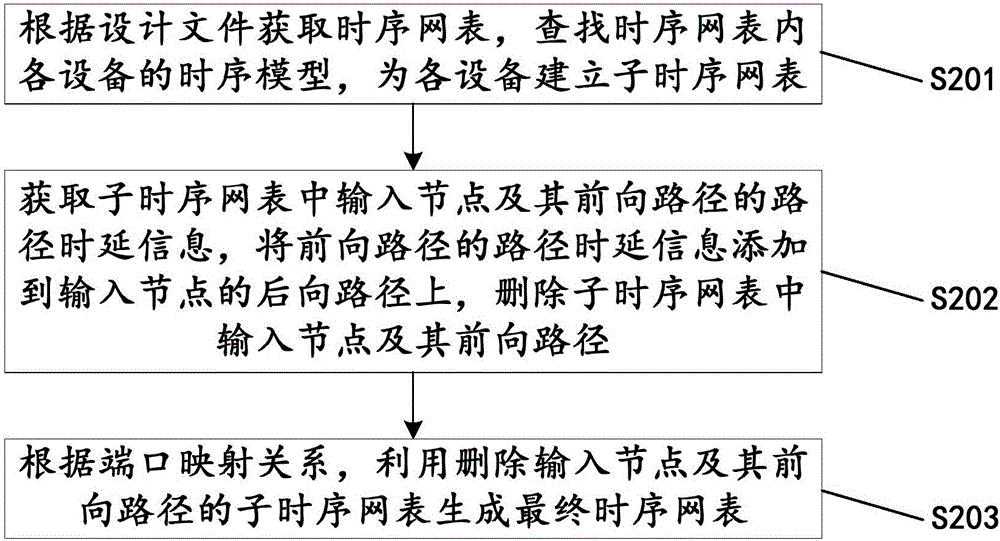

[0041] figure 2 The flow chart of the sequential netlist management method provided by the second embodiment of the present invention is composed of figure 2 It can be seen that in this embodiment, the timing netlist management method provided by the present invention includes:

[0042] S201: Acquire the timing netlist according to the design file, search for the timing model of each device in the timing netlist, and establish a sub-timing netlist for each device; the sub-timing netlist includes all nodes of the device, the connection relationship between each node and other nodes, and the nodes include device pins;

[0043] S202: Obtain the path delay information of the input node and its forward path in the sub-sequence netlist, add the path delay information of the forward path to the backward path of the input node, delete the input node and its forward path in the sub-sequence netlist forward path;

[0044] S203: According to the port mapping relationship, a final ti...

no. 3 example

[0051] This example provides a timing netlist optimization method based on static timing analysis, which is used to optimize the storage structure of timing paths in the timing netlist, reduce memory usage, and improve the operating efficiency of EDA software while ensuring the accuracy of analysis results. This optimization method has two usages in timing analysis. One is to optimize the timing netlist of each device, and then connect each sub-timing netlist into the final netlist; the other is to directly optimize the final timing netlist. The netlist is optimized. The memory resources consumed by the two usages are the same, but the peak value of memory consumed by the second method will be higher than that of the first method. The code implementation of the first method is more complicated than the second method. Which one to use can be determined according to the situation. choose.

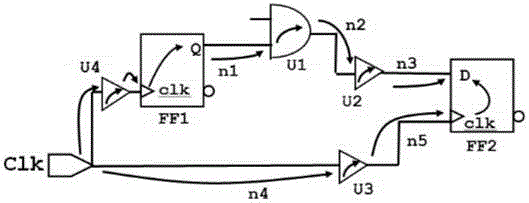

[0052] Such as image 3 As shown, the timing netlist management scheme provided by the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More