NAND Flash fault-tolerance method based on FPGA (Field Programmable Gate Array)

A content and bad block technology, applied in the field of Flash fault tolerance, can solve problems such as data cannot be read and written normally, Flash scrapping, system instability, etc., to solve the problem of bad block detection and management, improve storage performance, The effect of ensuring data security

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] The present invention will be further described below in conjunction with drawings and embodiments.

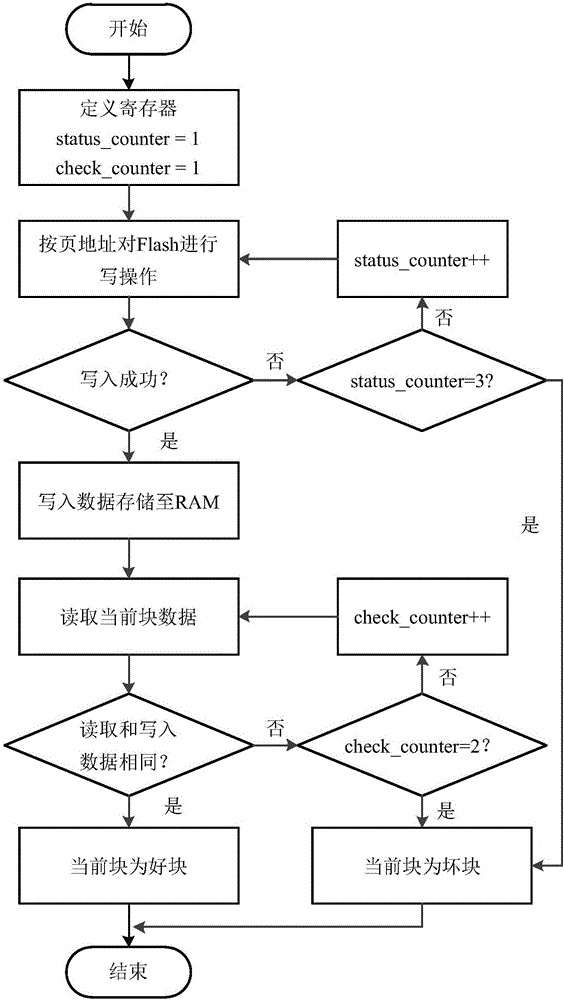

[0032] Such as figure 1 As shown, the Flash bad block detection process is as follows:

[0033] (1) Perform write operations on all blocks of the Flash chip according to the page address through the FPGA, and write one page at a time. After a write cycle is over, it is judged whether the writing is successful by checking the writing status flag bit. If the writing is not successful for 3 consecutive times, it is judged that the current block is a bad block;

[0034] (2) If the writing is successful, the writing data is stored in RAM. Read the content of the current block and compare it with the written data in RAM. If the content of reading and writing is different for two consecutive times, it is judged that the current block is a bad block;

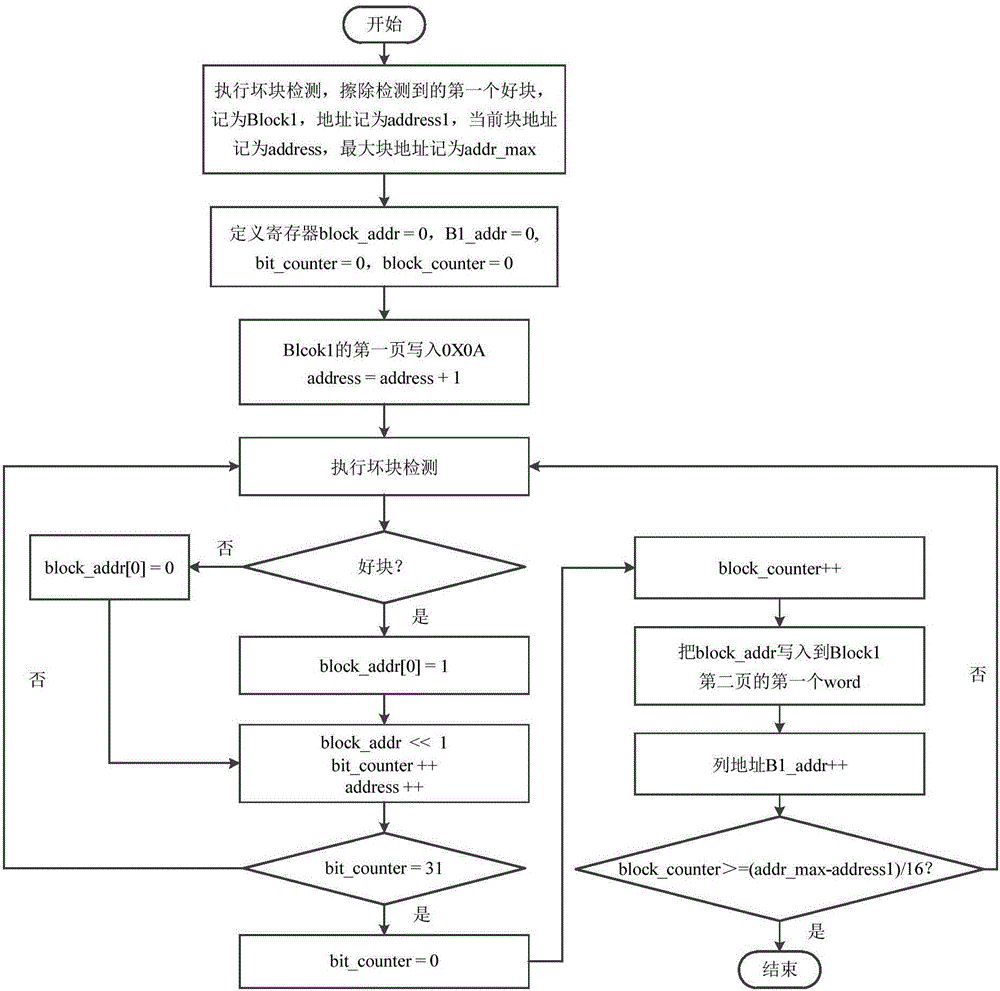

[0035] Such as figure 2 As shown, the bad block management process is as follows:

[0036] (1) Perform an erase operation...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More