Method for verifying I2C (Inter-Integrated Circuit) bus interface

A bus interface and interface technology, which is applied in the verification field of I2C bus interface in the FPGA verification stage, can solve the problems of FPGA port burnout and low clock bus, and achieve the effect of reducing chip tape-out costs and I2C function problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

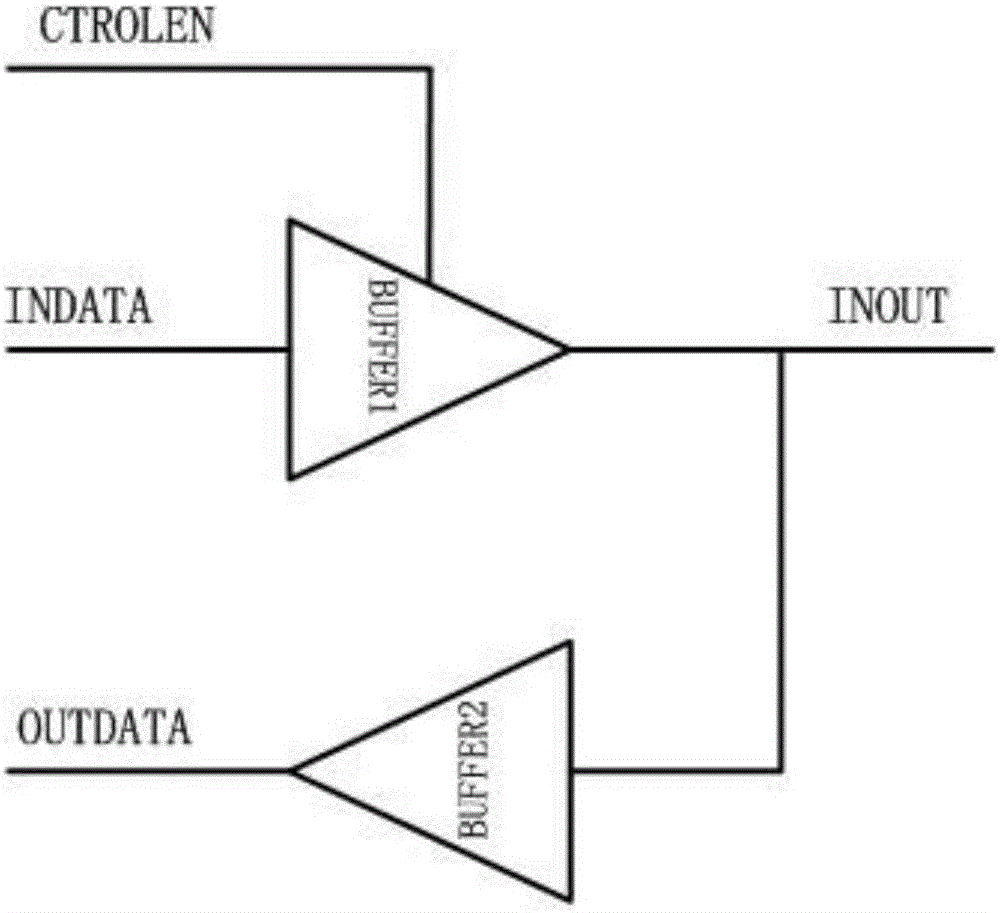

[0018] see image 3 As shown, the method for verifying the I2C bus interface realized by the present invention first decomposes the function of the tri-state port, and the tri-state port should make the port have both input and output functions, and then use the four-wire interface through the PNP triode, Imitate the open-drain structure of I2C to realize docking communication with external modules. The circuit that imitates the I2C open-drain structure is as follows image 3 shown. Before FPGA verification, the digital logic first decomposes the three-state port into a complete input function p...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More