High-performance multi-port DDR (double data rate) controller and method for implementing same

A controller and high-performance technology, which is applied in the field of data communication, can solve the problems of DDR controllers having only one user port, waste of pins and logic resources, etc., to ensure bandwidth utilization, save pin resources and logic resources, and simplify The effect of design difficulty

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

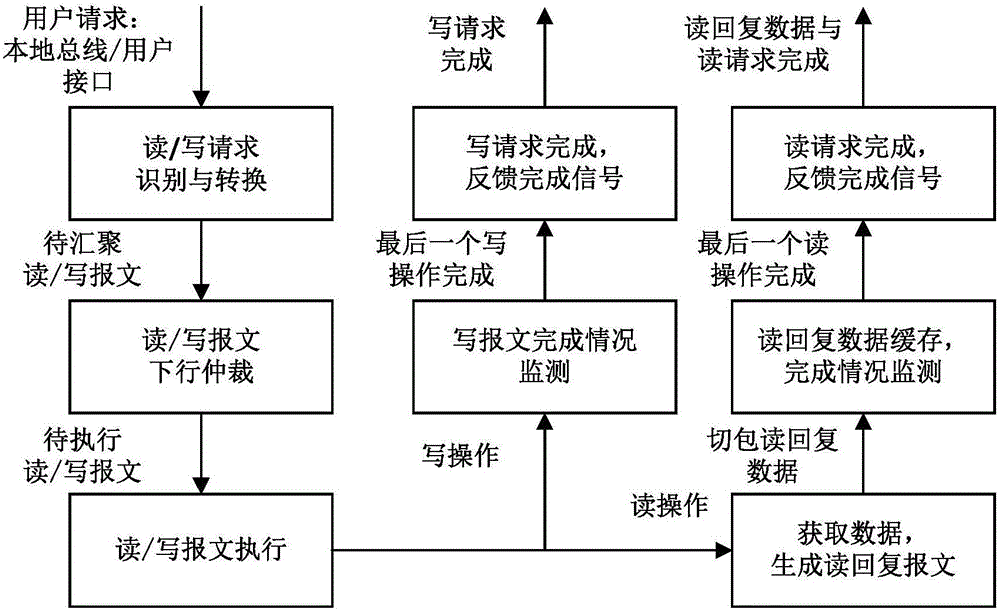

[0039] In order to meet the needs of multiple users accessing the same DDR interface at the same time, in addition to providing users with an easy-to-use interface, it supports users to read and write on the local bus or transfer large blocks of data similar to DMA (Directional Memory Access, direct memory access); At the same time, it is necessary to reasonably allocate the bandwidth of the DDR interface (only for the user interface in the working state to evenly allocate bandwidth), so as to improve the bandwidth utilization.

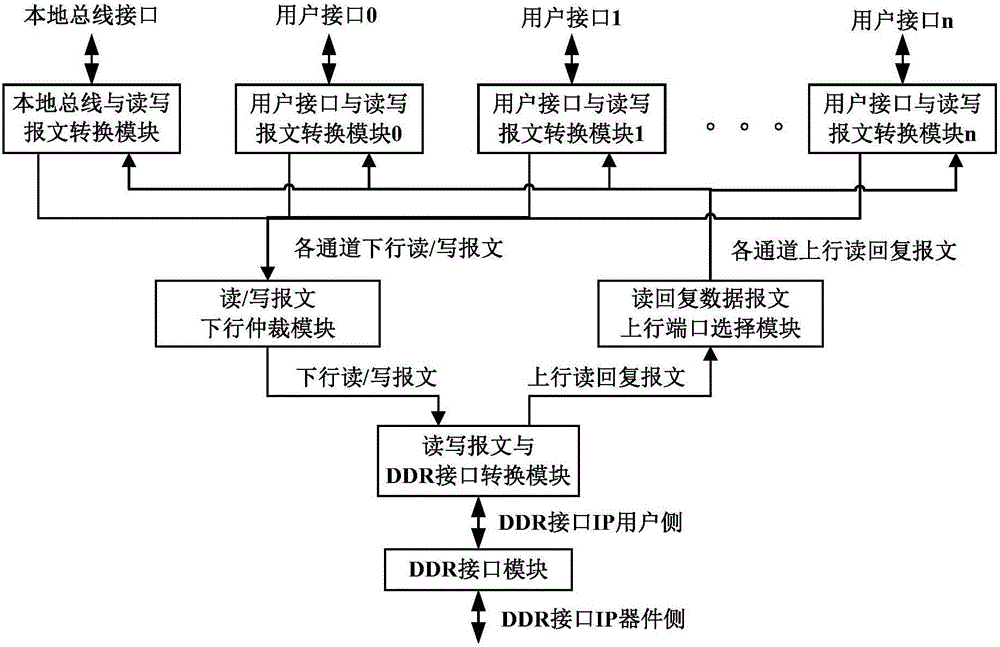

[0040] see figure 1 As shown, the embodiment of the present invention provides a high-performance multi-port DDR controller, the controller includes a local bus and read and write message conversion module, a user interface and a read and write message conversion module, and a read / write message downlink arbi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More