Sub-threshold to super-threshold cmos level-shifting circuit against single event effect

An anti-single event effect and ultra-threshold technology, applied in logic circuits, electrical components, reliability improvement and modification, etc., can solve problems such as faults and system errors, and achieve the effects of reliable circuit operation, avoiding flipping, and low cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

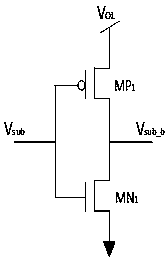

[0023] Such as figure 1 , in this embodiment, the inverting unit includes a PMOS transistor MP 1 and an NMOS tube MN 1 , MP 1 The source is connected to the power supply, and the drain is connected to the MN 1 The drain, and as the signal output terminal V of the inverting unit sub_b ; MN 1 The source of the ground; MP 1 The gate and MN 1 The gate is connected and used as the signal input terminal V of the inverting unit sub .

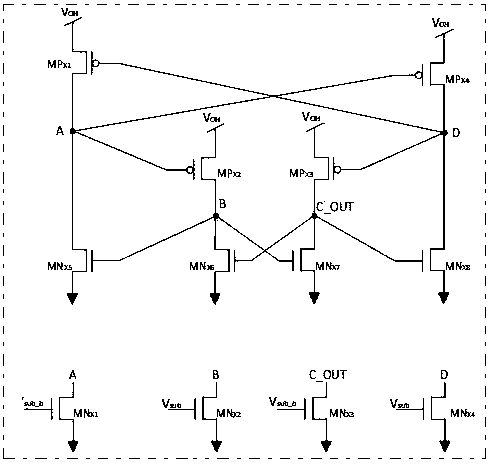

[0024] Such as figure 2 , the level conversion unit from sub-threshold to super-threshold with anti-single event effect consists of 4 PMOS transistors MP X1 , MP X2 , MP X3 , MP X4 , and 8 NMOS tubes MN X1 , MN X2 , MN X3 , MN X4 , MN X5 , MN X6 , MN X7 , MN X8 Composition, where MP X1 , MP X2 , MP X3 , MP X4 and MN X1 , MN X2 , MN X3 , MN X4 constitutes the level conversion module, MP X1 , MP X2 , MP X3 , MP X4 and MN X5 , MN X6 , MN X7 , MN X8 Constitute the anti-single event effect module.

[0025] MP X1 , MP ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More