Complementary Cmos Structure And Method

A field-effect transistor and metal-oxide-semiconductor field-effect transistor technology, which is applied in the field of complementary metal-oxide-semiconductor field effect transistor structure and fabrication, can solve the problems of surface area and occupation of multiple integrated circuits.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

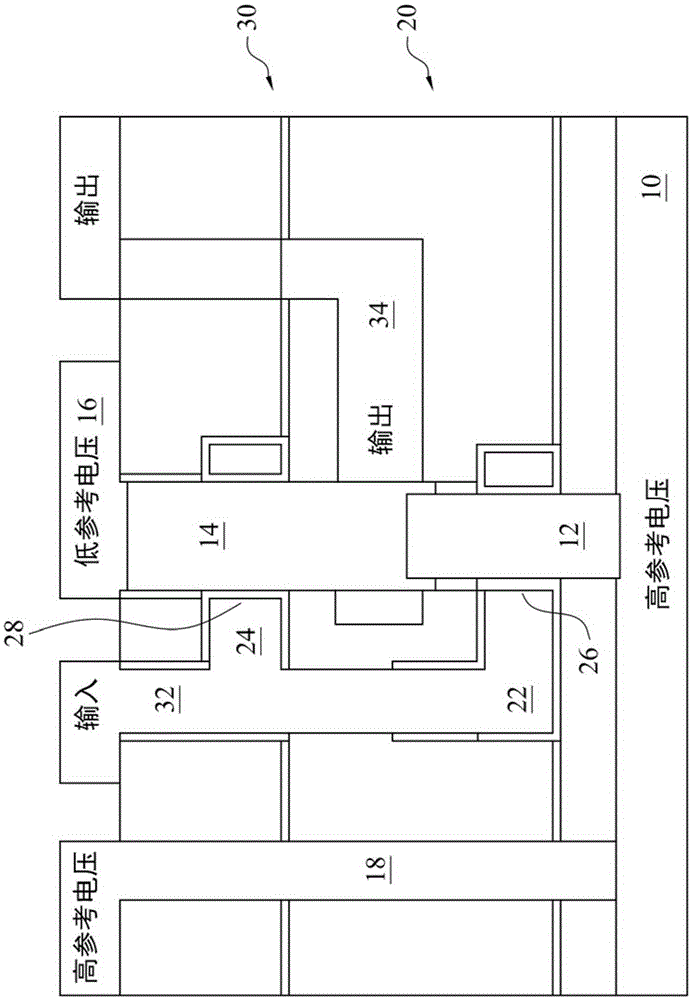

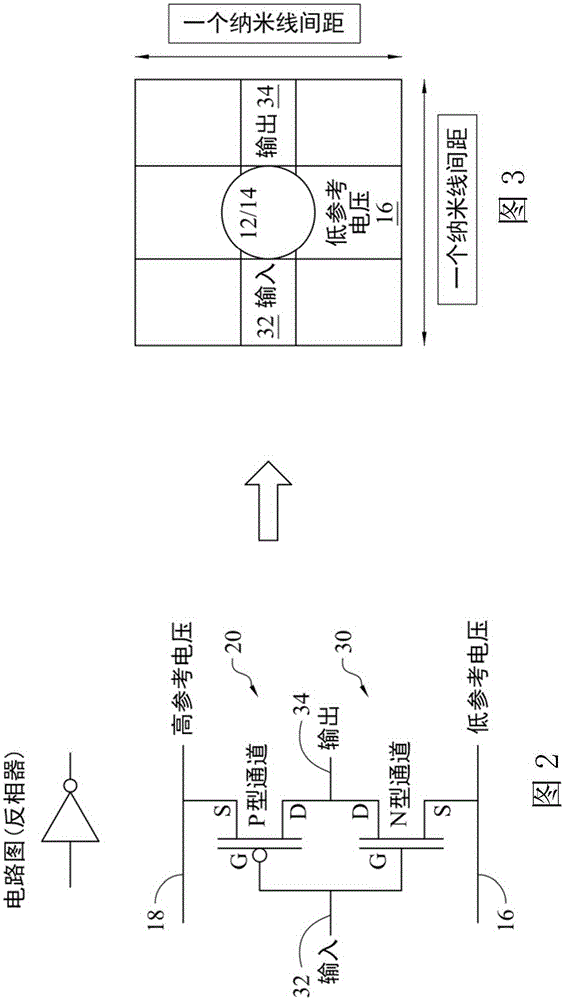

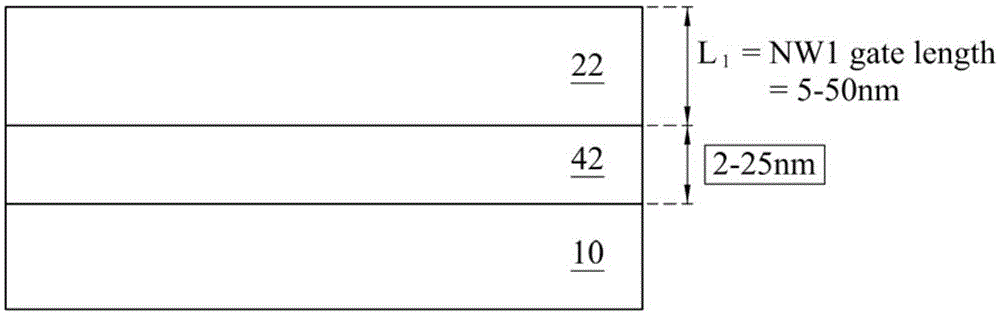

[0016] The making and using of this embodiment are discussed in detail below, however, it should be appreciated that the present invention provides practical innovative concepts which can be embodied in a wide variety of specific contexts. The specific examples discussed below are illustrative only and do not limit the scope of the invention.

[0017] Embodiments of the present invention will be described below with specific content, that is, using stacked vertical surround (VGAA) or nanowire (NW) transistors as structures. Nevertheless, the innovative concepts of the present invention are not limited to the formation of specific structures. In fact, the innovative concept of the present invention can also be used for other structure formations. Furthermore, even though the present invention is directed to vertical wrap-around or nanowire circuit embodiments, the innovative concepts of the present invention can be applied to other types of integrated circuits, electronic stru...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More