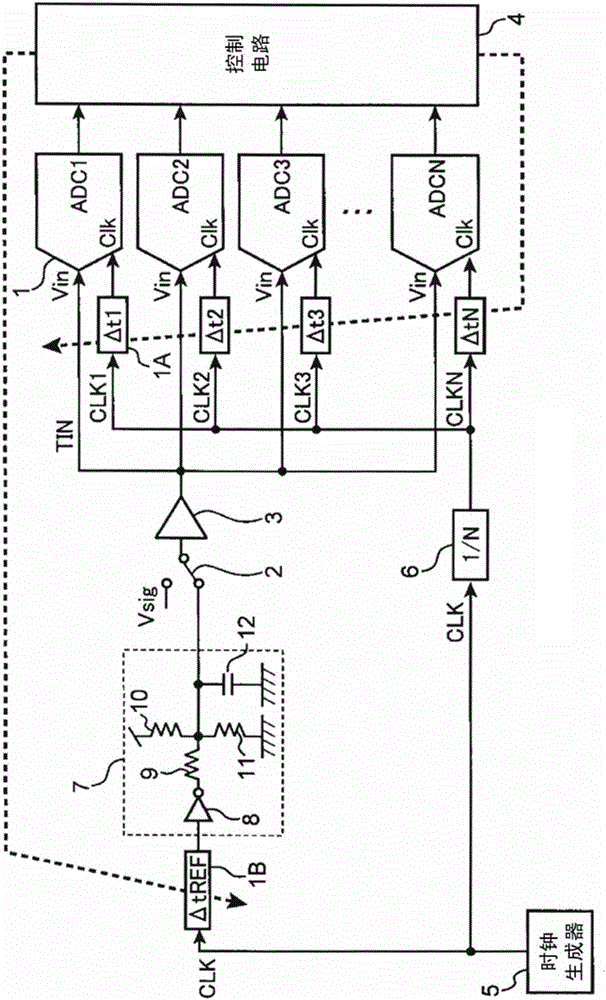

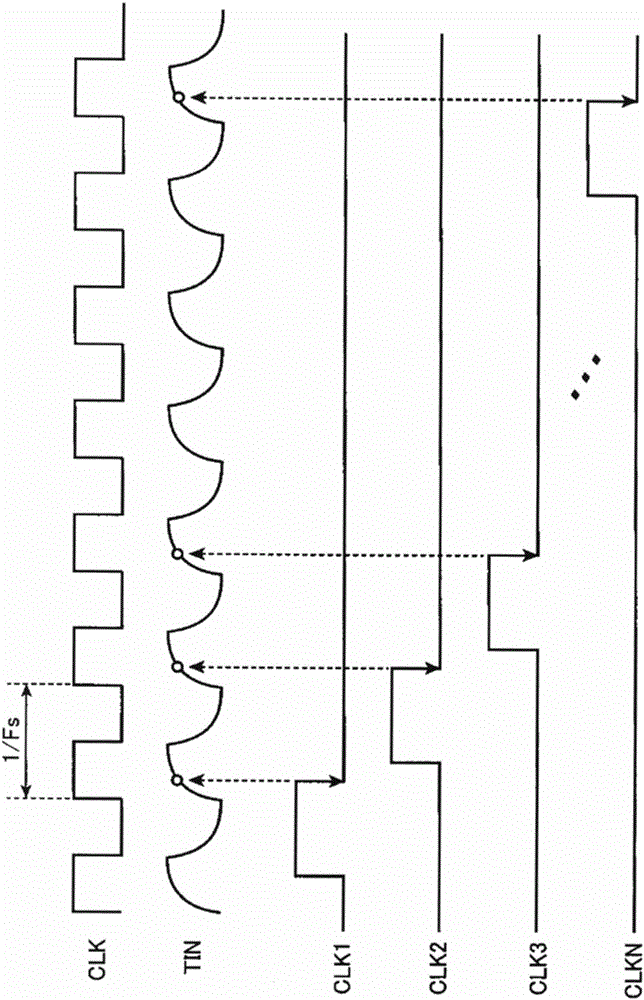

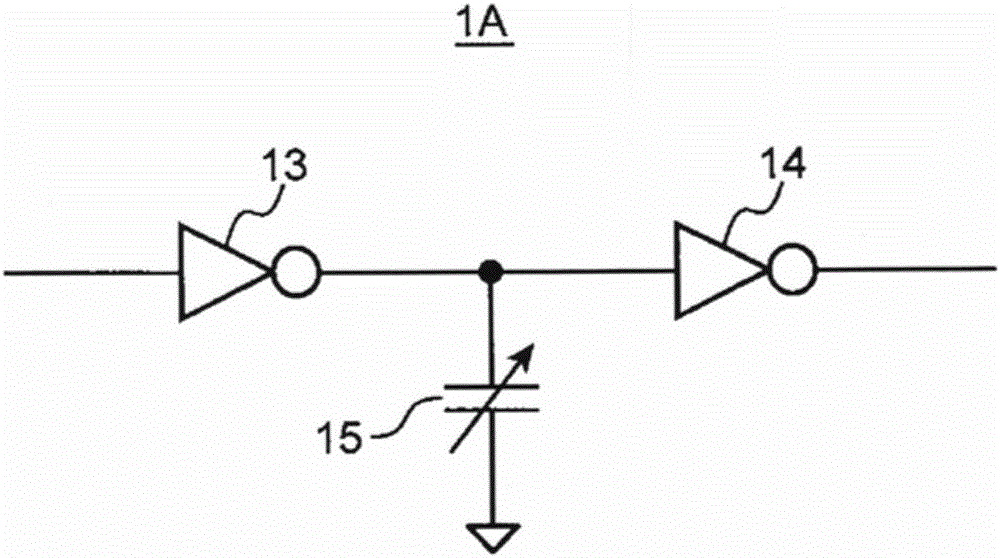

Time-interleaved analog-to-digital converter

A time interleaving and converter technology, applied in the direction of analog-to-digital converter, code conversion, analog-to-digital conversion, etc., can solve problems such as SN ratio deterioration, and achieve the effect of timing offset correction and reduction of timing offset.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] (recognition that is the basis of this application)

[0035] First, knowledge that is the basis of this application will be described. In the conventional timing offset correction method, when the speed of the AD converter is increased and the resolution is increased, it is necessary to divide the phase control steps of the DAC output into finer steps, which leads to an increase in the correction time and an increase in the correction time. The complication of the additional circuit. In addition, it is difficult to generate reference signals such as ramp waves as the speed and resolution of AD converters increase.

[0036] Therefore, the inventors of the present invention have made intensive studies in order to realize a time-interleaved AD converter capable of correcting the timing offset accurately and preventing the occurrence of AD conversion errors while suppressing the scale of the additional circuit for correction.

[0037] A technical solution of the present a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com