Power-up/power-down reset circuit and chip

A technology of electric reset and circuit, which is applied in the field of circuits, can solve problems such as unstable circuit node voltage and logic state of circuit components, achieve the effects of reducing energy consumption, fewer branches, and improving reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

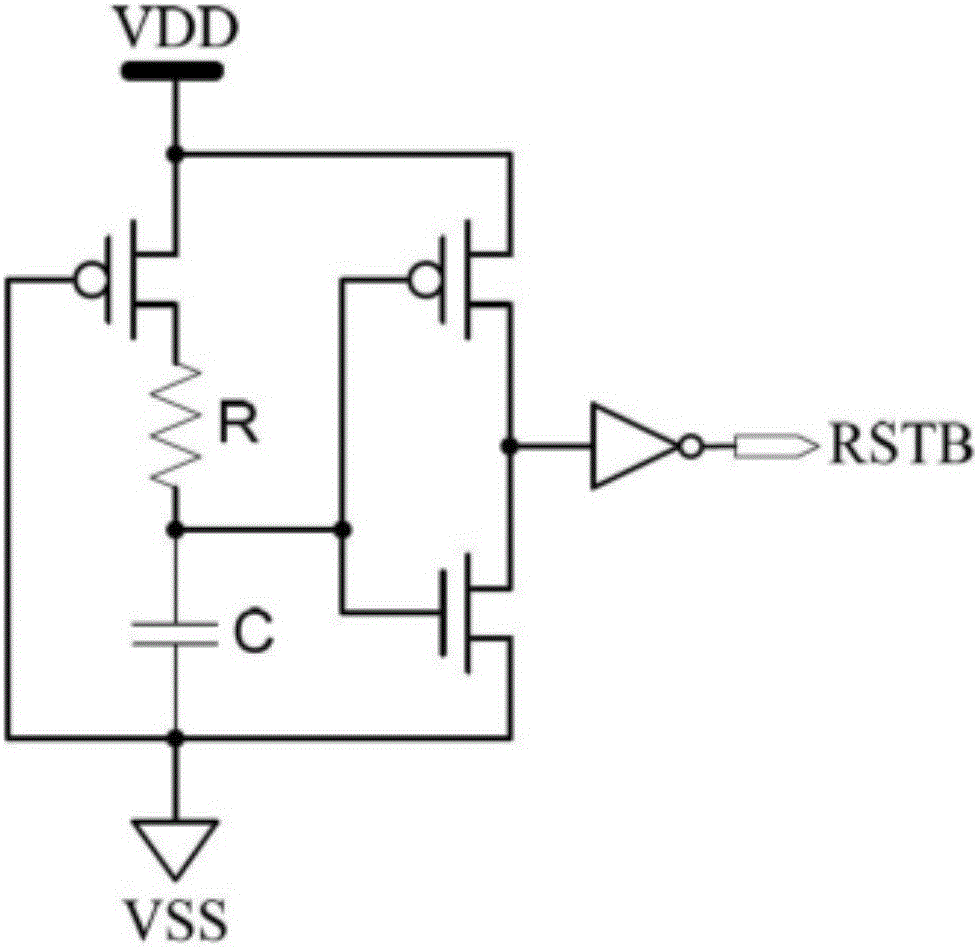

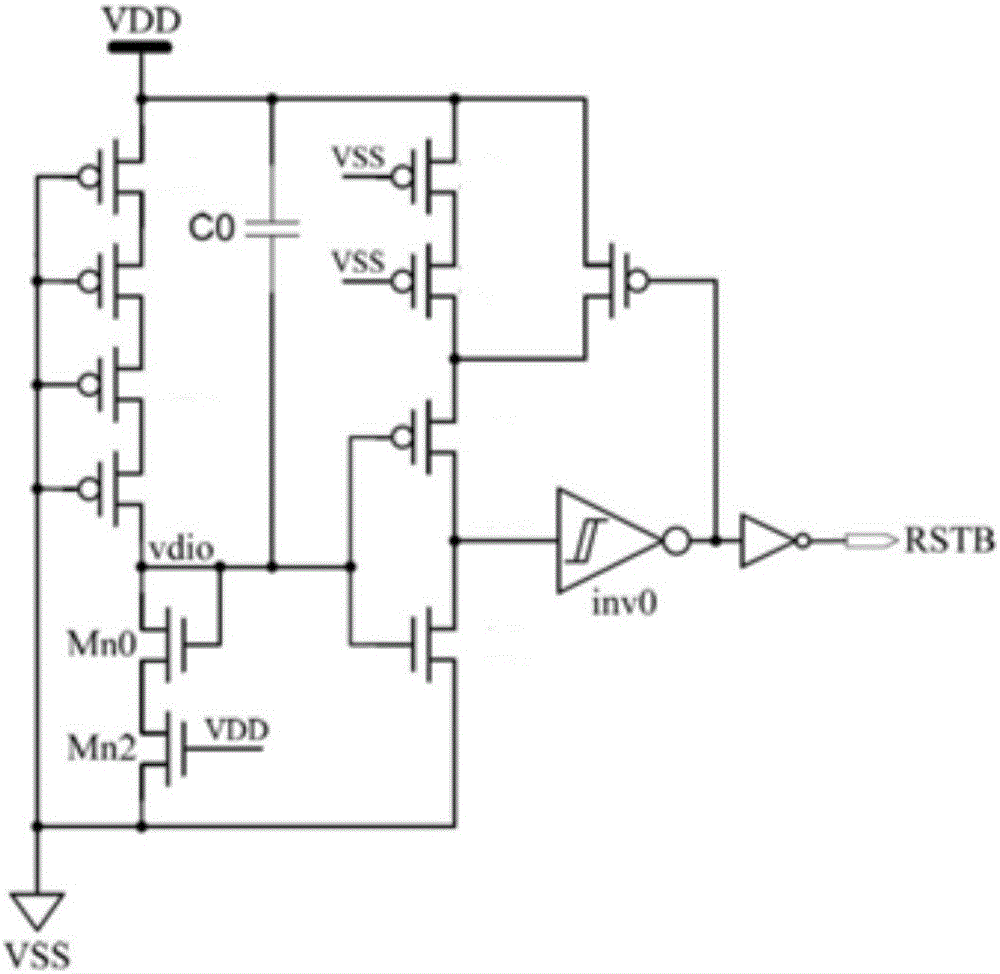

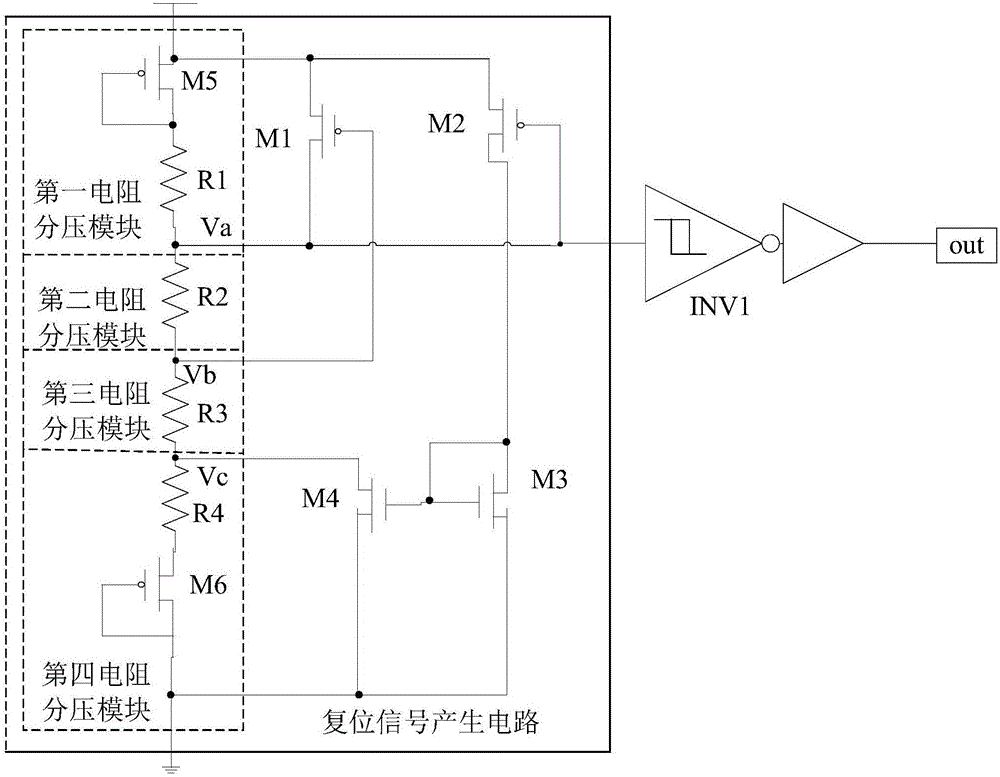

[0026] In order to make the object, technical solution and advantages of the present invention clearer, the specific implementation manners of the power-on and power-down reset circuit and the chip including the circuit of the present invention will be described below in conjunction with the accompanying drawings. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

[0027] It should also be noted that in the power-on and power-down reset circuits of the following embodiments, NMOS transistors and PMOS transistors are involved, and the NMOS transistors and PMOS transistors have corresponding source S, drain D, and gate G respectively. However, due to the symmetrical structure of the NMOS transistor and the PMOS transistor, when the NMOS transistor and the PMOS transistor are connected, the connection positions of the source S and the drain D are substantially interchangeable. C...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More