Binary frequency shift keying with data modulated in the digital domain and carrier generated from an intermediate frequency

A frequency shift keying, binary technology, applied in the direction of frequency modulation carrier system, modulation carrier system, phase modulation carrier system, etc., can solve problems such as difficulty in eye diagram

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

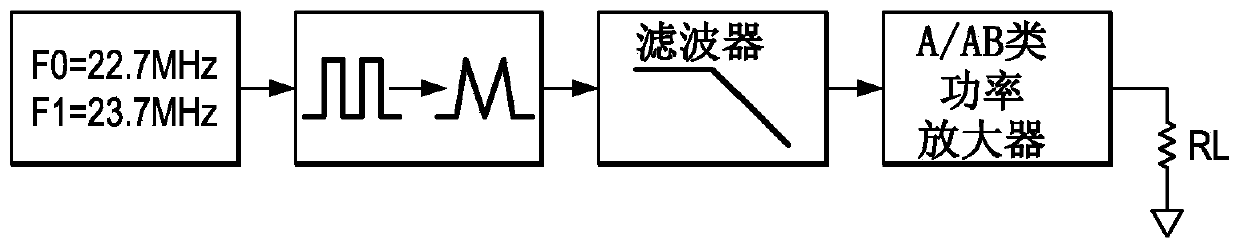

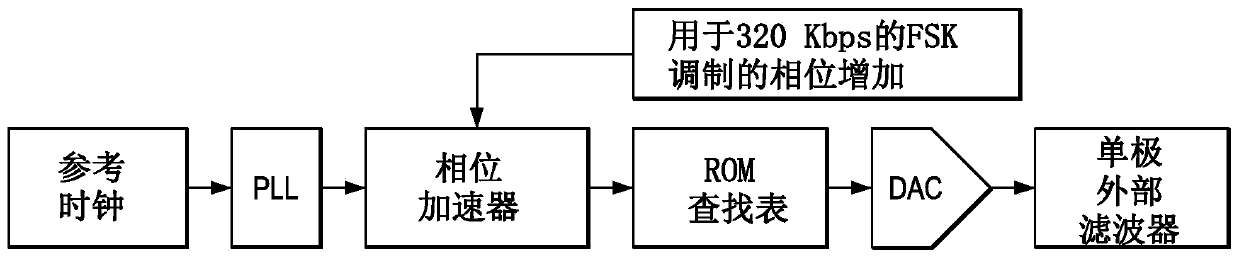

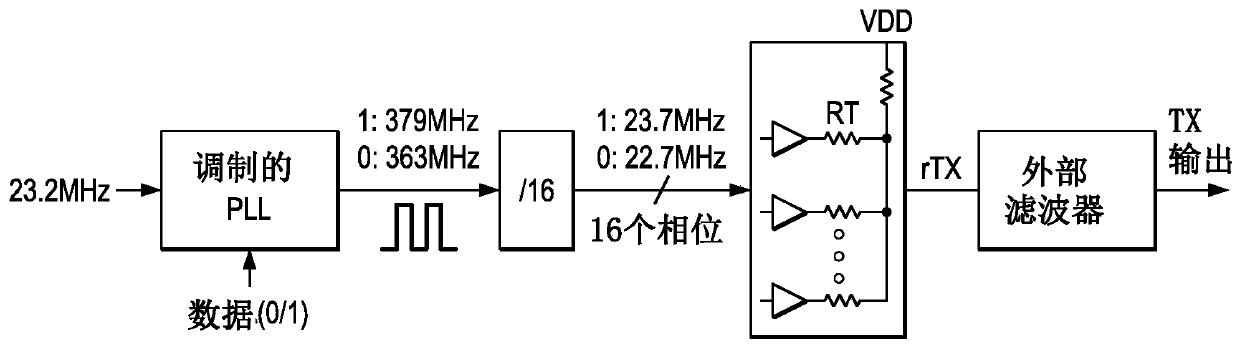

[0011] Example embodiments implement BFSK modulation (such as implementing the USB PD specification) by selecting the appropriate phase of the high frequency clock to produce a modulated intermediate clock frequency. The high frequency clock is chosen as (M+0.5)*fc, where fc is the carrier frequency and M is an integer. Convert "M" or "M+1" clock phases from a high-frequency clock to an intermediate clock whose frequency is 2*N of the carrier frequency, depending on the binary data "1" or "0" to be transmitted times, where N is an integer. This intermediate clock, generated entirely in the digital domain, has the required data modulation within it and is used to generate the N pulse width modulated (PWM) phases of the waveform operating at the carrier frequency. The N phases are then appropriately weighted to synthesize the output sinusoidal waveform. In some embodiments, significant harmonic content is only present at the (2*N-1) harmonic and upwards in the output sinusoida...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More