Fast delay signal cancellation filtering method and device, equipment and storage medium

A time-delayed signal and fast technology, applied in harmonic reduction devices, AC networks to reduce harmonics/ripples, and flicker reduction of AC networks, etc., can solve the problem that the advantages are not obvious, affect the dynamic performance of the system, and the computing power of the controller Weakness and other problems, to achieve the effect of strong ability to filter out harmonics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0094] The fast delay signal destructive filtering method provided in the embodiment of the present application includes:

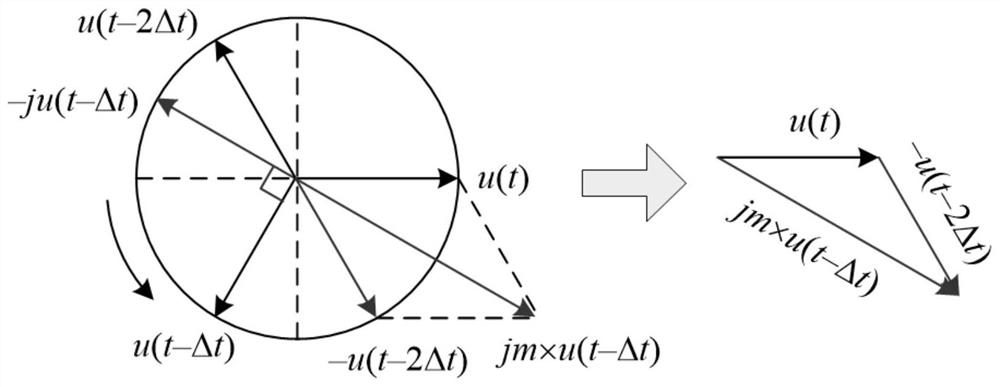

[0095] Set the appropriate delay Δt and parameter m, by sampling the three grid voltage signals u(t), u(t–Δt) and u(t–2Δt), based on the vectorial nature of the voltage, the harmonics in the three samples Form vector triangles, such as figure 1 As shown, there is u(t)–u(t–2Δt)=m×ju(t–Δt), thus eliminating the harmonic;

[0096] m is the filter parameter;

[0097] j is the imaginary part in the complex field coordinate system;

[0098] –ju(t–Δt) is the quadrature signal lagging u(t–Δt) by 90°;

[0099] The u(t) is the voltage at the current moment, and u(t-Δt) and u(t-2Δt) are the sampling voltages at two lagging moments.

[0100] In some embodiments, the specific method for setting the appropriate delay Δt and parameter m includes:

[0101] Make the delay Δt=T / n;

[0102] The formula u(t)–u(t–2Δt)=m×ju(t–Δt) is:

[0103]

[0104] Among them, T i...

Embodiment 2

[0126] A fast delay signal destructive filtering device, comprising:

[0127] Voltage sampling module, fast delay signal cancellation operator construction module and time domain calculation module;

[0128] The voltage sampling module: sample grid voltage u(t), u(t–Δt) and u(t–2Δt) three times, the u(t) is the voltage at the current moment, u(t–Δt) and u(t –2Δt) is the sampling voltage at two lag moments;

[0129] The fast delay signal cancellation operator construction module: set the appropriate delay Δt and parameter m, so that the harmonics in the three samples form a vector triangle, then u(t)-u(t-2Δt)=m ×ju(t–Δt);

[0130] Make the delay Δt=T / n;

[0131] The formula u(t)–u(t–2Δt)=m×ju(t–Δt) is:

[0132]

[0133] Among them, T is the fundamental wave period, n is the delay coefficient, is a fast delay signal cancellation operator;

[0134] The time-domain calculation module: based on the orthogonal relationship between the two-phase voltages in the αβ coordinat...

Embodiment 3

[0138] Based on the above embodiments, the FDSC is applied to eliminate the h=6k+1 harmonic. due to h * =1 corresponds to the positive sequence component of the fundamental wave, which needs to be decomposed into several groups h * For the harmonic subset of ≠1, the cascaded FDSC is used to eliminate each group of harmonics one by one. For example, the harmonics such as –5, 7, –17, and 19 can be expressed in the form of h=12k–5 (k=0, ±1, ±2…). Substitute n=12 and h * =–5, then there is m=–1, so as to get FDSC(–1,12), the time domain expression is

[0139]

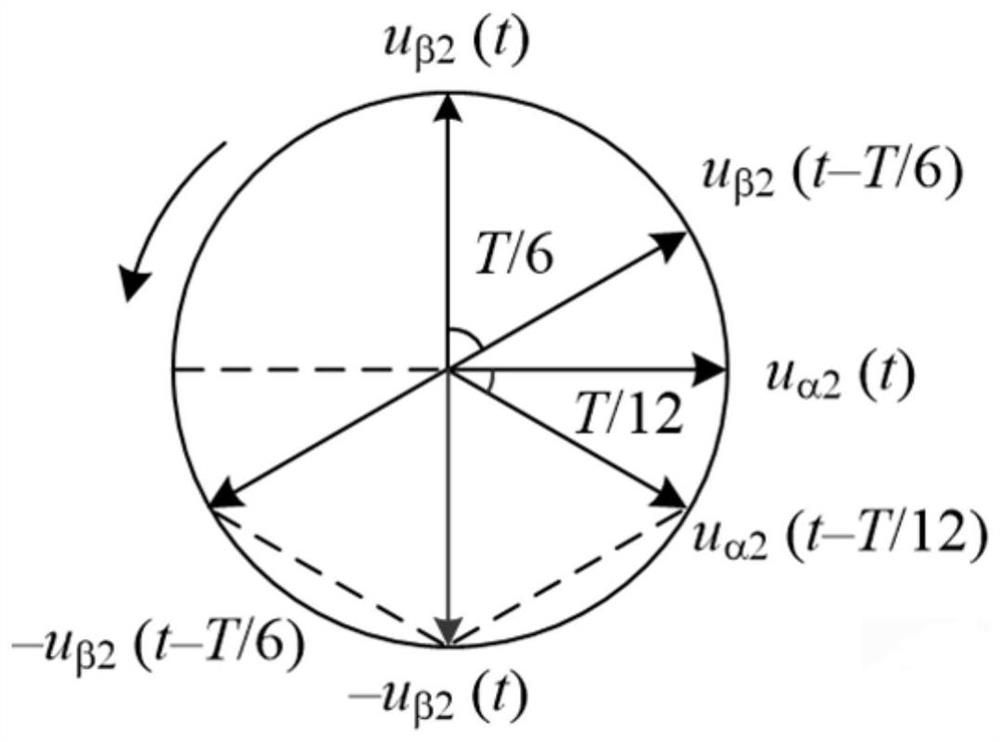

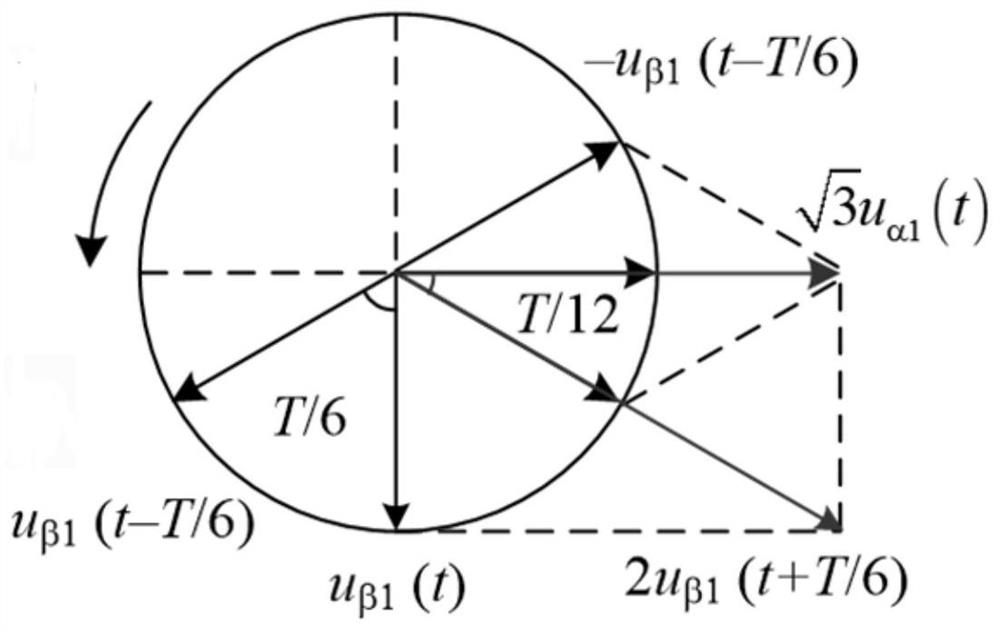

[0140] Substitute h=-1 into FDSC(-1,12), then there is 2sin(2hπ / n)-m=0. This shows that FDSC(–1,12) not only suppresses the h=12k–5th harmonic effectively, but also eliminates the negative sequence component of the fundamental voltage at the same time. Figure 2 is its vector diagram to eliminate the voltage u β The fundamental negative sequence component u in β2 As an example, u in Figure 2(a) α2 (t–T / 12) with –u...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More