Formation method of semiconductor structure

A semiconductor and gate structure technology, applied in the field of semiconductor structure formation, can solve the problems of transistor performance and stability degradation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

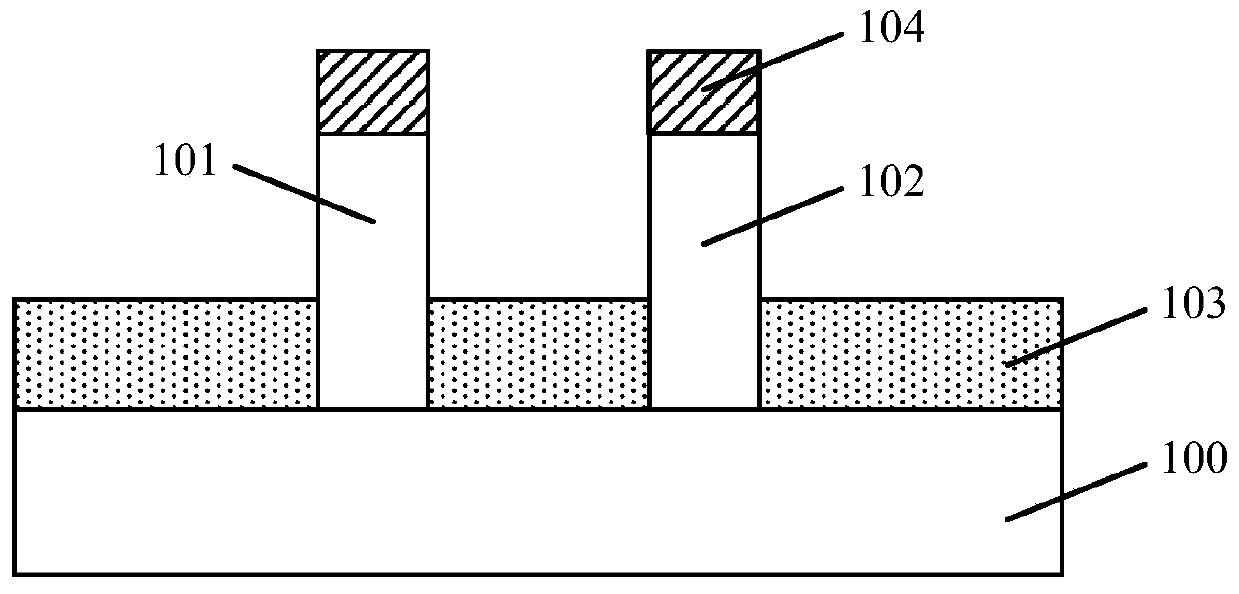

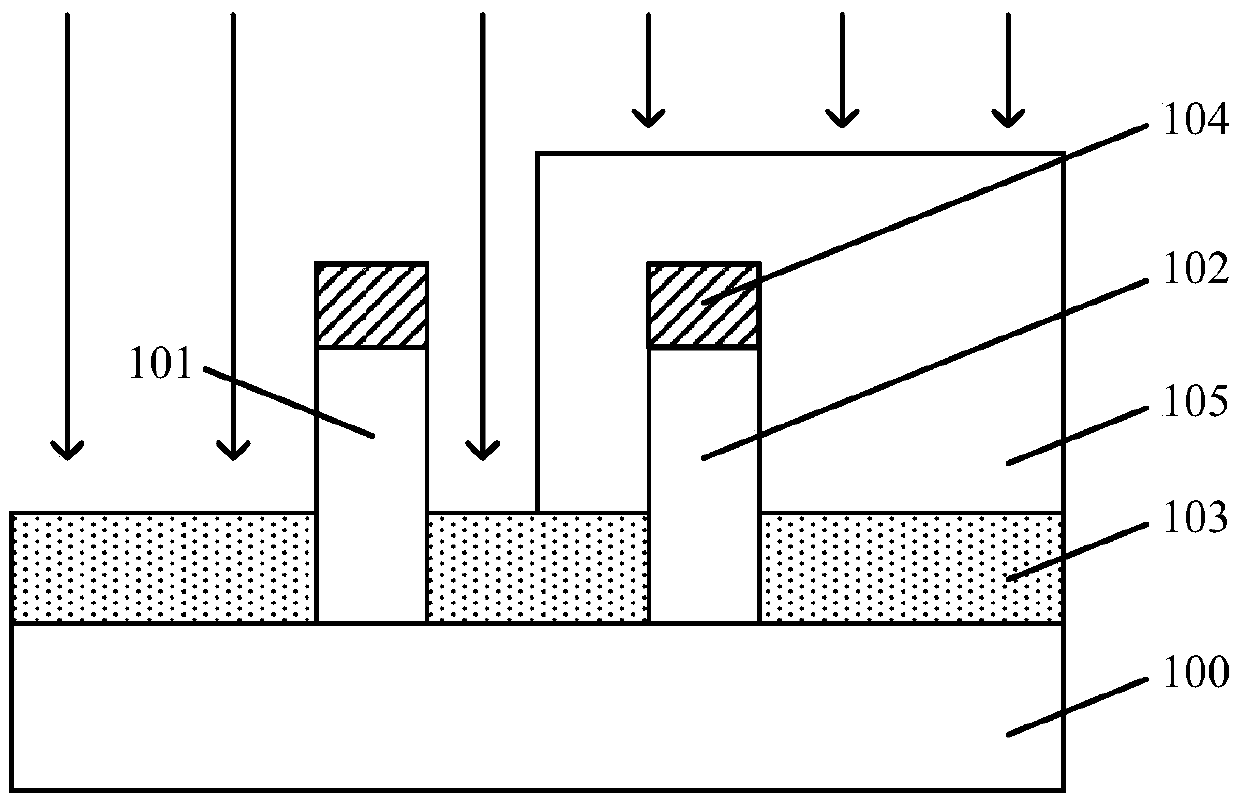

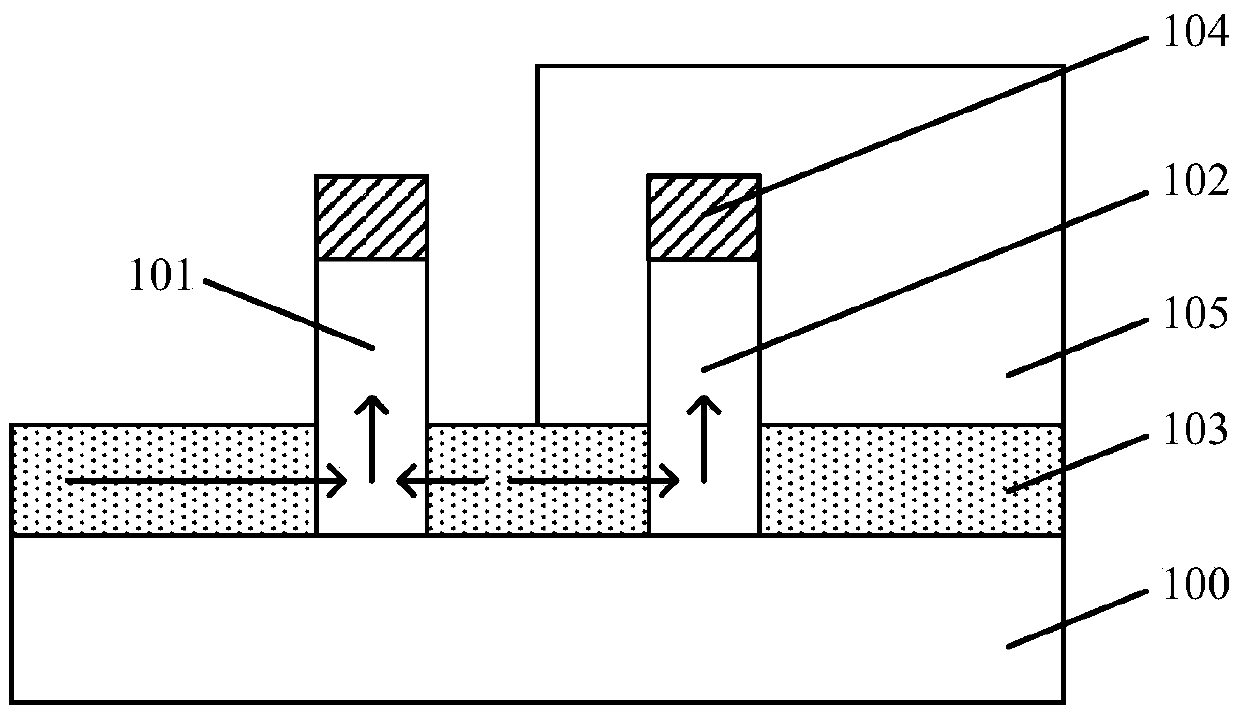

[0034] As mentioned in the background art, as the device density in the SRAM increases and the size shrinks, the performance and stability of the FinFET in the SRAM also decreases.

[0035] After research, it is found that as the size of the SRAM decreases and the component density increases, the size of the fin field effect transistor used to form the SRAM also decreases accordingly, and the fin size used to form the fin field effect transistor zoom out. While the size of the fin is reduced, the dopant ions formed in the source region and the drain region in the fin are more likely to diffuse to the bottom region of the fin, and the dopant ions are likely to be short-circuited at the bottom region of the fin, so that The bottom region of the fin causes a punch-through phenomenon, so that the bottom region of the fin easily generates leakage current. Wherein, the bottom area of the fin refers to the area from the position where the fin is flush with the surface of the diele...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More