Simulation Model and Simulation Method of Junction Field Effect Transistor

A technology of field effect transistors and simulation models, which is applied in special data processing applications, instruments, calculations, etc., and can solve problems that cannot meet the requirements of simulation accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

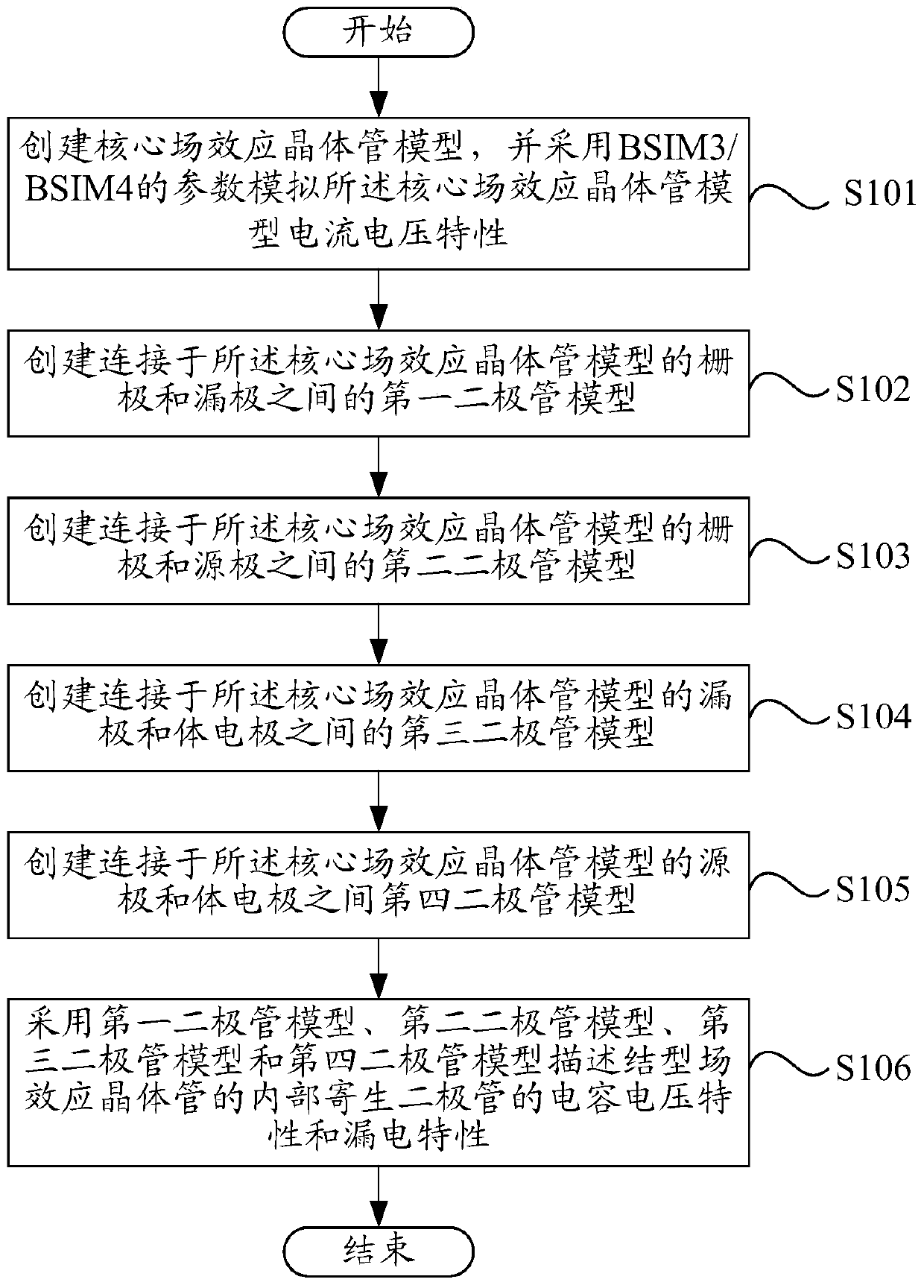

[0071] Further description will be given below in conjunction with the accompanying drawings and embodiments.

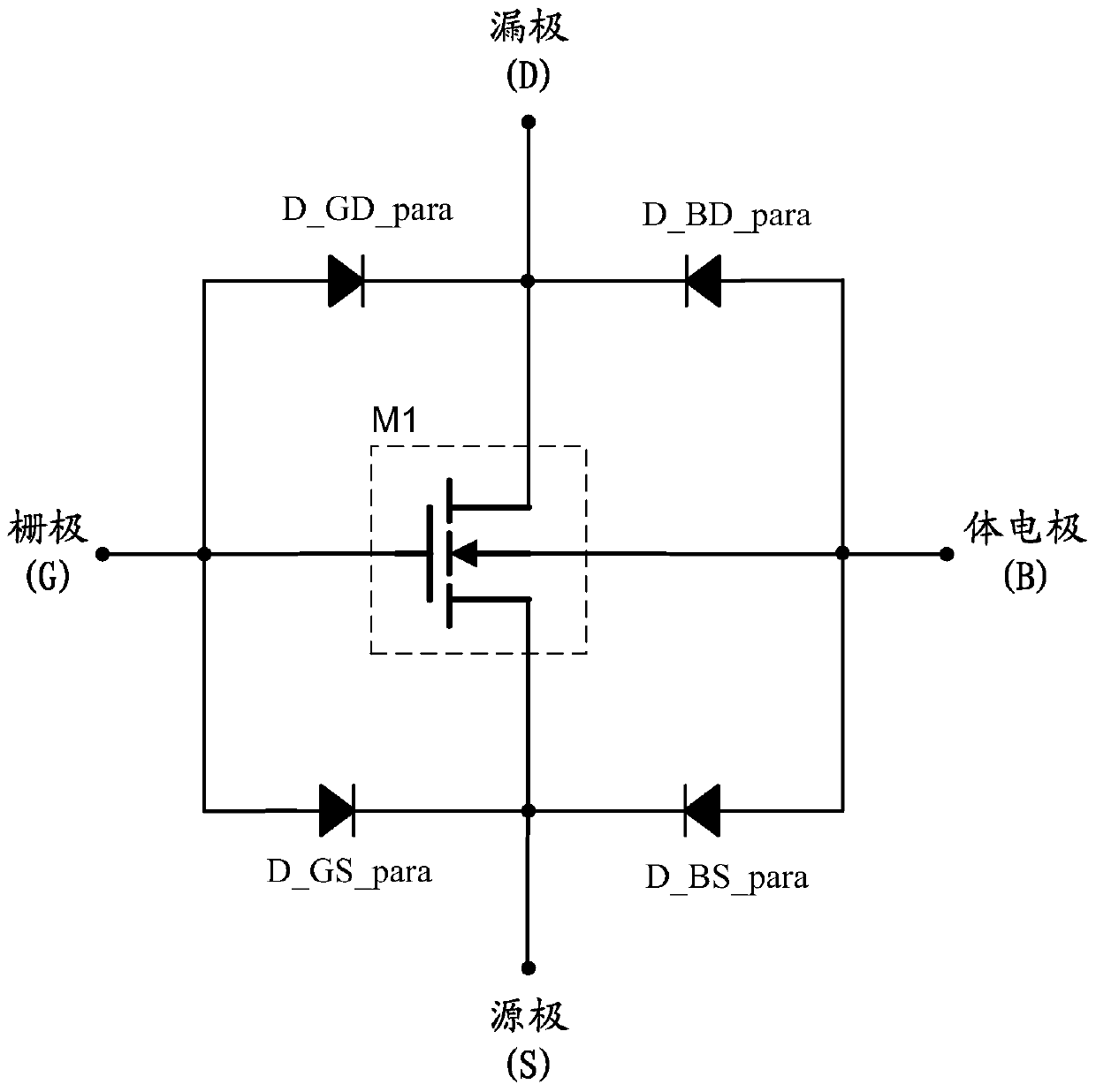

[0072] figure 1 It is the equivalent circuit structure of the simulation model of the junction field effect transistor of an embodiment. The simulation model of the junction field effect transistor includes a core field effect transistor model M1, a first diode model D_GD_para, a second diode model D_GS_para, a third diode model D_BD_para, and a fourth diode model D_BS_para.

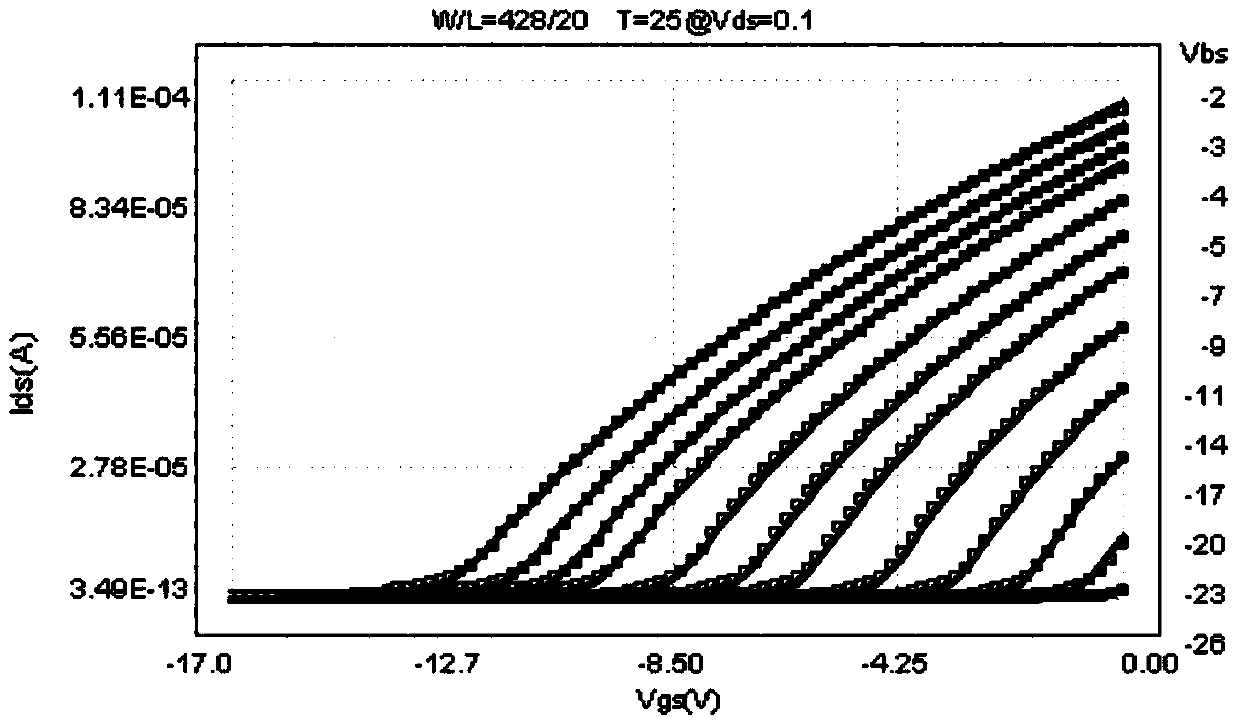

[0073]The current and voltage characteristics of the core field effect transistor model M1 are fitted using the parameters of BSIM3 / BSIM4. BSIM3 / BSIM4 is a circuit simulation standard developed by the University of California, Berkeley. Starting from the third generation of BSIM3, the simulation standard is based on the physical model, based on quasi-two-dimensional analysis, and solves the physical characteristics of the device when it is working. In order to improve the accuracy in specifi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More