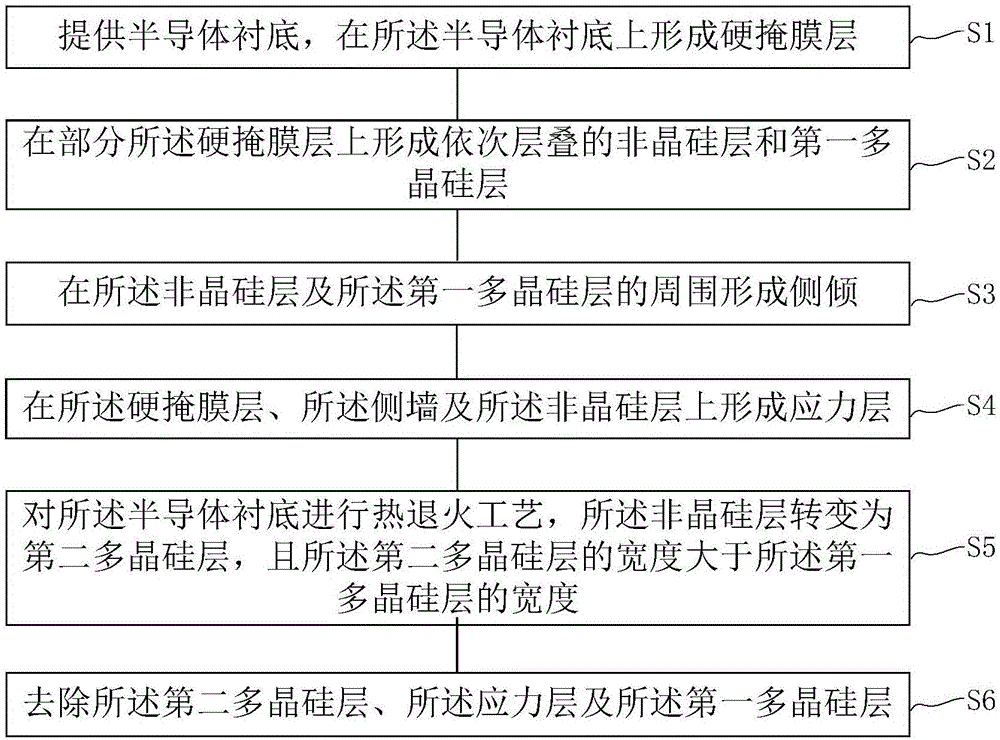

Multiple graphical mask preparation method

A multi-patterning and masking technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as sidewall differences on both sides of the sidewall, reduce shape differences, and optimize the etching process Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

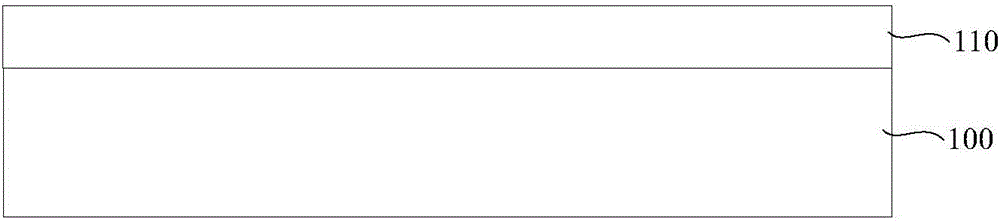

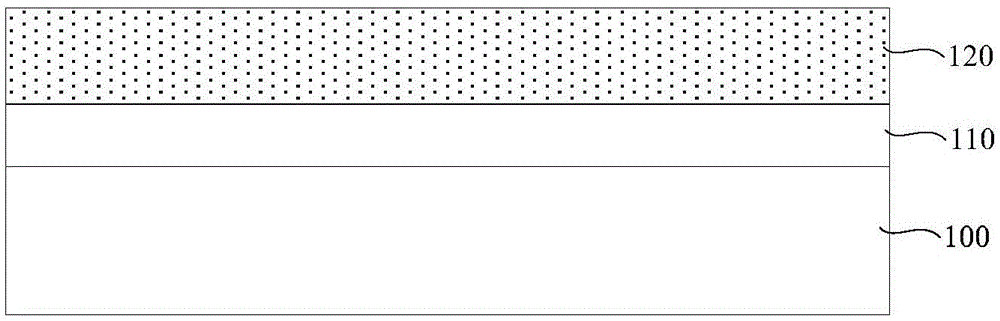

[0036] The preparation method of the multi-patterned mask process of the present invention will be described in more detail below in conjunction with the schematic diagram, wherein a preferred embodiment of the present invention is represented, it should be understood that those skilled in the art can modify the present invention described here, and still realize Advantageous effects of the present invention. Therefore, the following description should be understood as the broad knowledge of those skilled in the art, but not as a limitation of the present invention.

[0037] In the interest of clarity, not all features of an actual implementation are described. In the following description, well-known functions and constructions are not described in detail since they would obscure the invention with unnecessary detail. It should be appreciated that in the development of any actual embodiment, numerous implementation details must be worked out to achieve the developer's specif...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More