Patents

Literature

46results about How to "Optimizing the etch process" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

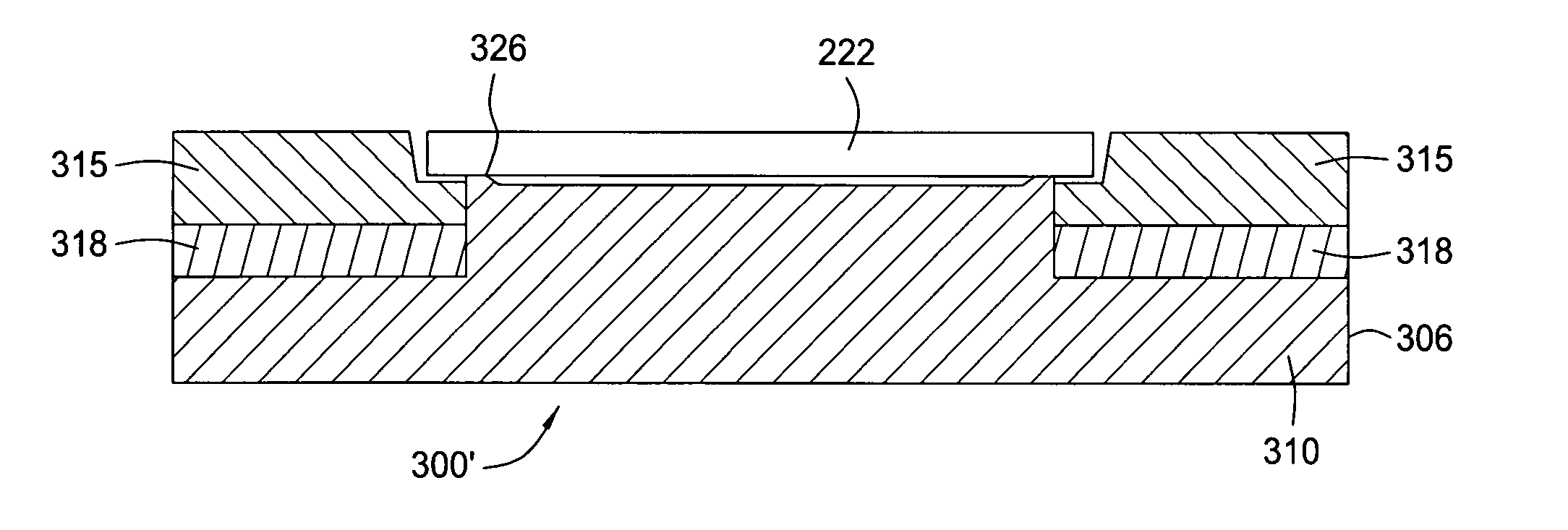

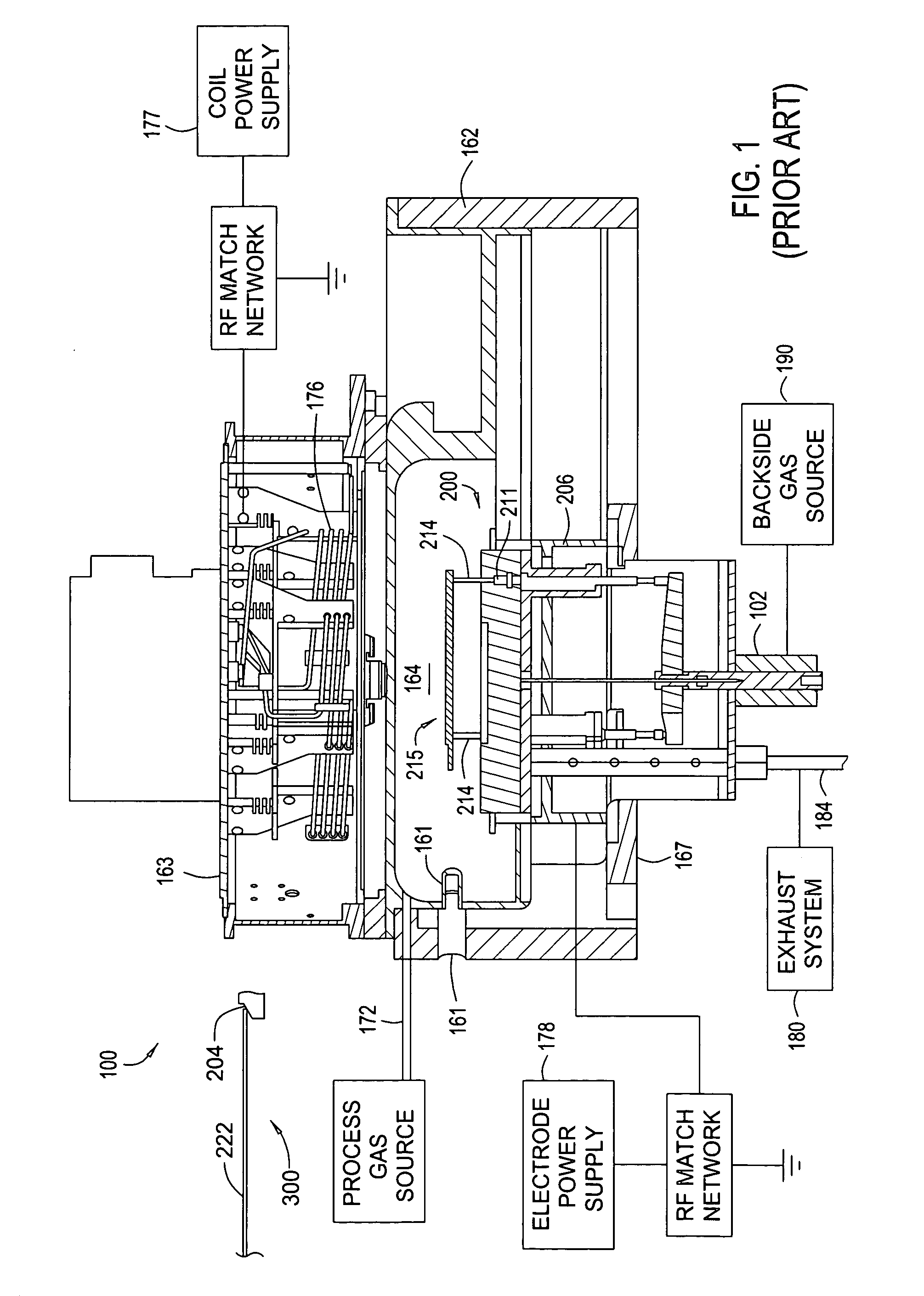

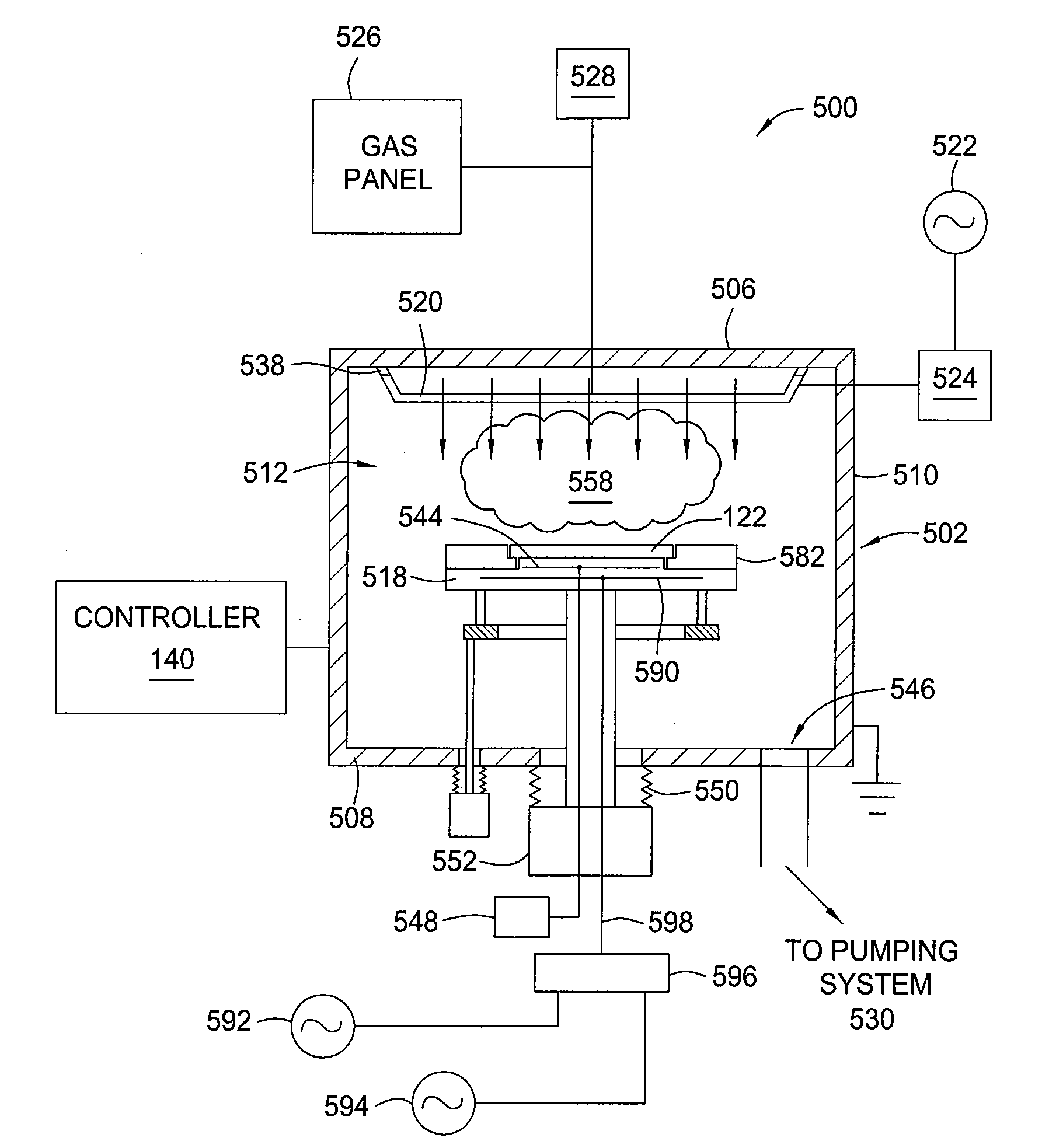

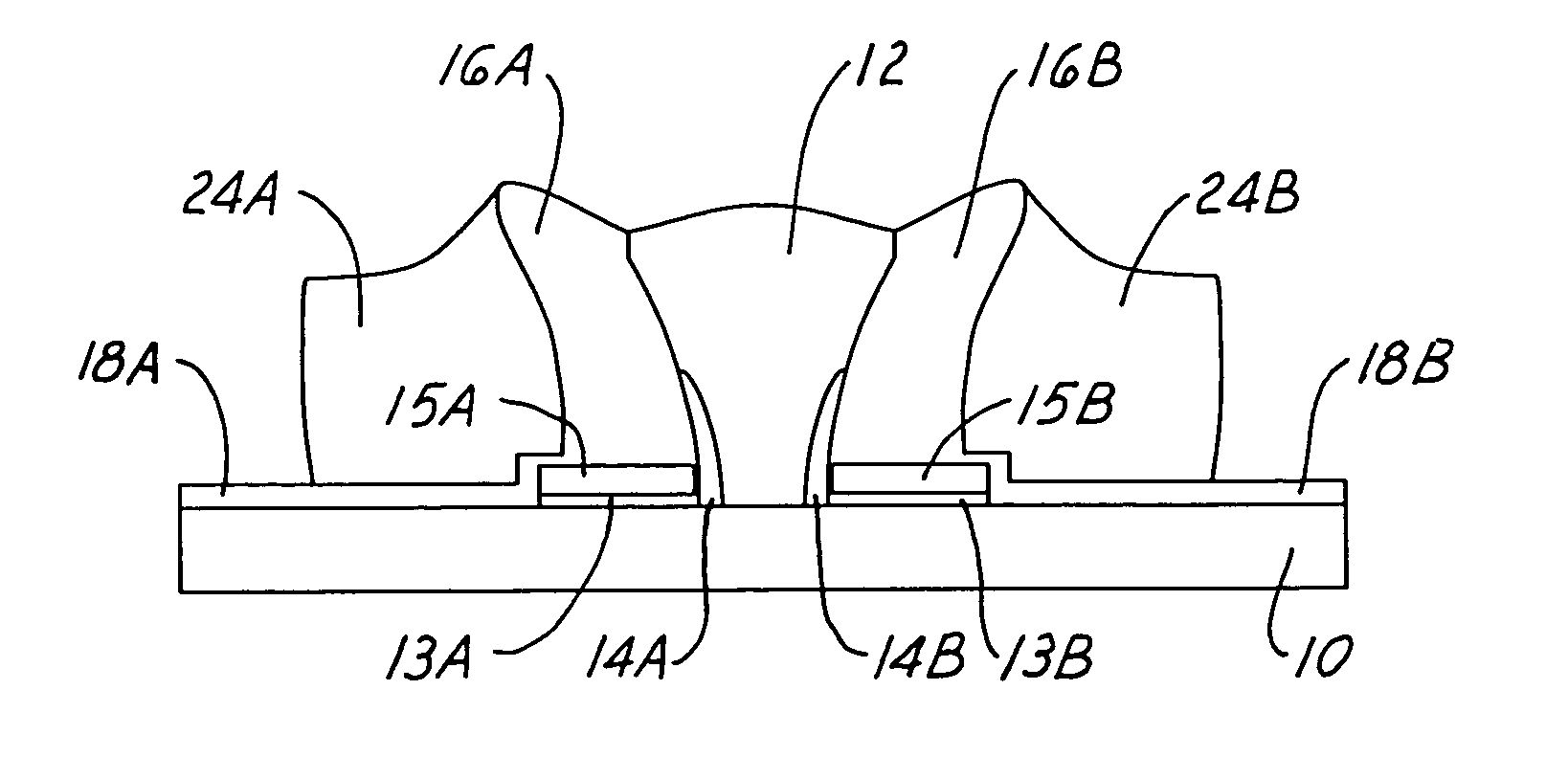

Tuned potential pedestal for mask etch processing apparatus

InactiveUS20050133166A1Great RF powerEnhancing plasma etching processElectric discharge tubesSemiconductor/solid-state device manufacturingEngineeringReticle

The present invention generally provides an improved pedestal for supporting a substrate. The pedestal has greatest application during a plasma etching process, such as for a quartz photomask, or “reticle.” The pedestal defines a body, and a substrate support base along an upper surface of the body. The substrate support base has an outer edge, and an intermediate substrate support ridge for receiving and supporting the substrate. At least a portion of the substrate support base outside of the intermediate substrate support ridge is fabricated from a dielectric material. The purpose is to couple greater RF power through the reticle in order to enhance the plasma etching process.

Owner:APPLIED MATERIALS INC

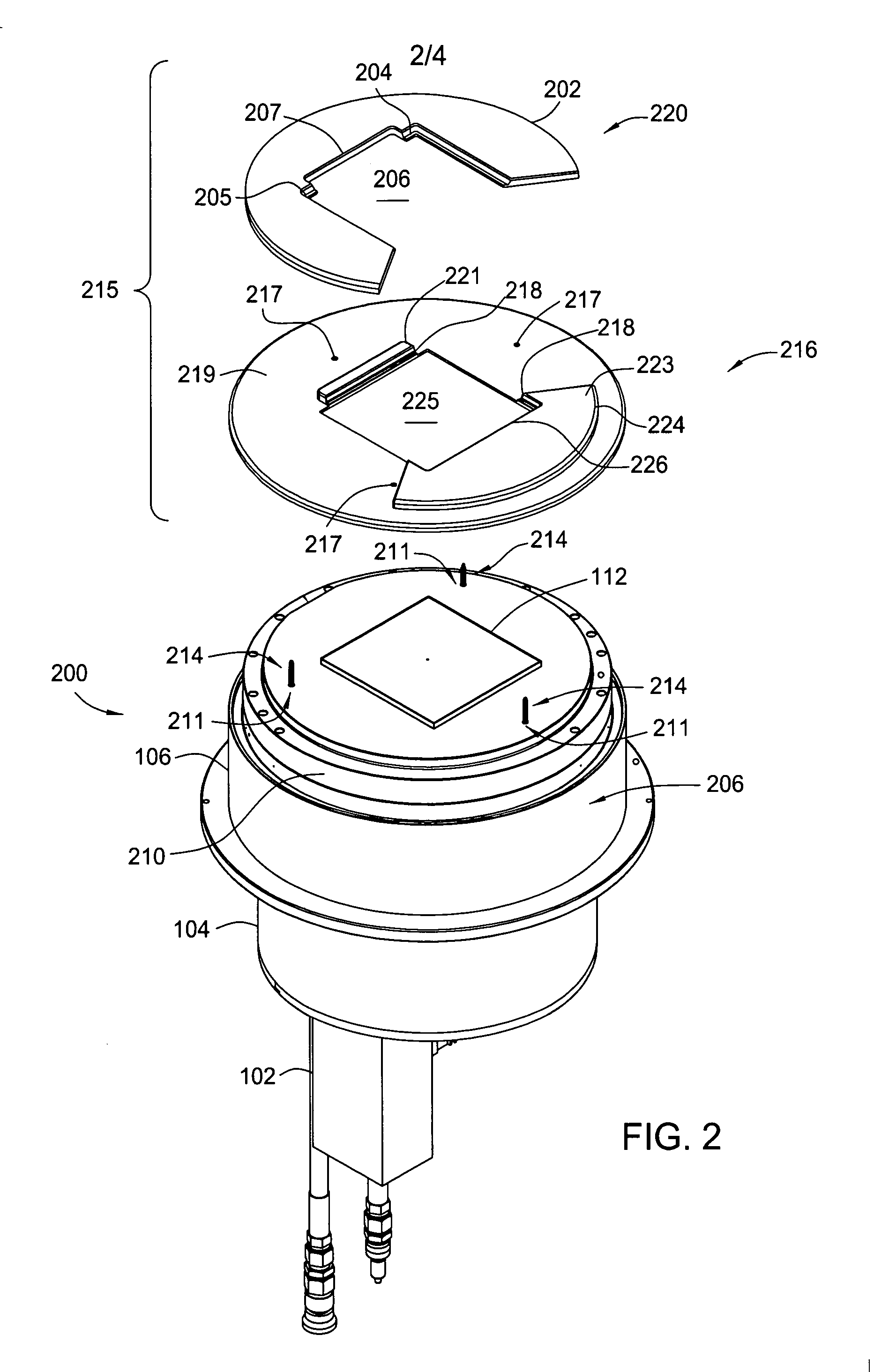

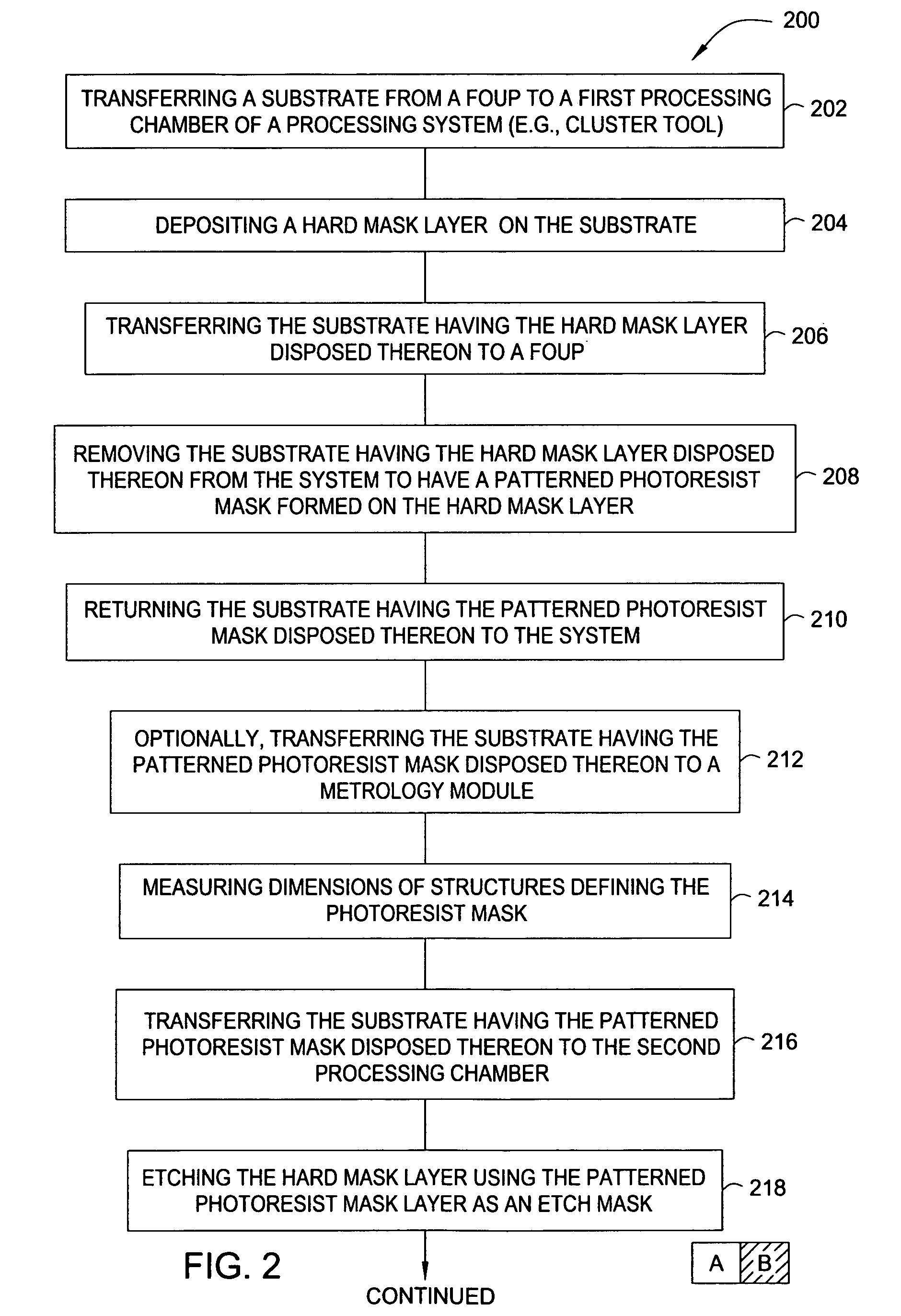

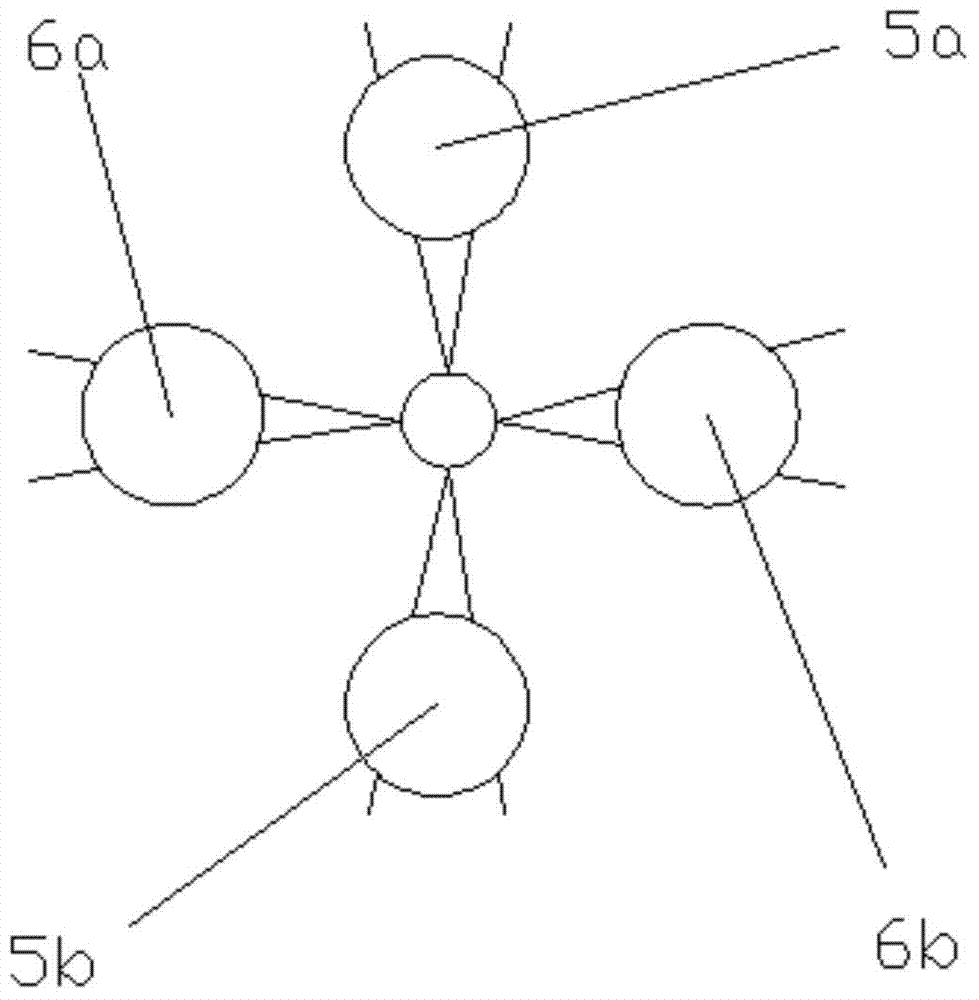

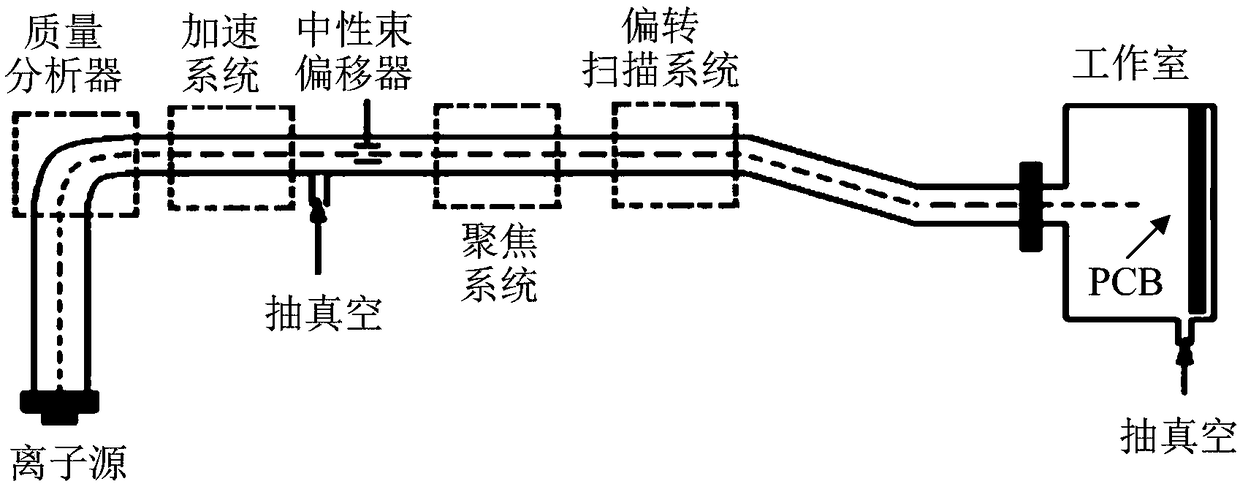

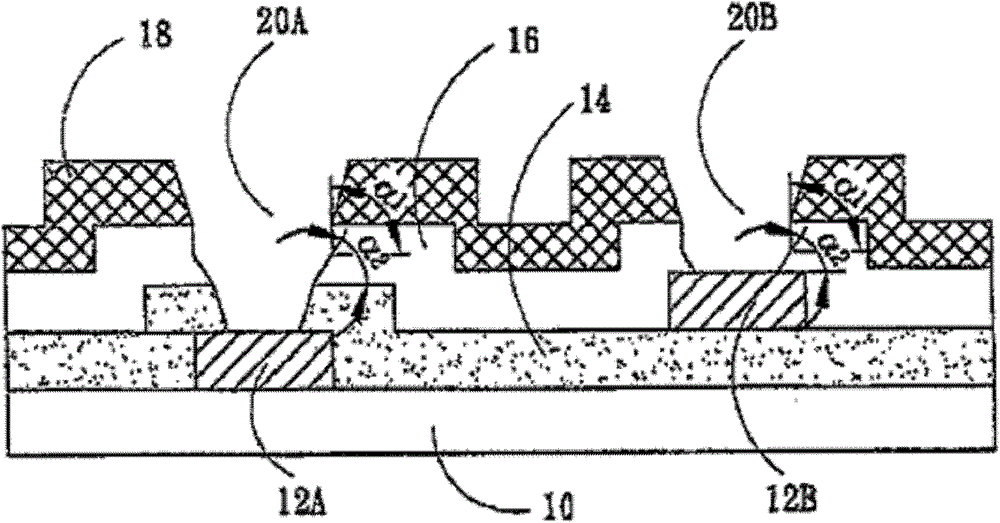

Cluster tool and method for process integration in manufacturing of a photomask

InactiveUS20070026321A1Improve photomask fabricationMinimal financial investmentDecorative surface effectsPhotomechanical apparatusResistProcess integration

A method and apparatus for process integration in manufacture of a photomask are disclosed. In one embodiment, a cluster tool suitable for process integration in manufacture of a photomask including a vacuum transfer chamber having coupled thereto at least one hard mask deposition chamber and at least one plasma chamber configured for etching chromium. In another embodiment, a method for process integration in manufacture of a photomask includes depositing a hard mask on a substrate in a first processing chamber, depositing a resist layer on the substrate, patterning the resist layer, etching the hard mask through apertures formed in the patterned resist layer in a second chamber; and etching a chromium layer through apertures formed in the hard mask in a third chamber.

Owner:APPLIED MATERIALS INC

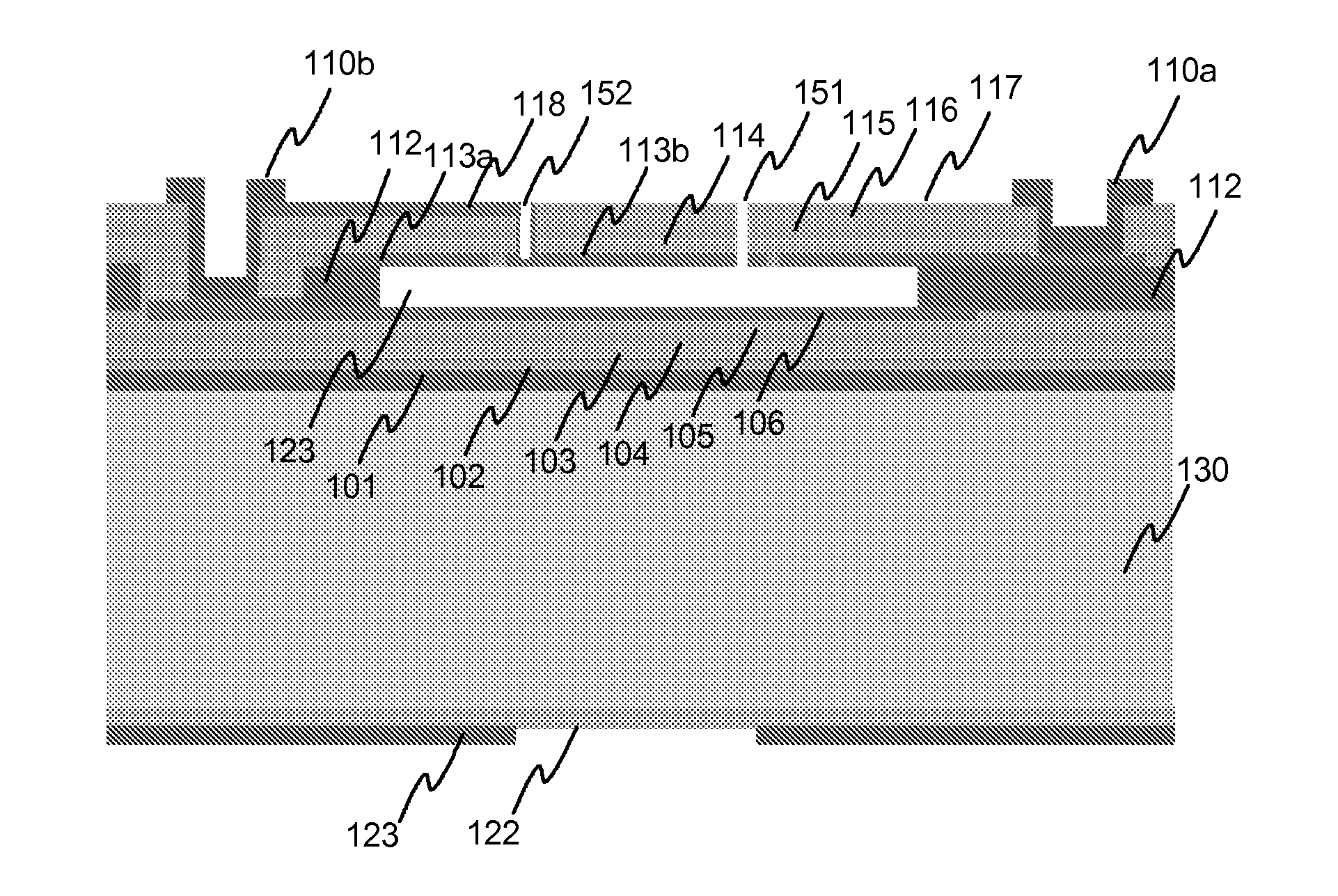

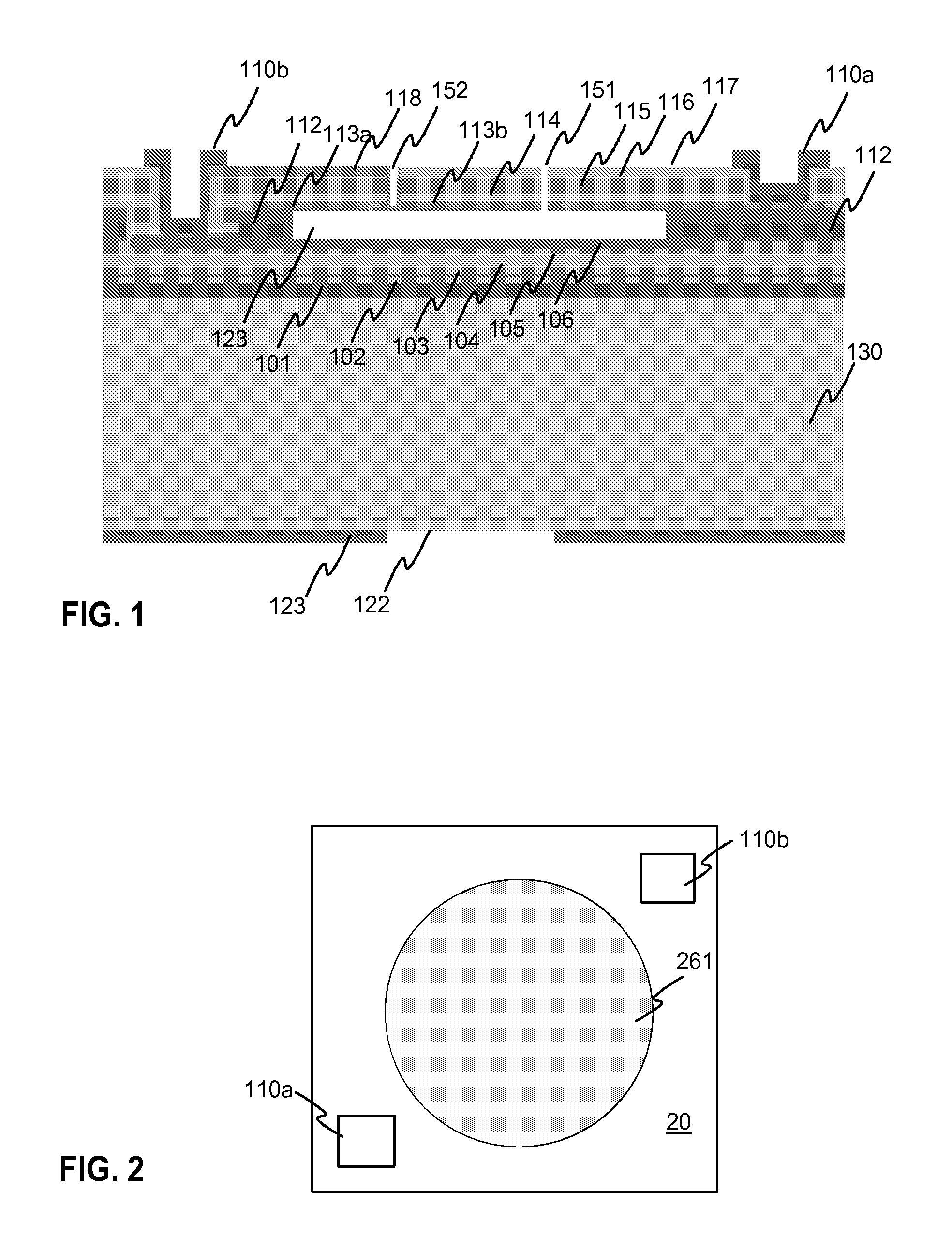

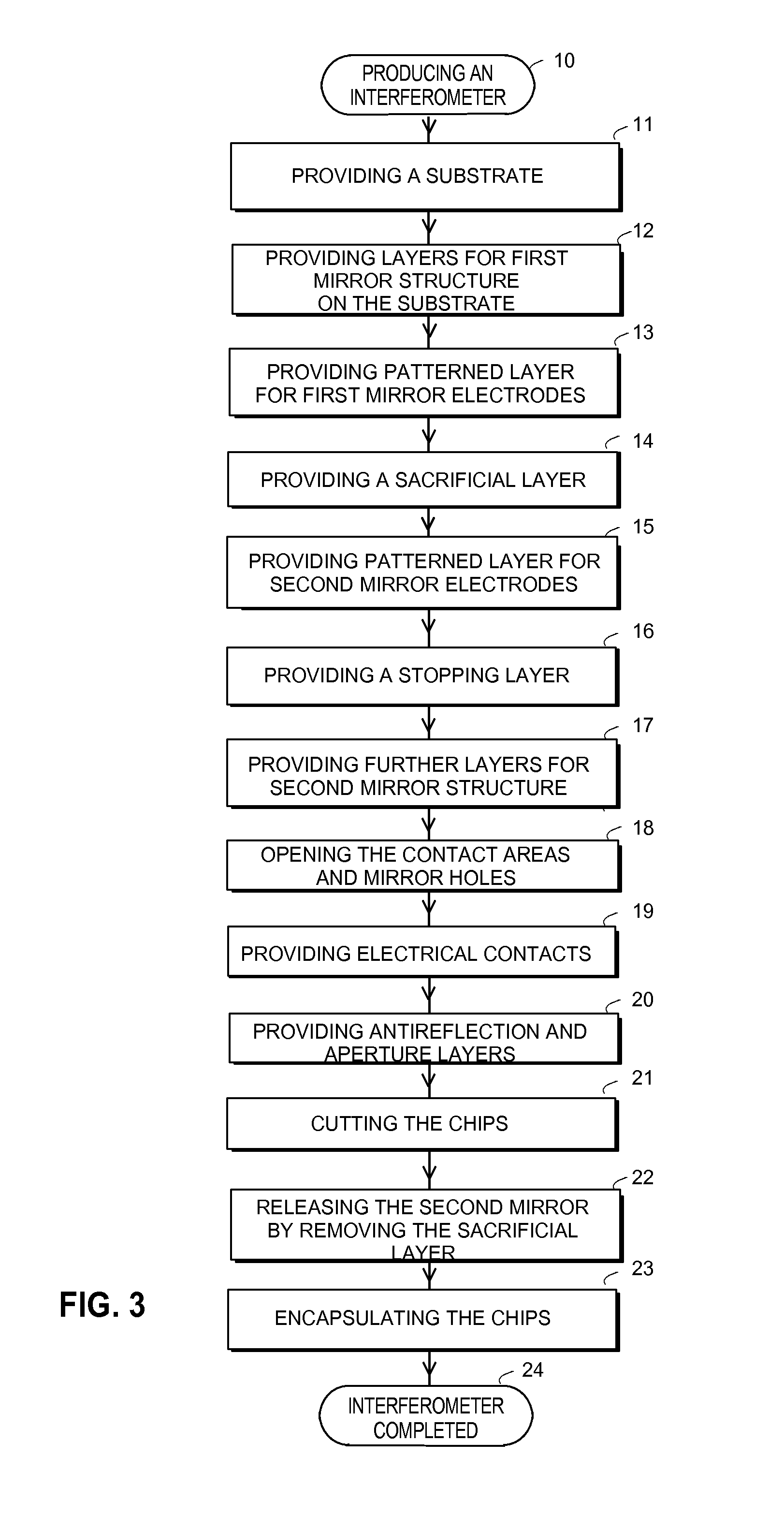

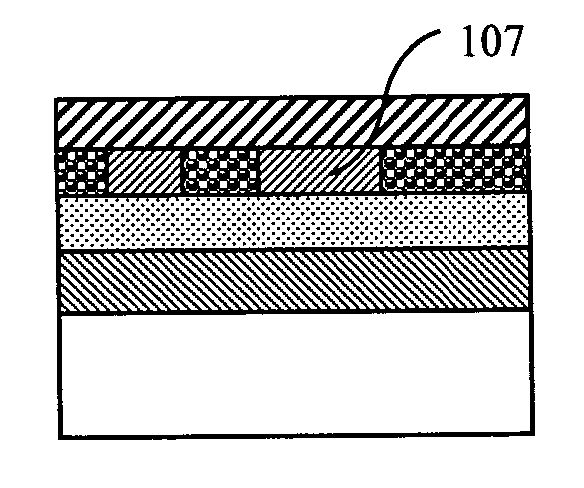

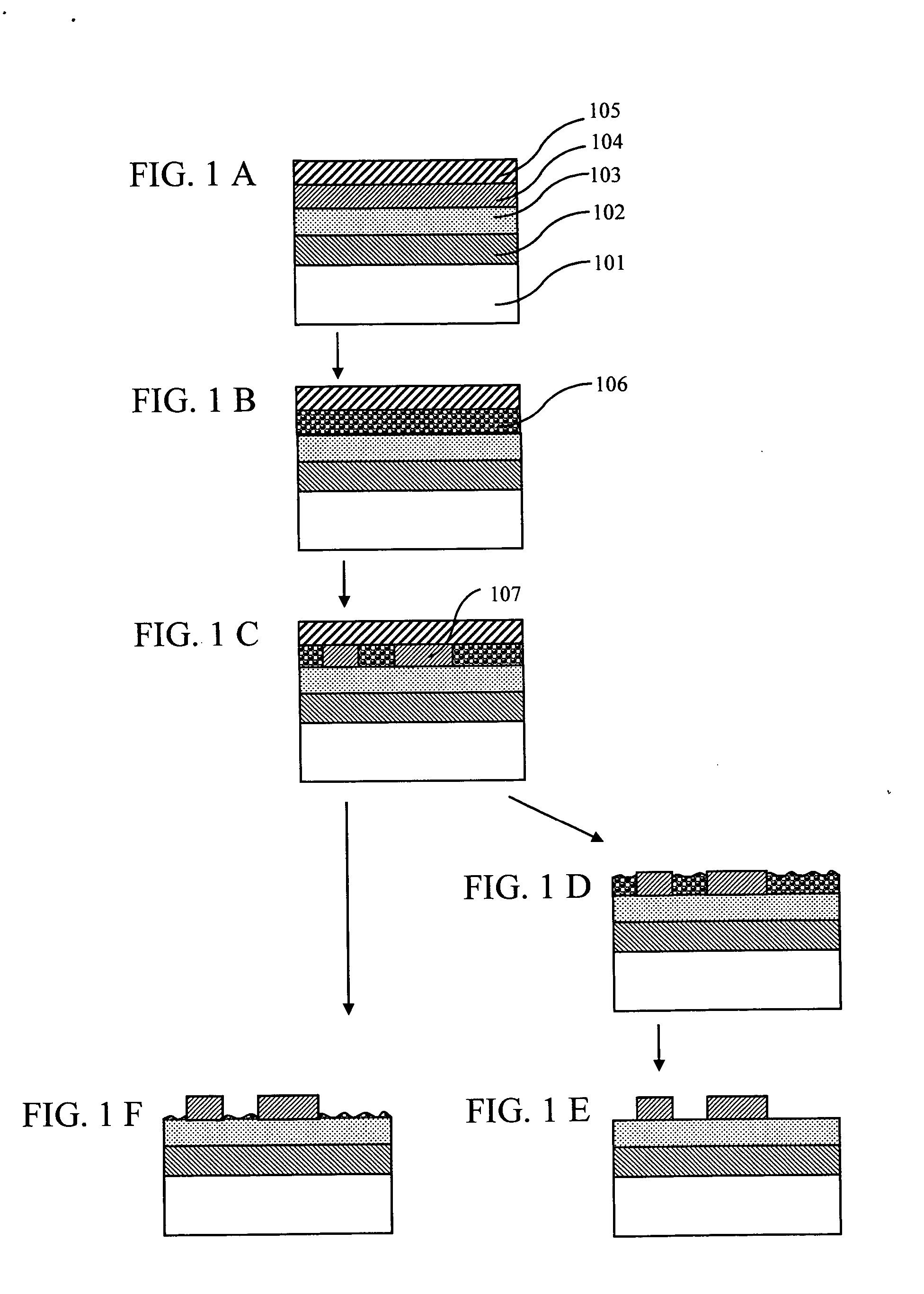

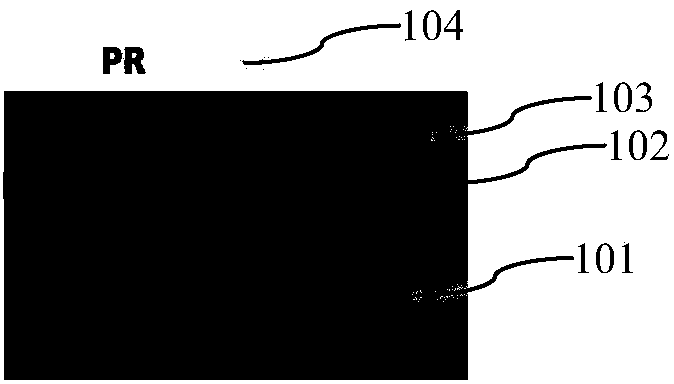

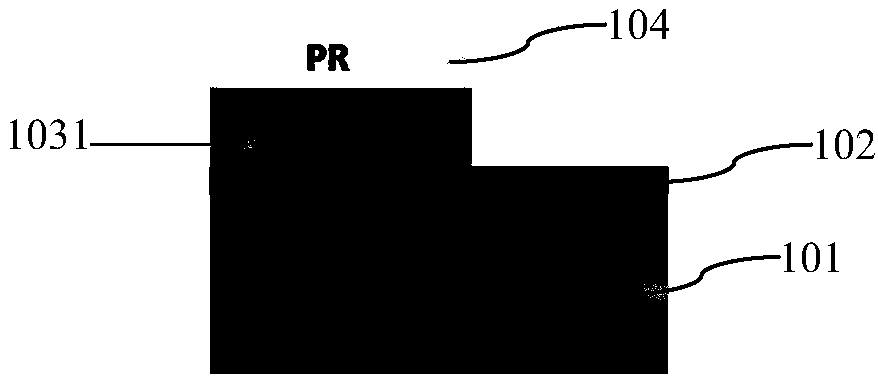

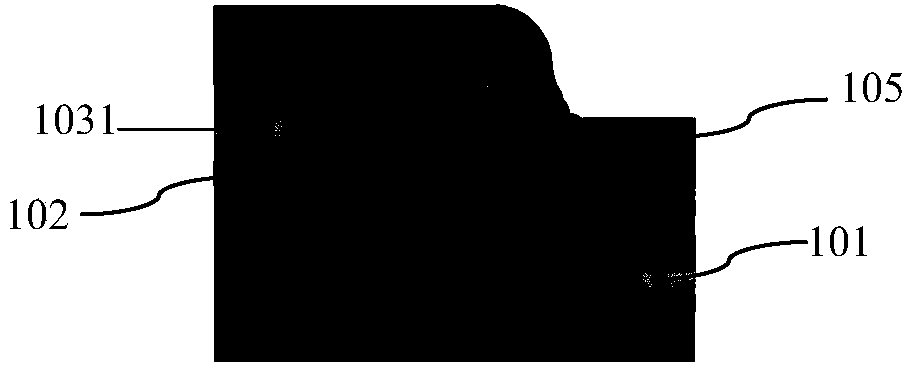

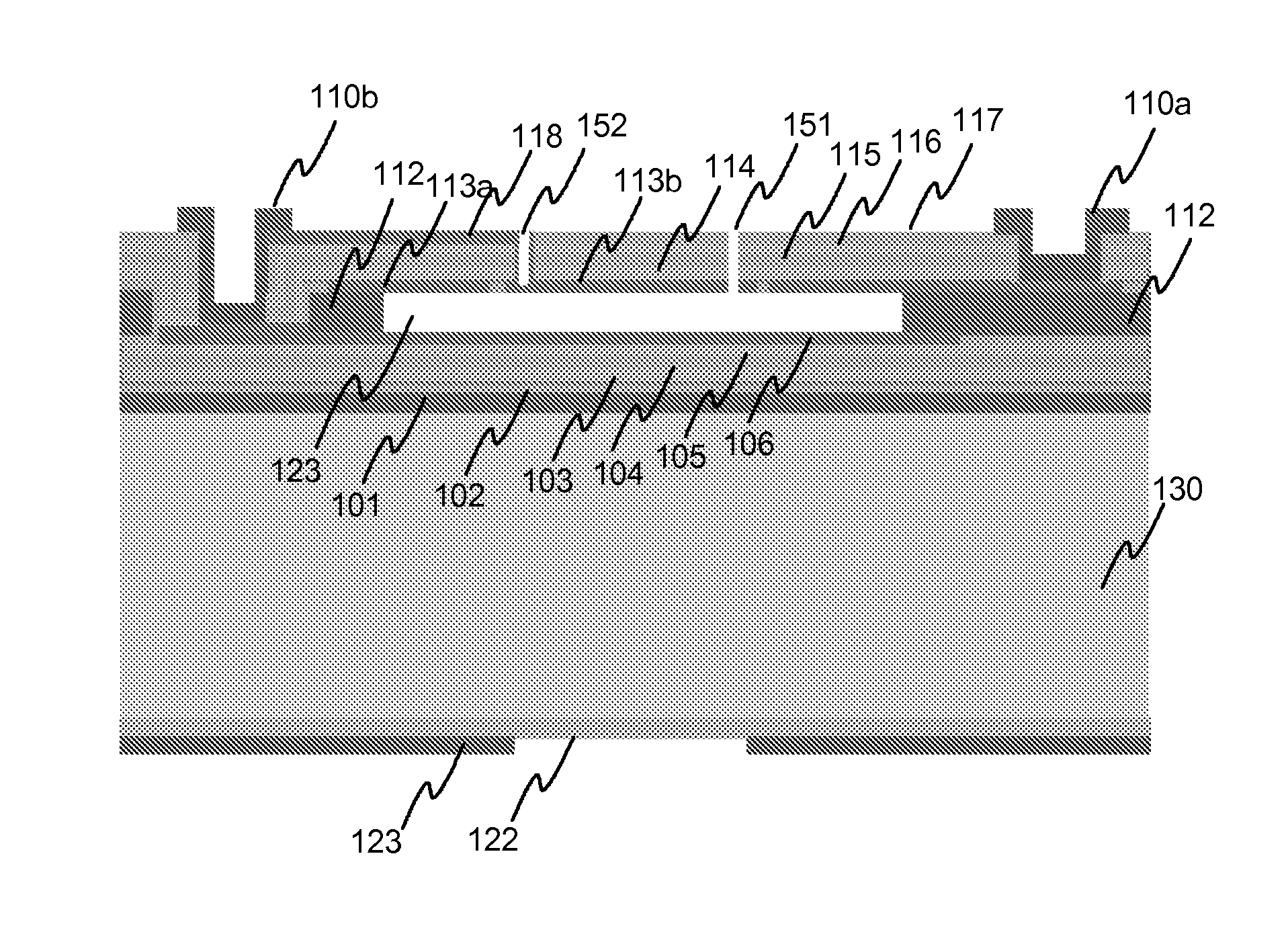

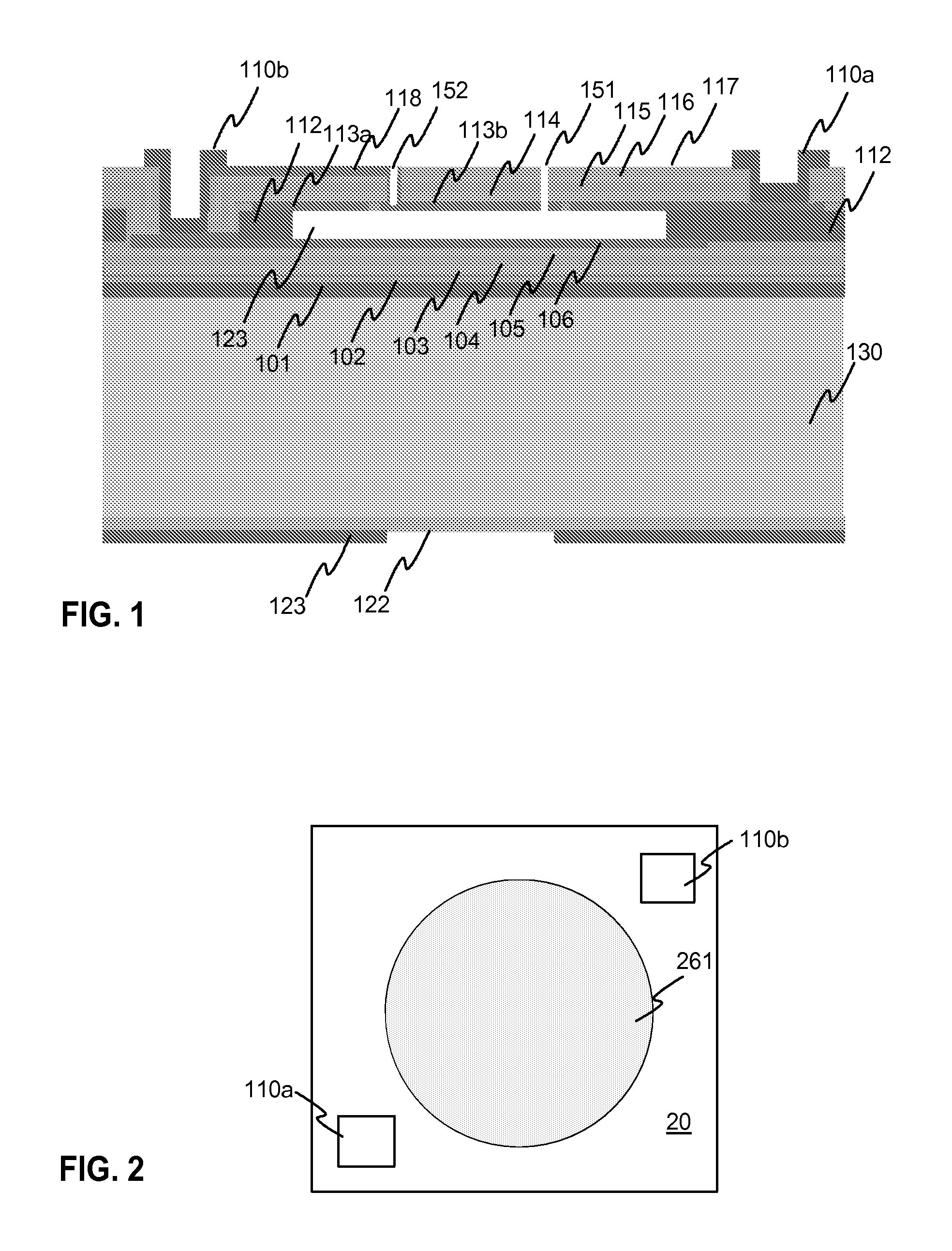

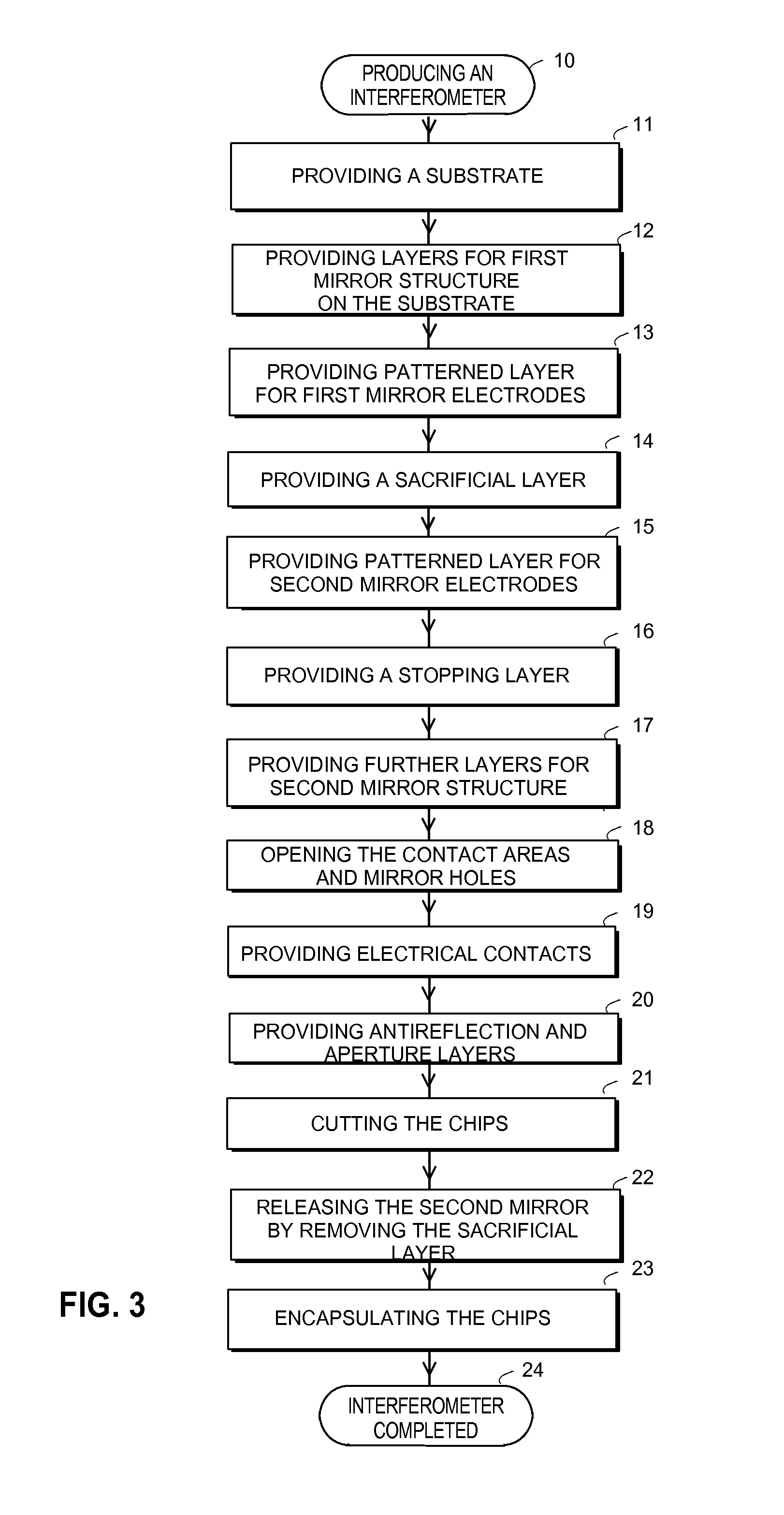

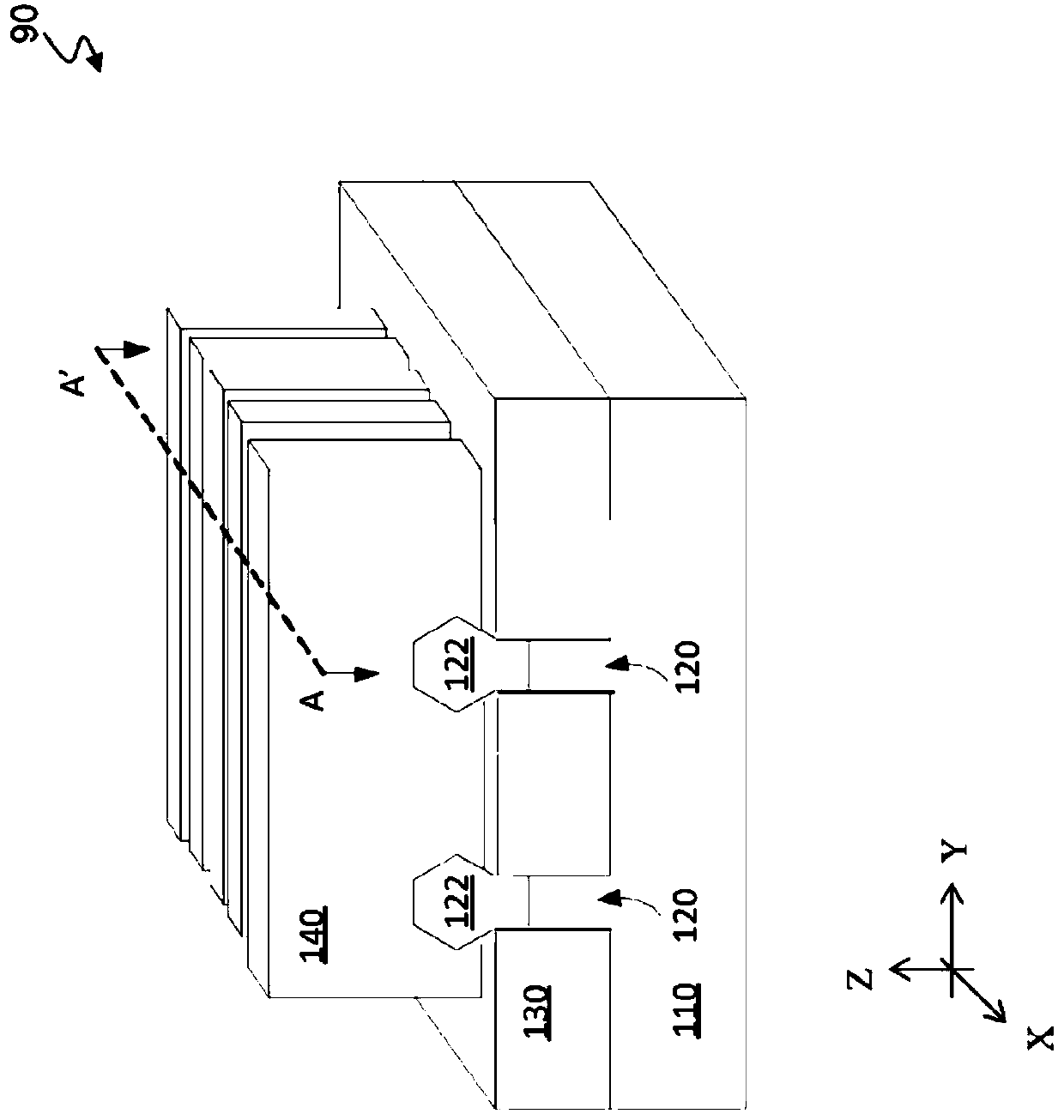

Micromechanical tunable fabry-perot interferometer, an intermediate product, and a method for producing the same

ActiveUS20120050751A1Reduce and avoid useHigh densitySemiconductor/solid-state device manufacturingSpectrum generation using multiple reflectionEtchingSilicon oxide

The invention relates to controllable Fabry-Perot interferometers which are produced with micromechanical (MEMS) technology. Producing prior art interferometers includes a risk of deterioration of mirrors during the etching of the sacrificial layer (123). According to the solution according to the invention at least one layer (103, 105, 114, 116) of the mirrors is made of silicon-rich silicon nitride. In the inventive Fabry-Perot interferometer it is possible to avoid or reduce using silicon oxide in the mirror layers whereby the risk of deterioration of the mirrors is reduced. It is also possible to use mirror surfaces with higher roughness, whereby the risk of the mirrors sticking to each other is reduced.

Owner:TEKNOLOGIAN TUTKIMUSKESKUS VTT

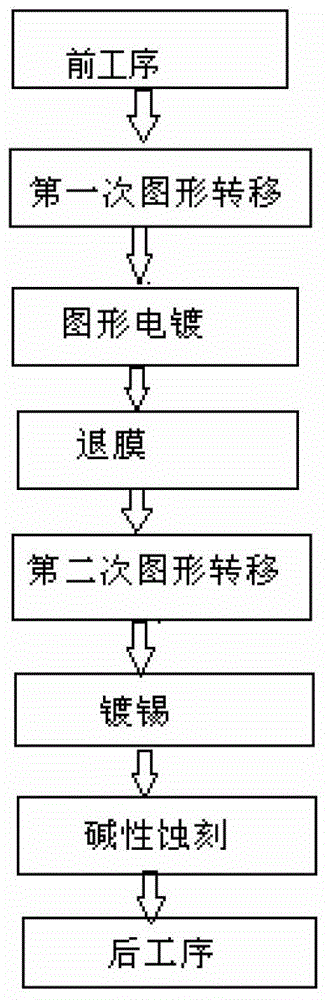

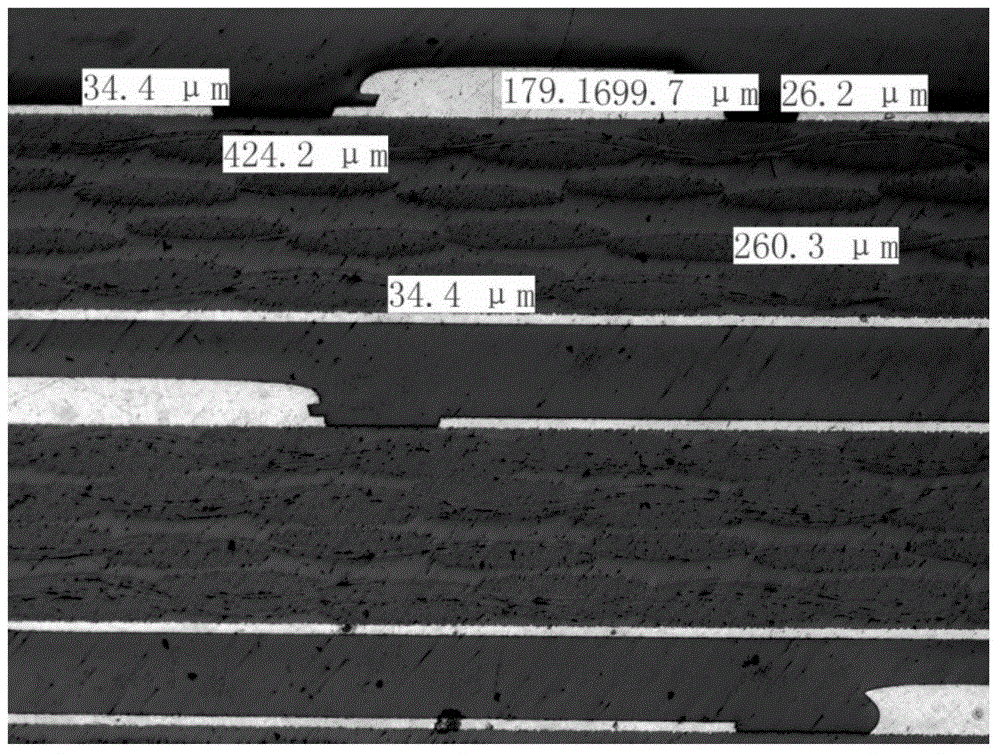

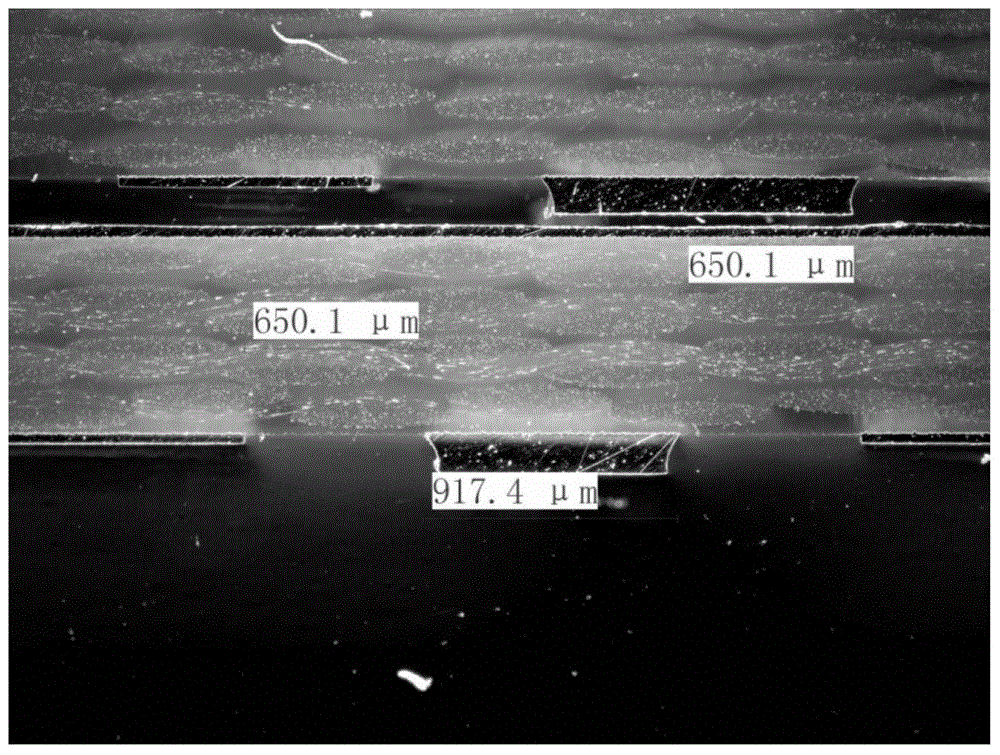

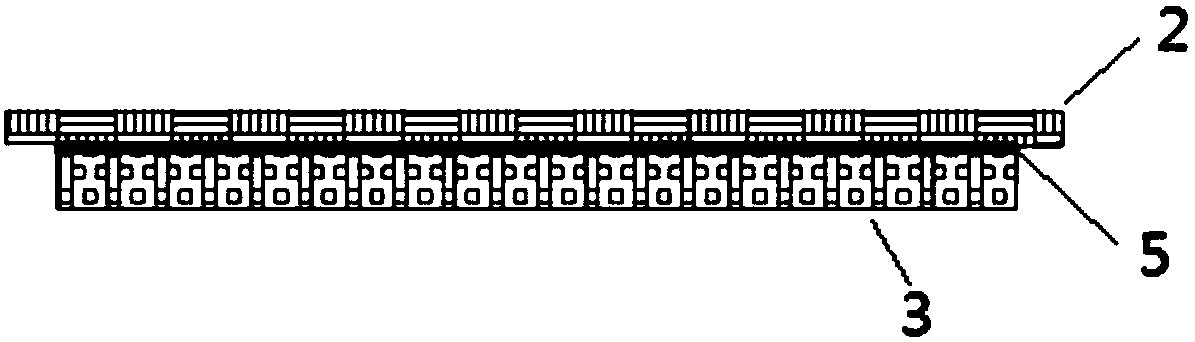

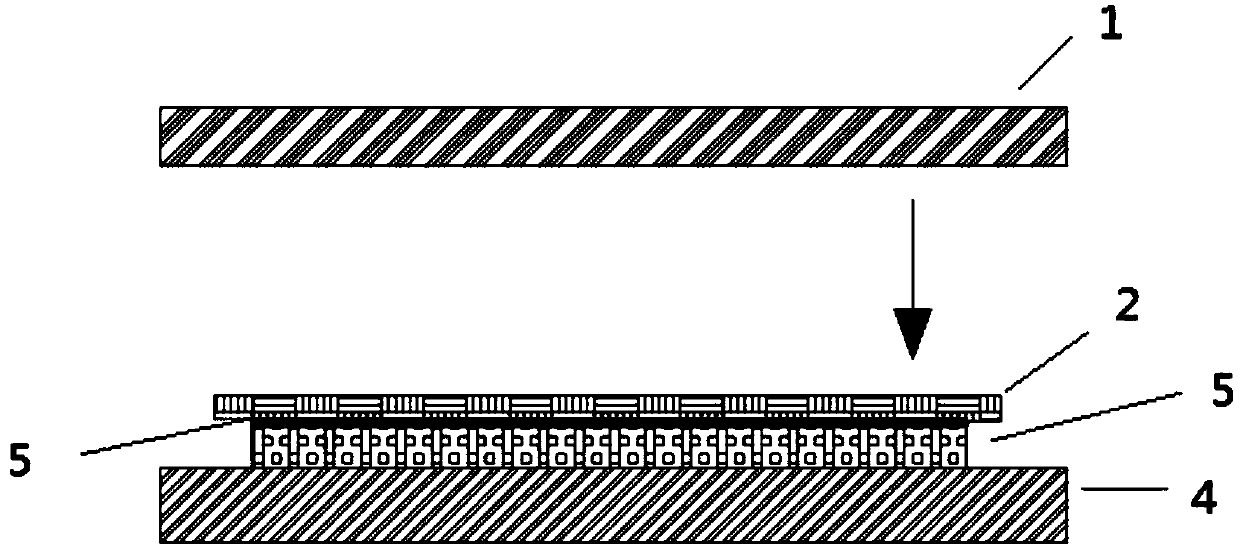

Heavy-copper step circuit board and preparation method thereof

ActiveCN103338595AOptimize grinding plateOptimizing the etch processConductive material chemical/electrolytical removalTinningAlkaline etching

The invention discloses a heavy-copper step circuit board and a preparation method thereof. The preparation method comprises the working procedures of primary pattern transfer, pattern electroplating, film removal, secondary pattern transfer, tinning and alkaline etching. The preparation method solves the quality problem of a clamping film and the quality problems such as circuit nicks and unclean etching due to the fact that an anti-corrosion layer cannot be closely bonded with a circuit by a dry film technology by utilizing the production capacity of the available equipment and optimizing roll film, board grinding and etching processes; the whole preparation process is compatible with the traditional circuit board technology; and the quality and the cost can be compatible effectively.

Owner:KALEX MULTI LAYER CIRCUIT BOARD (ZHONGSHAN) CO LTD

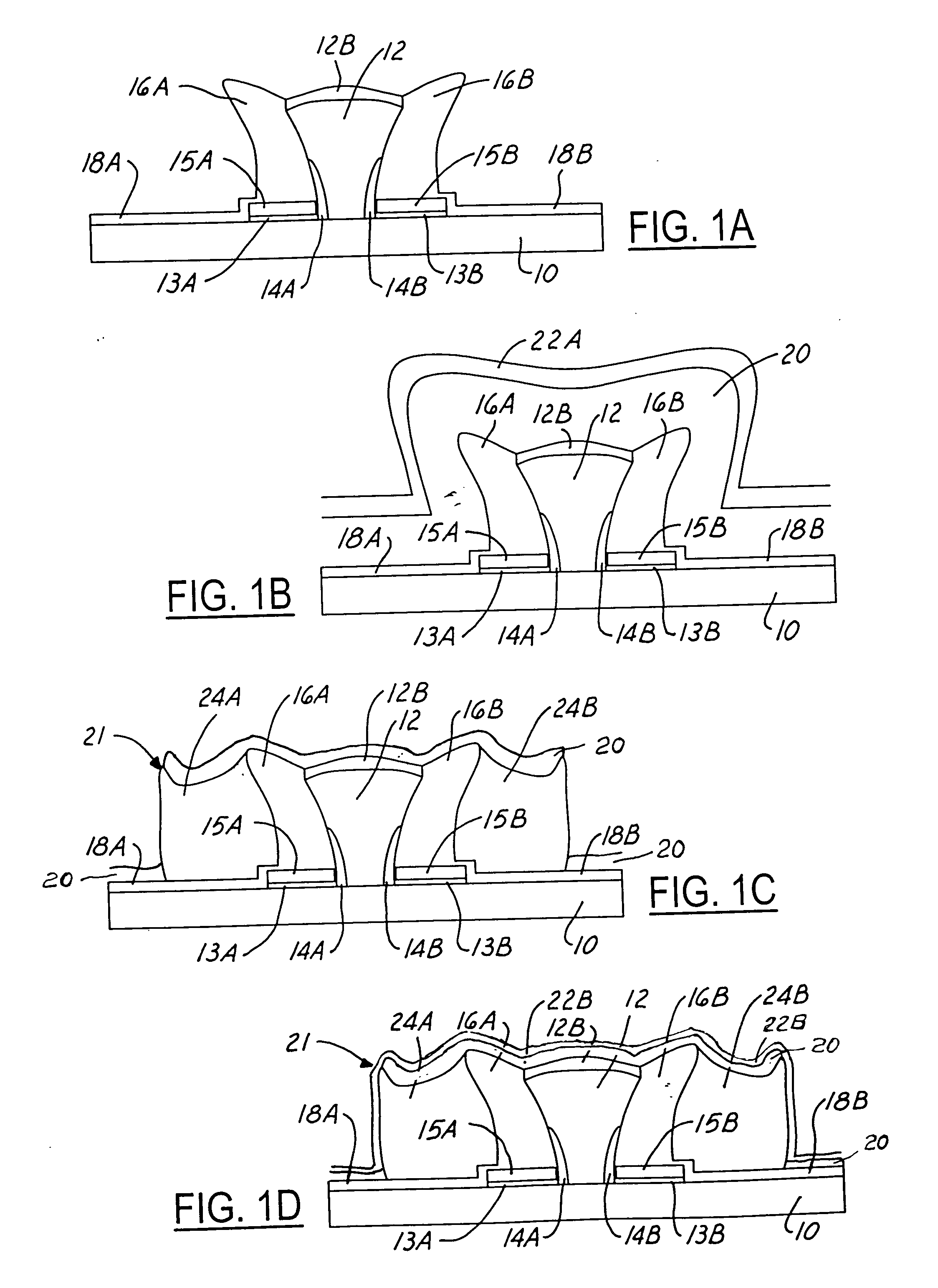

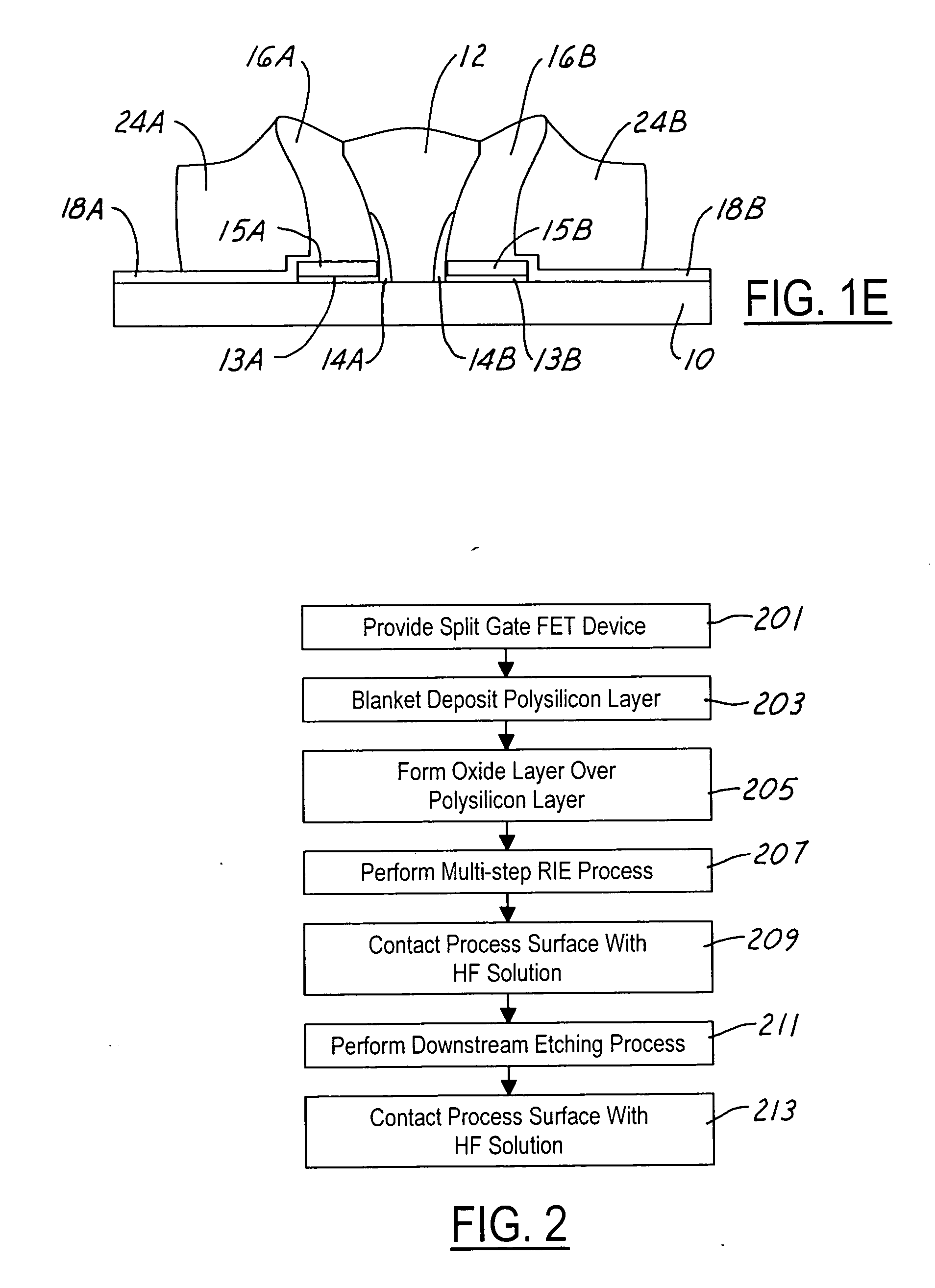

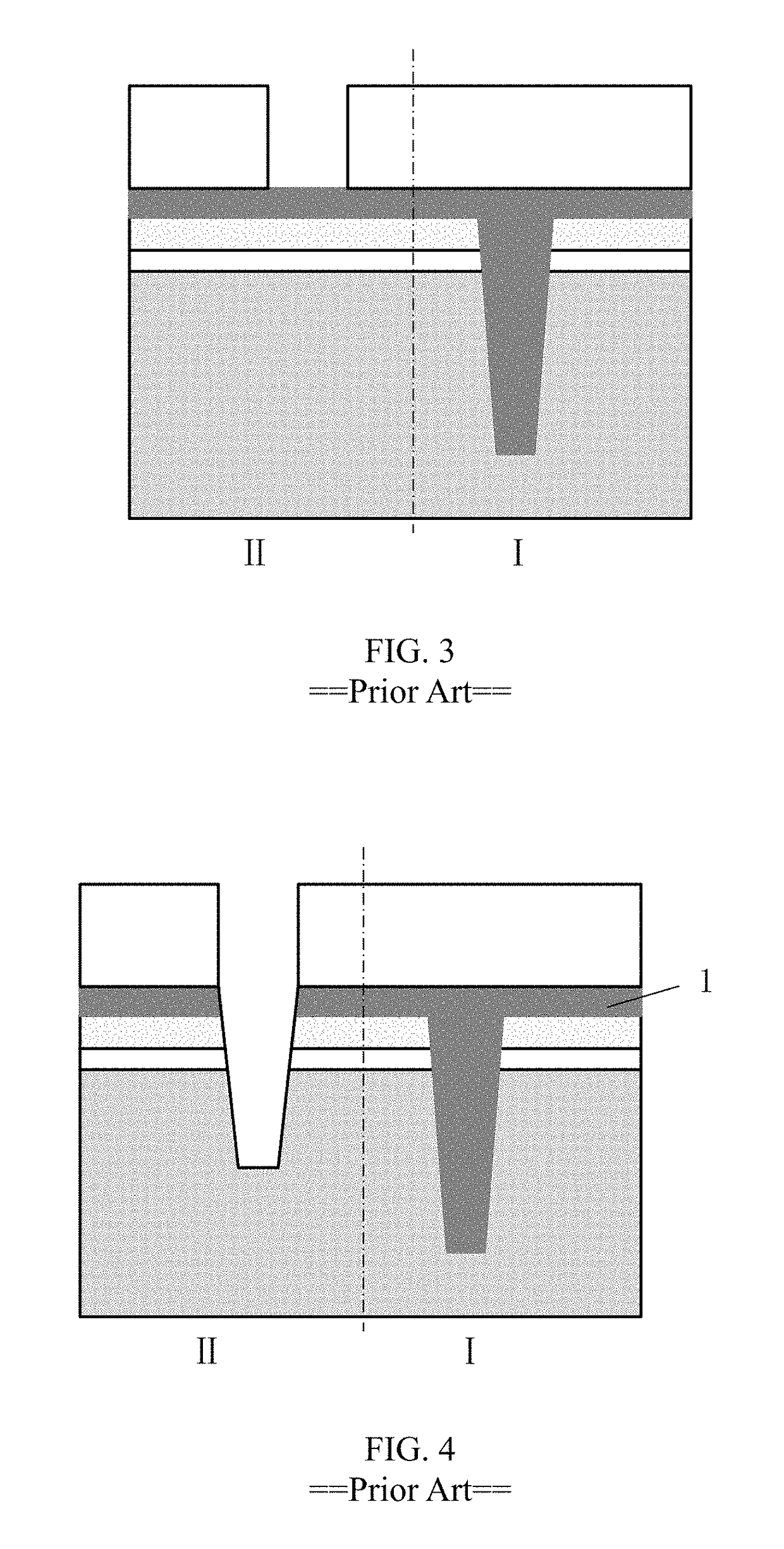

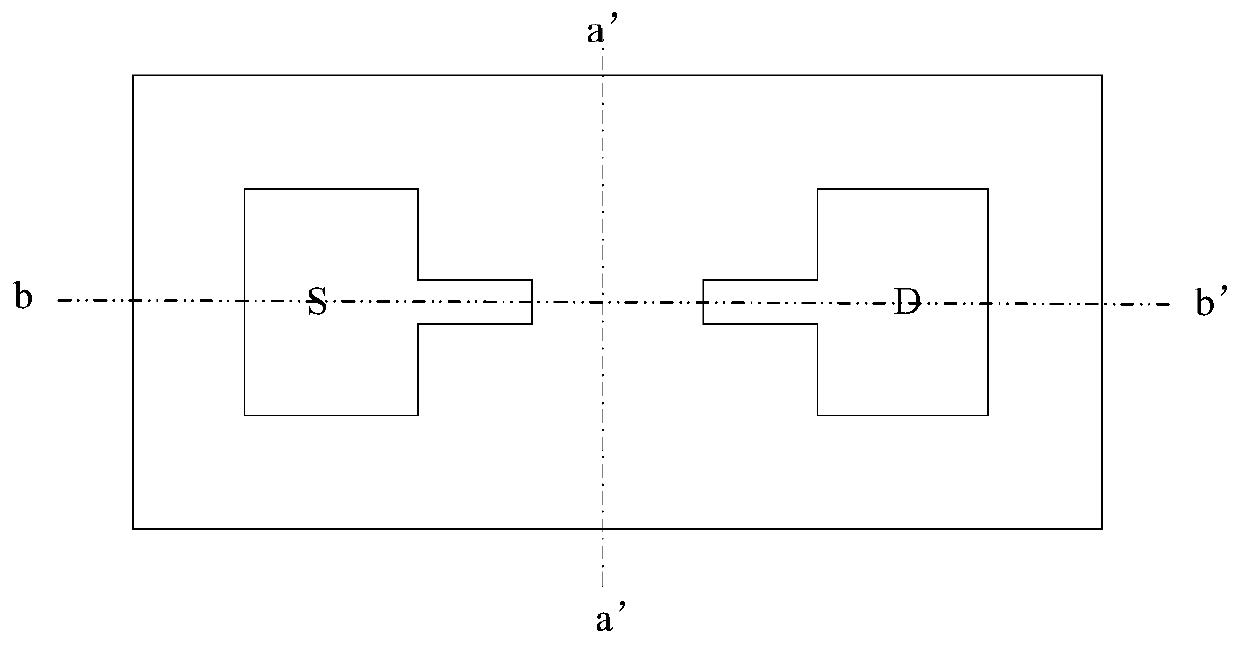

Etching method for forming a square cornered polysilicon wordline electrode

InactiveUS20050079672A1Optimizing the etch processSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringReactive-ion etching

A split gate FET wordline electrode structure and method for forming the same including an improved polysilicon etching process including providing a semiconductor wafer process surface comprising first exposed polysilicon portions and adjacent oxide portions; forming a first oxide layer on the exposed polysilicon portions; blanket depositing a polysilicon layer on the first exposed polysilicon portions and adjacent oxide portions; forming a hardmask layer on the polysilicon layer; carrying out a multi-step reactive ion etching (RIE) process to etch through the hardmask layer and etch through a thickness portion of the polysilicon layer to form second polysilicon portions adjacent the oxide portions having upward protruding outer polysilicon fence portions; contacting the semiconductor wafer process surface with an aqueous HF solution; and, carrying out a downstream plasma etching process to remove polysilicon fence portions.

Owner:TAIWAN SEMICON MFG CO LTD

Method for fabrication of physical patterns and the method for fabrication of device using the same

InactiveUS20060275712A1Improve solubilityReduce solubilityPhotomechanical apparatusRecord information storageEtchingMedicine

Etching properties are improved in a processing method of a phase change material in which the regions of one state are removed by etching to form a fine physical pattern. The phase change film is subjected to an advance treatment conducted before the etching, and this advance treatment uses water, an alkaline solution, an acid solution, or a surface-active agent. The regions to be removed by the etching are treated in the advance treatment to facilitate penetration of the etchant in the etching step so that complete removal is accomplished with no film residue. The advance treatment also improves etching resistance of the regions to be left unremoved. The process is thereby stabilized.

Owner:HITACHI LTD

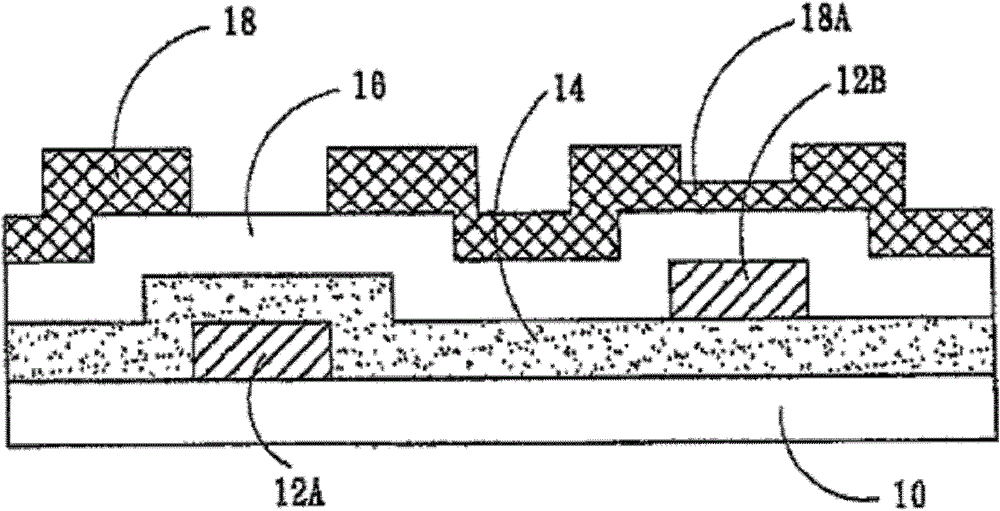

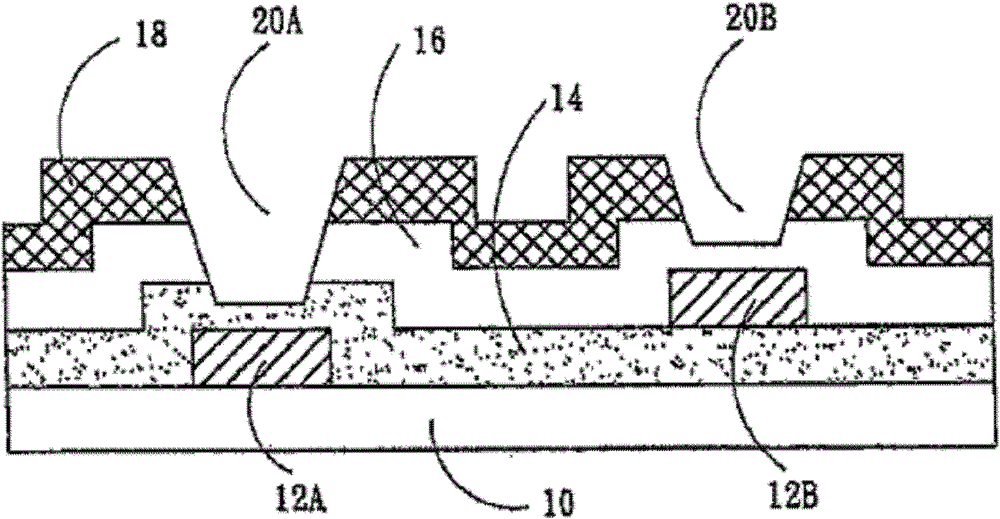

Display device contact hole forming method

ActiveCN102683266ARemove defects with poor uniformity controlAvoid over etchingSemiconductor/solid-state device manufacturingDisplay devicePhotoresist

The embodiment of the invention discloses a display device contact hole forming method which includes the following steps of: providing a substrate on which a first metal layer, an insulating layer, a second metal layer, a passivated layer and a patterning photoresist layer are sequentially formed; performing a first etching step to remove the entire thickness of the passivated layer and the partial thickness of the insulating layer above the first metal layer, and at the same time to remove the partial thickness of the corresponding halftone photoresist above the second metal layer; performing an ashing step to totally remove the corresponding halftone photoresist above the second metal layer; and performing a second etching step to remove the insulating layer retained in a deep hole above the first metal layer so as to expose the surface of the first metal layer and at the same time to remove the passivated layer retained in a shallow hole above the second metal layer so as to expose the surface of the second metal layer. The scheme of the invention can overcome the disadvantage that the uniformity of the remnant film of the photoresist is difficult to control, and the etching processes are optimized; the process of controlling the etching speed is simple; and over etching of the metal wirings can be avoided to the largest extent.

Owner:SHANGHAI AVIC OPTOELECTRONICS

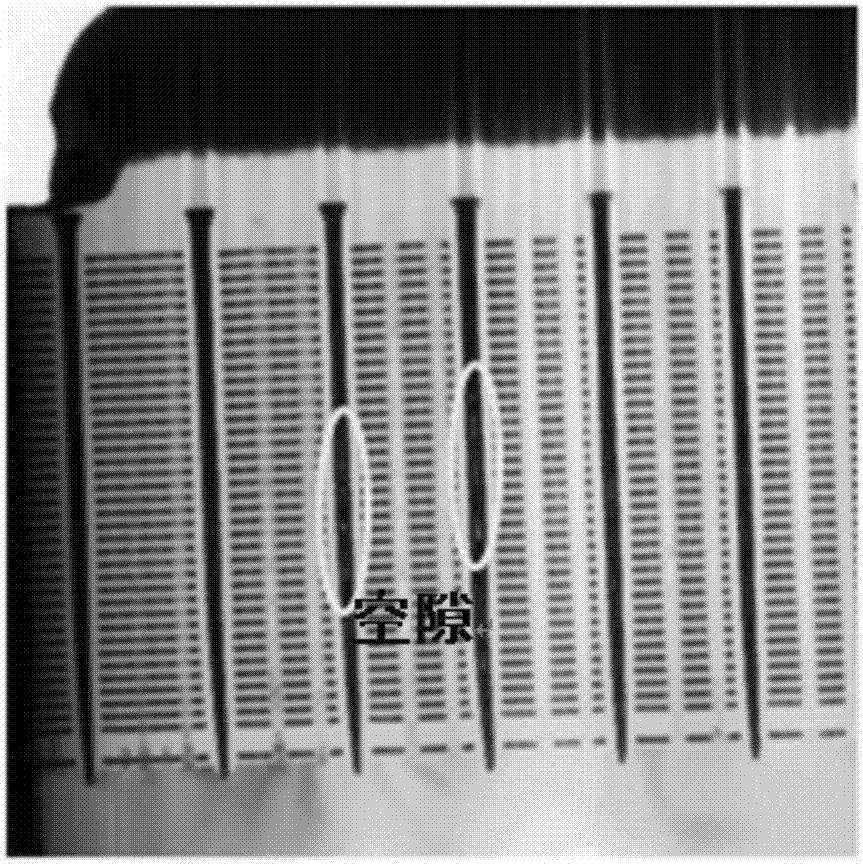

Method for forming via holes and embedded holes in multilayer circuit board

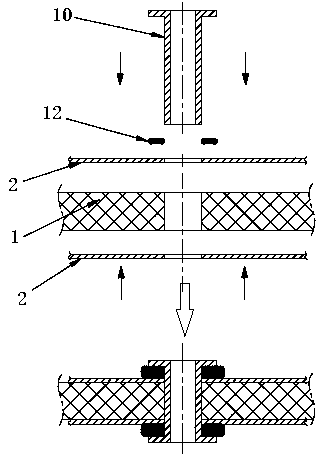

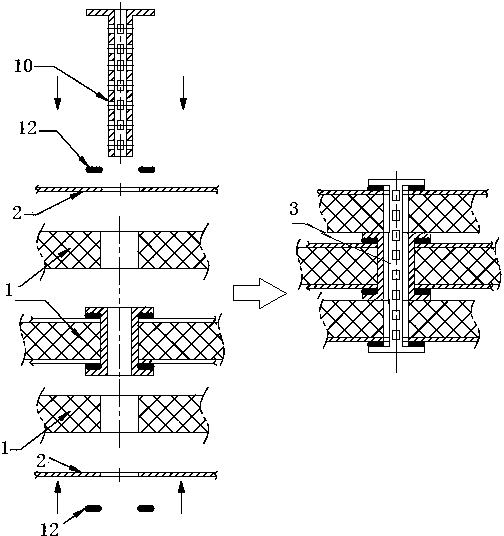

InactiveCN103889167AOptimizing the etch processMultilayer circuit manufacturePrinted element electric connection formationEngineeringSoldering

The invention relates to a copper cylinder used in the manufacturing process of a circuit board. The copper cylinder is a hollow copper cylinder. Through holes are vertically formed in the side wall of the hollow copper cylinder. Based on the hollow copper cylinder, environment-friendly forming of via holes and embedded holes in a multilayer circuit board can be achieved. According to the forming method of the embedded holes, the hollow copper cylinder is arranged in the circuit board, one end or two ends of the hollow copper cylinder are welded to the circuit board, and accordingly circuits on the two sides of the circuit board can be communicated. Single-layer circuit boards and double-layer circuit boards are laminated to form the multilayer circuit board, and the through holes in the inner-layer circuit board form the embedded holes. When the embedded holes need to be connected with one certain layer of circuit board, the hollow copper cylinder is used, the hollow copper cylinder is inserted into the corresponding positions of the embedded holes from the circuit board at the uppermost layer, tin soldering is performed, and soldering tin is led in through the through holes of the hollow copper cylinder so that soldering tin and the embedded holes of the inner-layer circuit board can be welded. A brand new method for forming via holes and embedded holes in the circuit board is provided, it is hopeful that the etching technology of the circuit board can be overall improved, an electroless plating copper electroplating technology is eliminated, and energy saving and environmental protection are achieved.

Owner:周小平

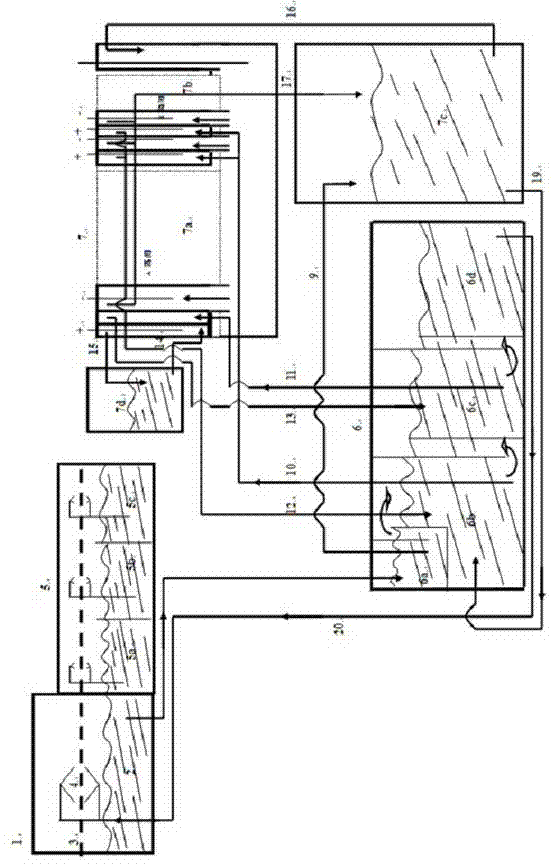

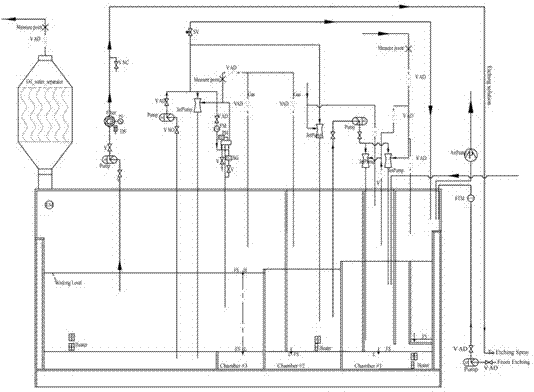

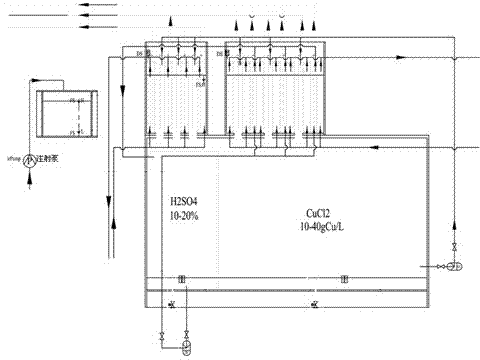

Electrolytic bath, acid etching liquid regenerating equipment and method using electrolytic bath

ActiveCN103757635ASimple structureCompact structurePhotography auxillary processesProcess efficiency improvementAcid etchingElectrolysis

The invention provides a method and equipment for treating waste acid etching liquid. The etching liquid is a solution for etching a printed circuit board inside an etching machine; overflowing treatment is carried out multiple times in a reactor; the reactor is connected with the electrolytic bath provided by the invention; the regenerated acid etching liquid is fed back to the etching machine to carry out a new round. The electrolytic bath has the outstanding effects that the structure is simple and compact, expected accelerators and reaction gases can be provided for the regenerating process, the whole process needs no any regenerating additive, the stability and the flexibility of the etching process are improved, and the etching process is greatly improved.

Owner:桥德联合自动化(苏州)有限公司

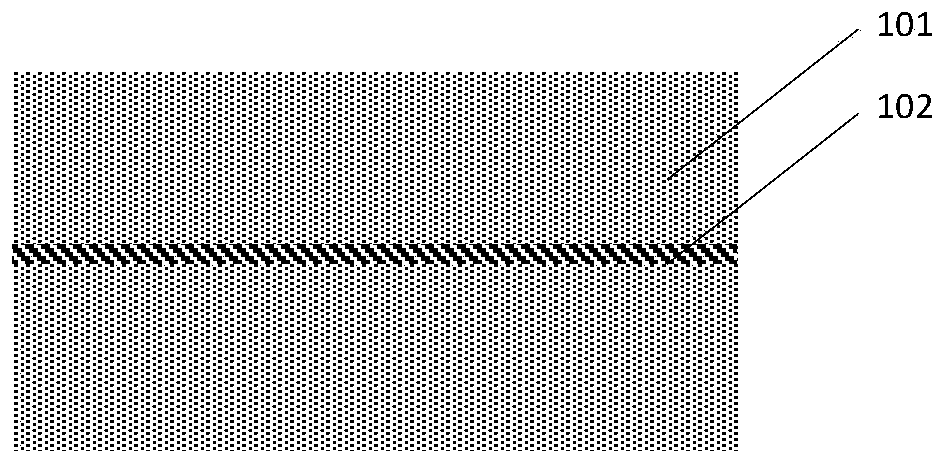

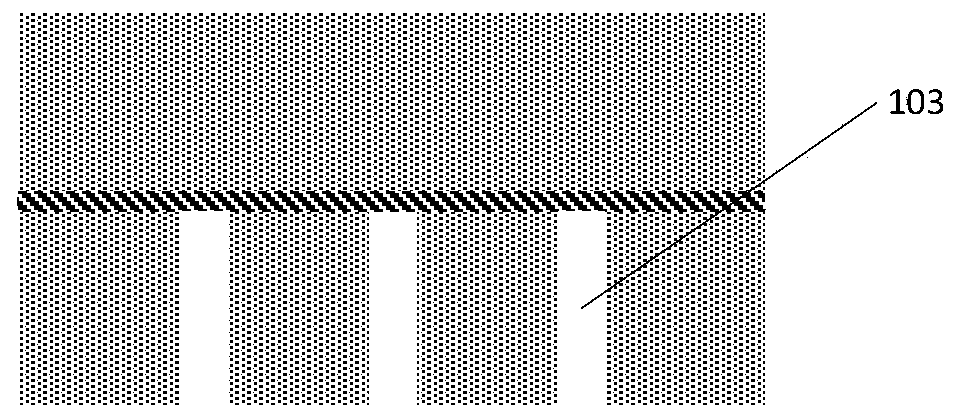

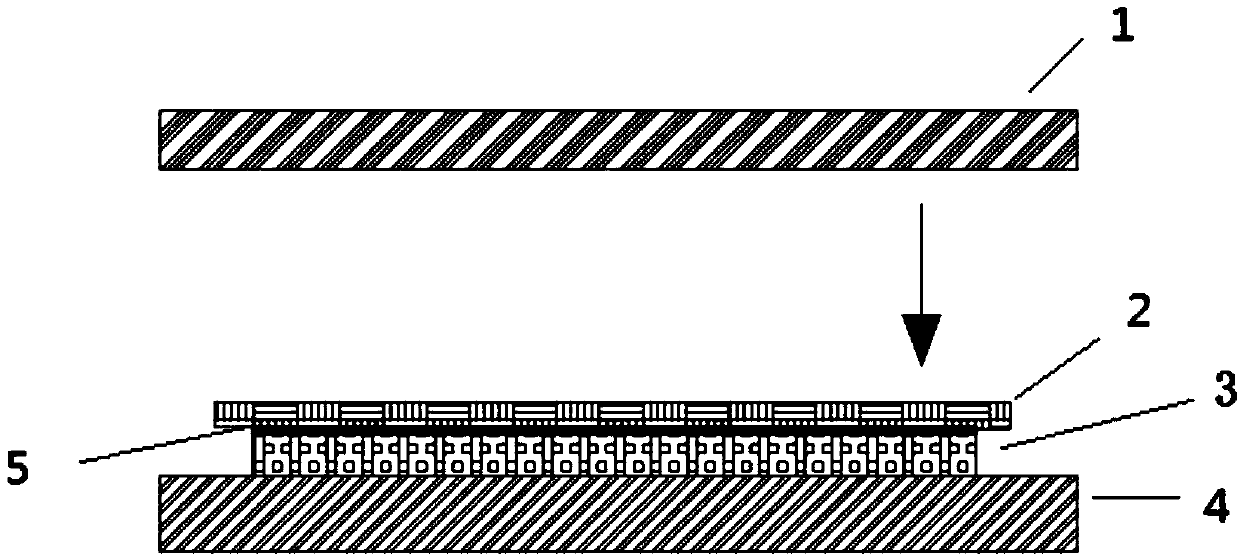

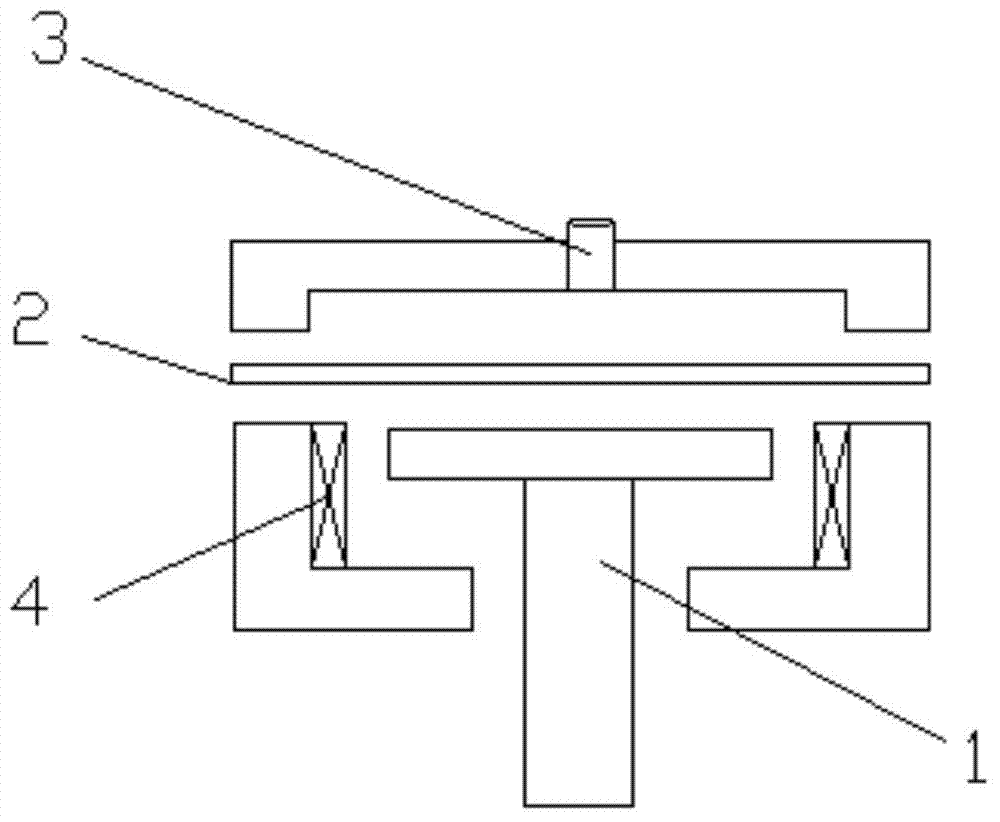

Method for embedding radio frequency chip into silicon cavity

PendingCN111341668AIncrease heightImprove flatnessSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringInterconnection

The invention discloses a method for embedding a radio frequency chip into a silicon cavity. The method specifically comprises the following steps: 101) a metal column forming step; 102) a cavity manufacturing step; 103) a chip embedding step. The invention provides the method for embedding the radio frequency chip in the silicon cavity, which is convenient to manufacture and simplified in process, and can realize heat dissipation and grounding interconnection at the bottom of the radio frequency chip.

Owner:浙江集迈科微电子有限公司

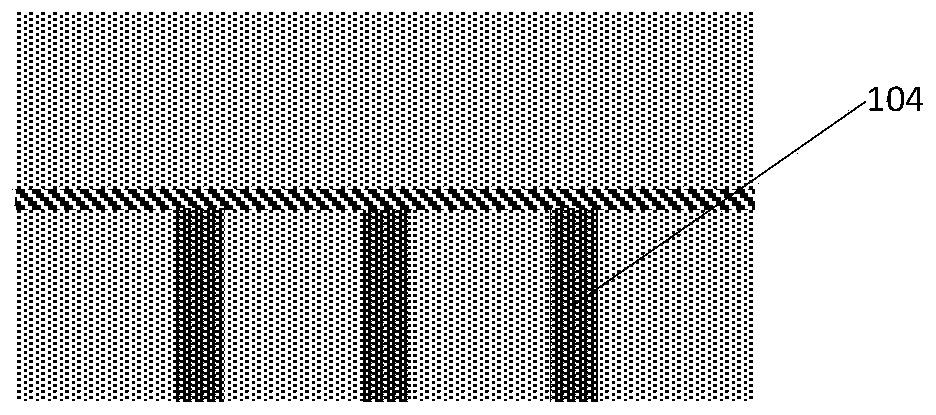

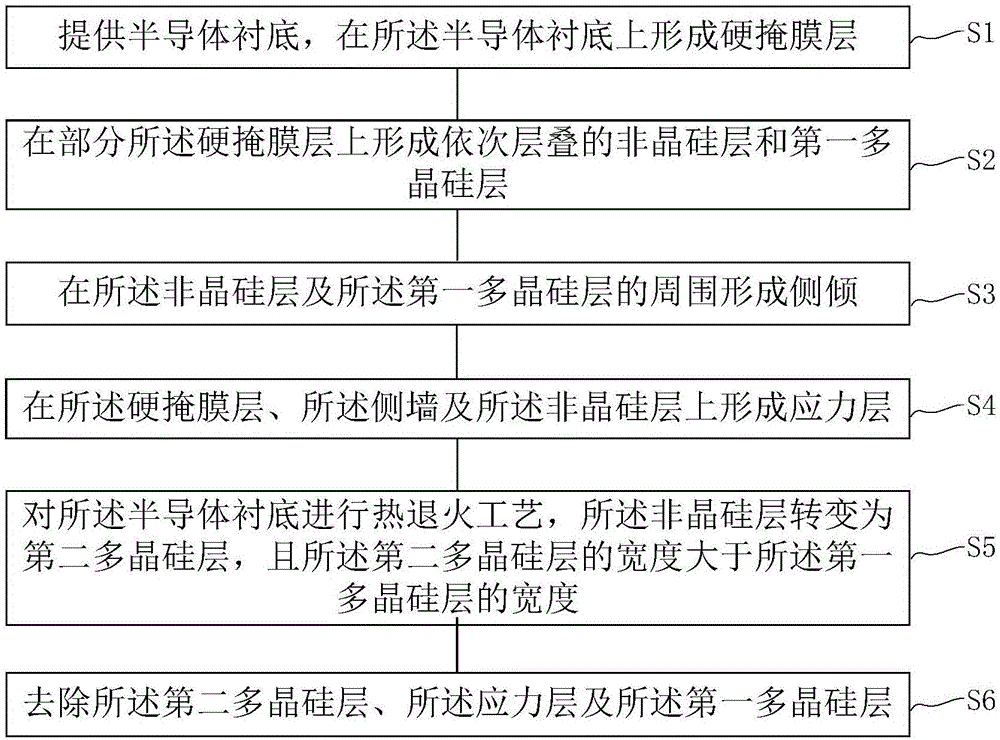

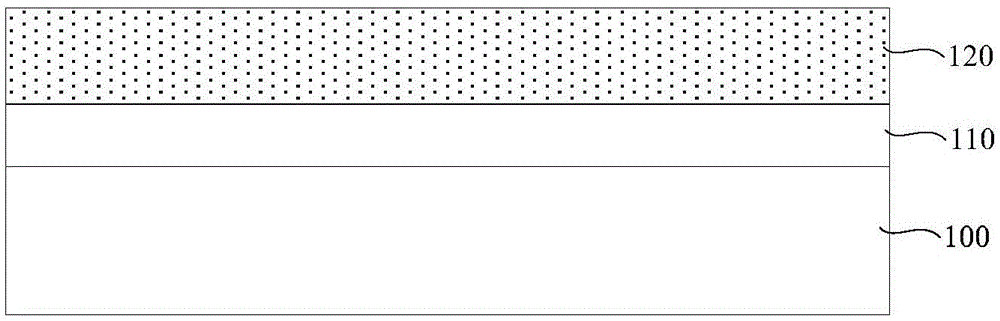

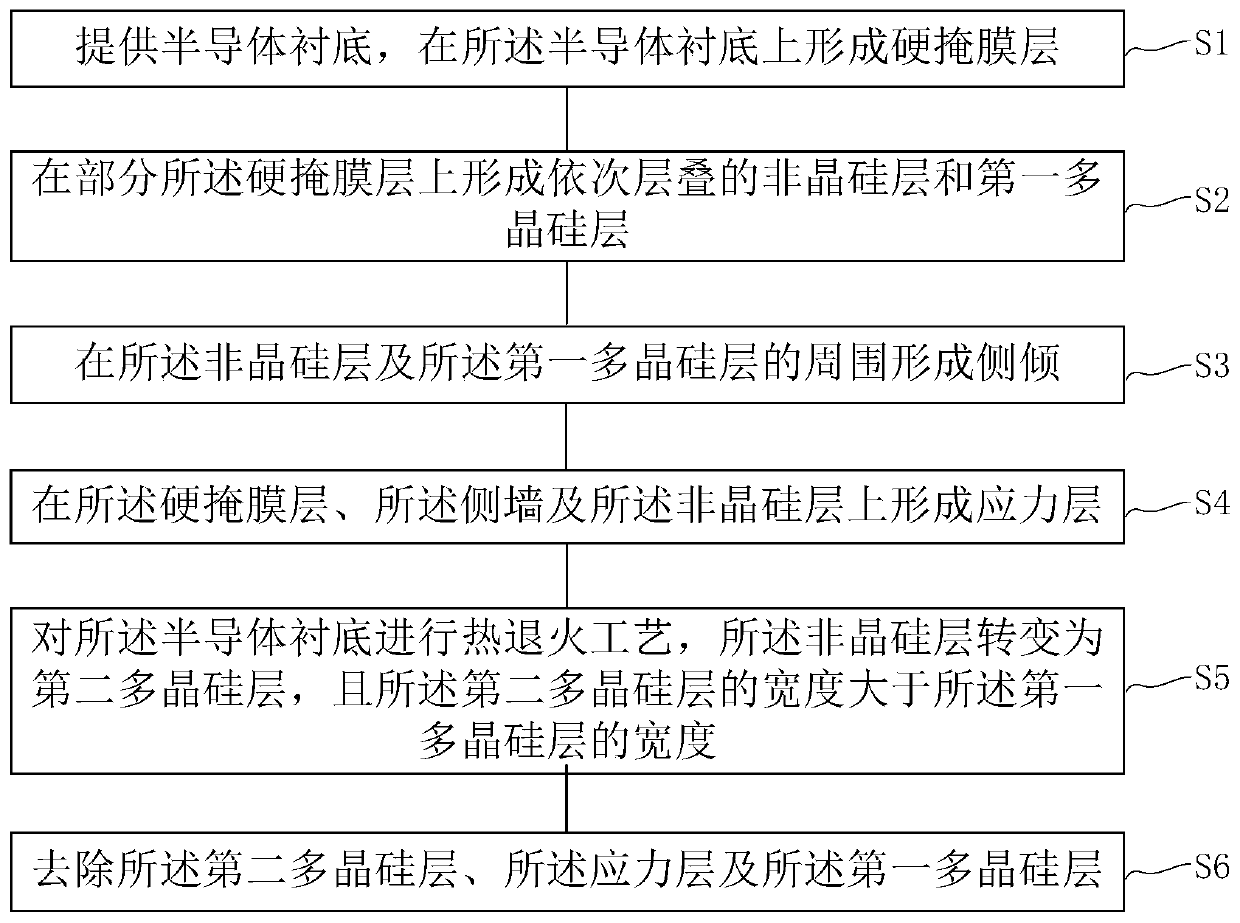

Multiple graphical mask preparation method

ActiveCN106783557AOptimizing the etch processSmall difference in morphologySemiconductor/solid-state device manufacturingAmorphous siliconSemiconductor

The present invention relates to a multiple graphical mask preparation method. The method comprises: providing a semiconductor substrate, and forming a hard mask layer on the semiconductor substrate; forming an amorphous silicon layer and a first polycrystalline silicon layer which are overlapped in order on part of the hard mask layer; forming a side lurch around the amorphous silicon layer and the first polycrystalline silicon layer; forming stress layers on the hard mask layer, the side wall and the amorphous silicon layer; performing heat annealing process of the semiconductor substrate, converting the amorphous silicon layer to a second polycrystalline silicon layer, wherein the width of the second polycrystalline silicon layer is larger than the width of the first polycrystalline silicon layer; and removing the second polycrystalline silicon layer, the stress layers and the first polycrystalline silicon layer. In the invention, the multiple graphical mask preparation method can reduce the morphology difference of the two side walls of the side wall so as to optimize the etching technology of the hard mark layer.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Method for relieving metal residues at side step of polycrystalline silicon structure

ActiveCN108231544AOptimizing the etch processEliminates metal residueSemiconductor/solid-state device manufacturingEtchingSilicon oxide

The invention discloses a method for relieving metal residues at a side step of a polycrystalline silicon structure. The method comprises the following steps of forming a polycrystalline silicon layer, and performing photoetching to define a forming area of a polycrystalline silicon structure; etching for the first time in an isotropy way; etching for the second time in the isotropy way, wherein avertical structure is formed at the side step of the polycrystalline silicon structure, and the top part of the vertical structure is of a circular arc structure which is formed during first-time etching; depositing an interlayer film which is formed by stacking common-pressure silicon oxide and boron-phosphorosilicate glass, wherein the thickness of the interlayer film is greater than or equal to the thickness of the vertical structure at the side step of the polycrystalline silicon structure; annealing and refluxing, wherein the boron-phosphorosilicate glass after refluxing forms a completely inclined structure at the side step of the polycrystalline silicon structure; forming an opening in contact with a hole; forming a metal layer, and performing metal etching. The method has the advantage that the boron-phosphorosilicate glass is of the completely inclined structure at the side step of the polycrystalline silicon structure, so as to eliminate the metal residues at the side step of the polycrystalline silicon layer.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

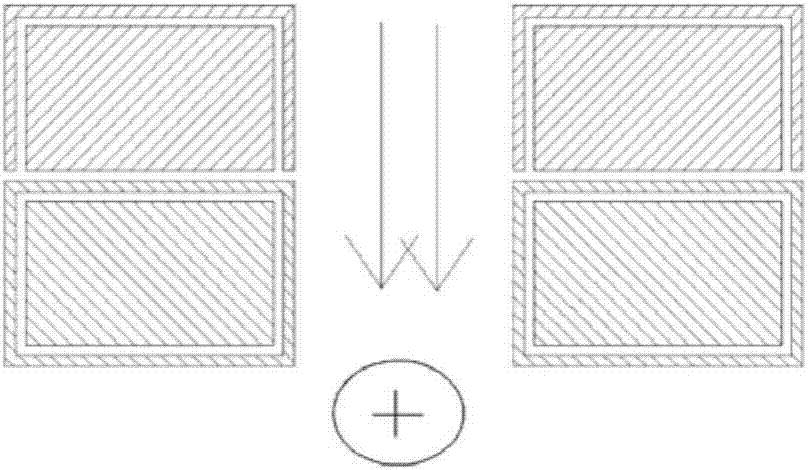

Integrated circuit (IC) package processing device and processing method

ActiveCN107611077AReduce loss costAchieve perfect separationSemiconductor/solid-state device manufacturingTemperature controlEngineering

The invention proposes an integrated circuit (IC) package processing device and processing method. The structure comprises a first temperature control suction disc, a second temperature control suction disc and a separation control unit, wherein the first temperature control suction disc is used for absorbing a metal carrier plate and heating the carrier plate, the second temperature control suction disc is used for absorbing an IC package body and controlling the IC package body to be maintained within a first temperature range, and the separation control unit is used for separating the metalcarrier plate from the IC package body when a temperature of the metal carrier plate is heated to reach a second temperature range and is started by the first temperature control suction disc. By theIC package processing device, the package process is optimized, the cost is favorably reduced, green production is achieved, a workpiece is not needed to be repeatedly circulated between a package plant and a substrate plant, so that the processing period is shortened, and control among processes is smoother.

Owner:深圳市鼎华芯泰科技有限公司

Step-by-step cyclic etching method for 3D NAND gate line slit trench

ActiveCN107978605AGood lookingEasy to fillSolid-state devicesSemiconductor devicesProcess qualityNAND gate

A step-by-step cyclic etching method for a 3D NAND gate line slit trench is provided. By splitting two etching steps ME1 and ME2 in a 3D NAND gate line slit trench etching process into multiple sub-steps, alternately performing the multiple sub-steps of the ME1 and ME2, and performing an OE step after the sub-steps are performed cyclically, the etching rate of a oxidizing dielectric layer and theetching rate of an nitride dielectric layer are balanced by the alternate etching of the ME1 and ME2. By implementing the step-by-step cyclic etching process, a deep trench structure with good morphology can be obtained, and the window of an etching process is expanded, so that the gate line slit trench is prepared into a good conical morphology, which is beneficial to subsequent injection of thetungsten. Thus, the process quality after a dry etching method is improved, void defects are reduced, and a product yield is improved.

Owner:YANGTZE MEMORY TECH CO LTD

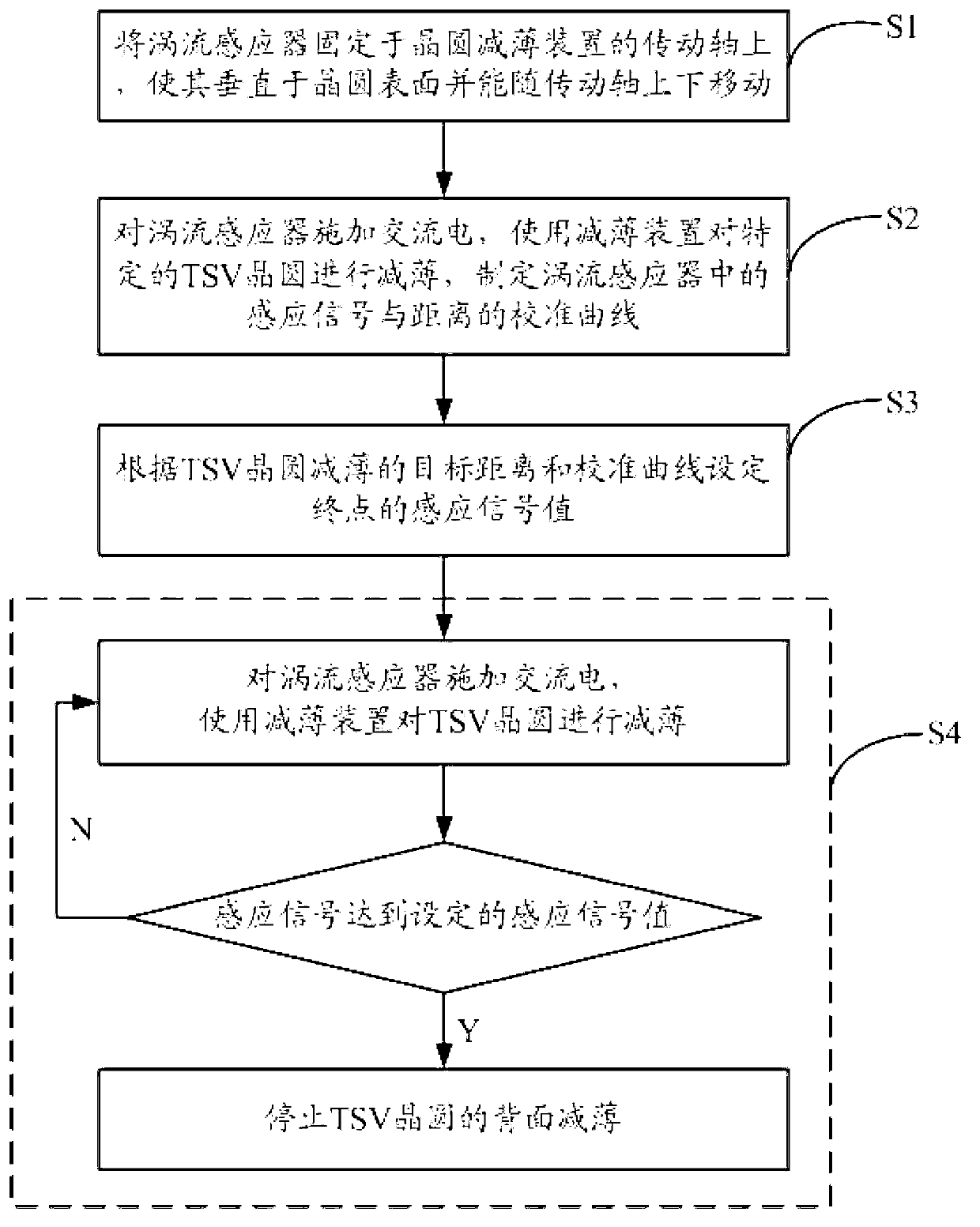

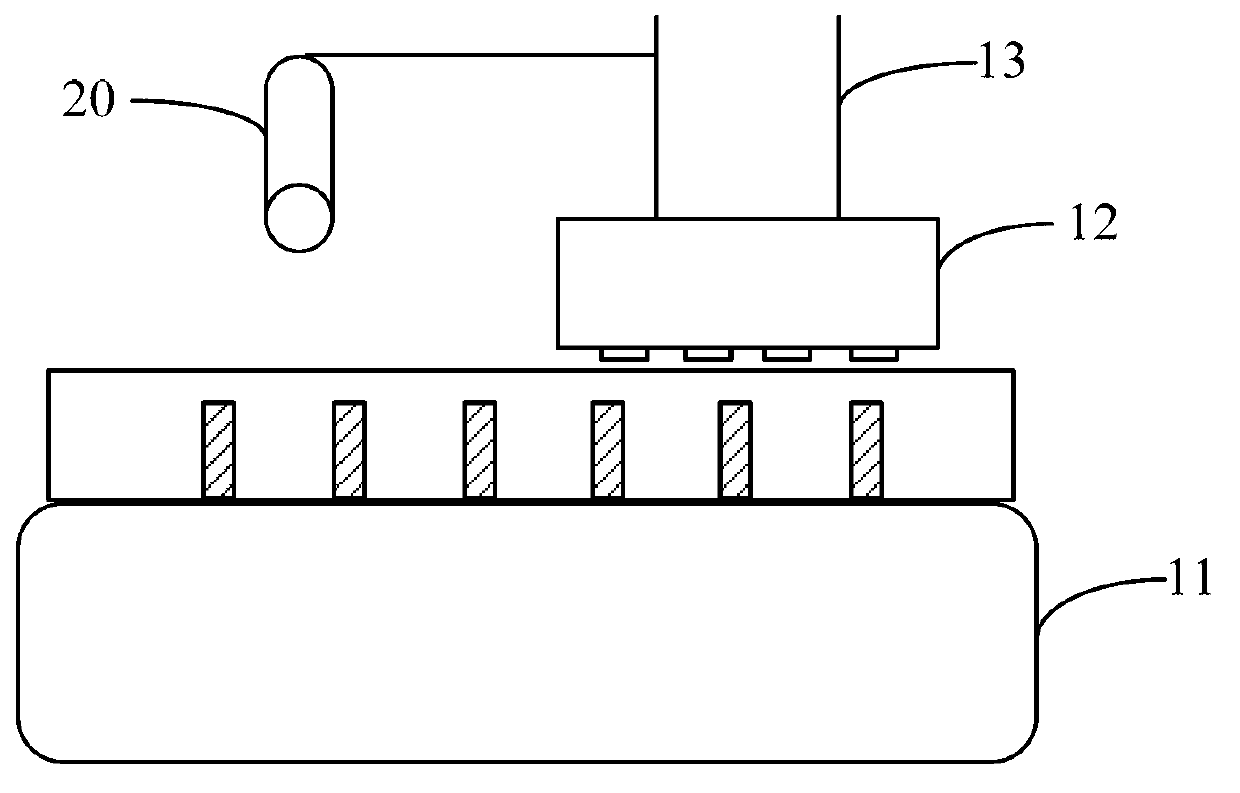

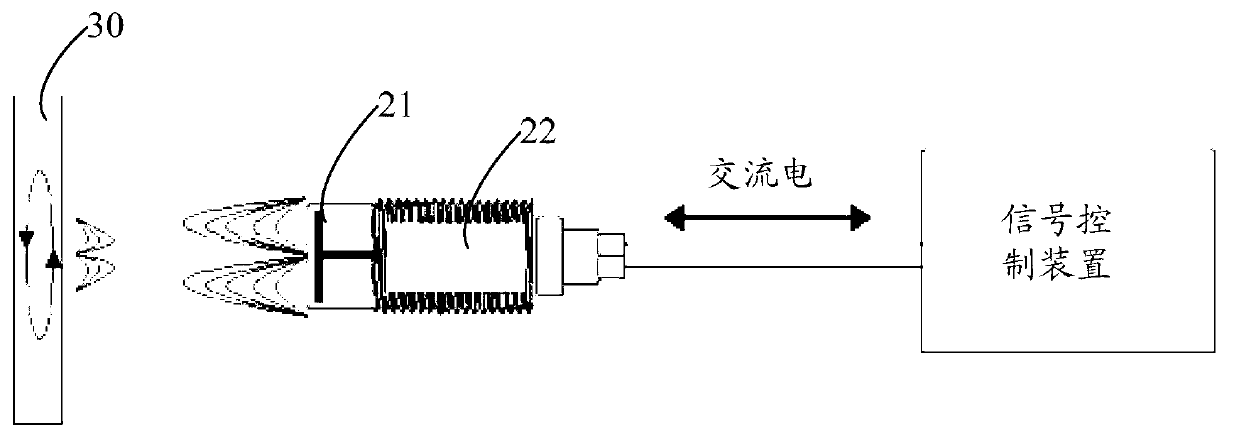

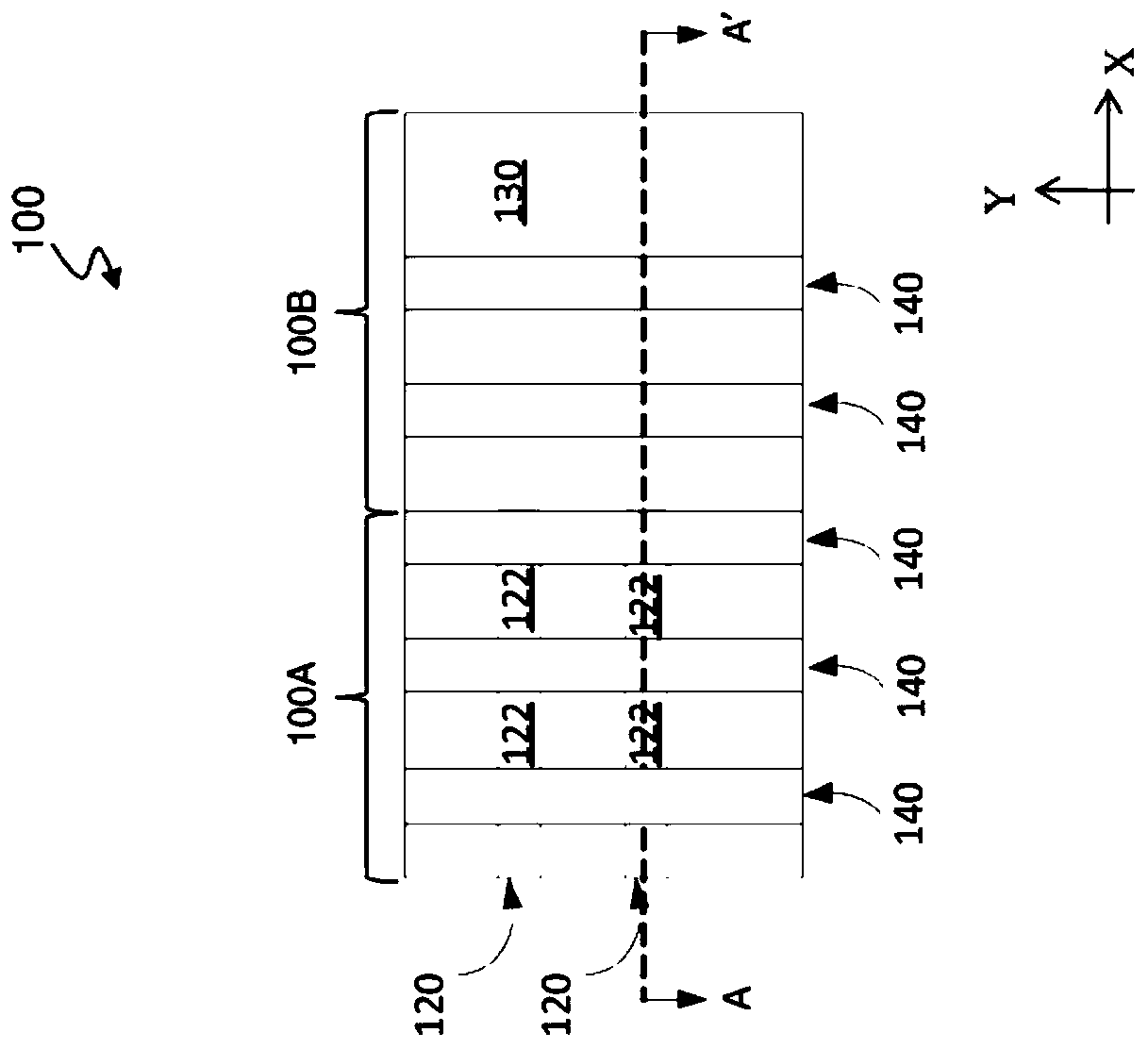

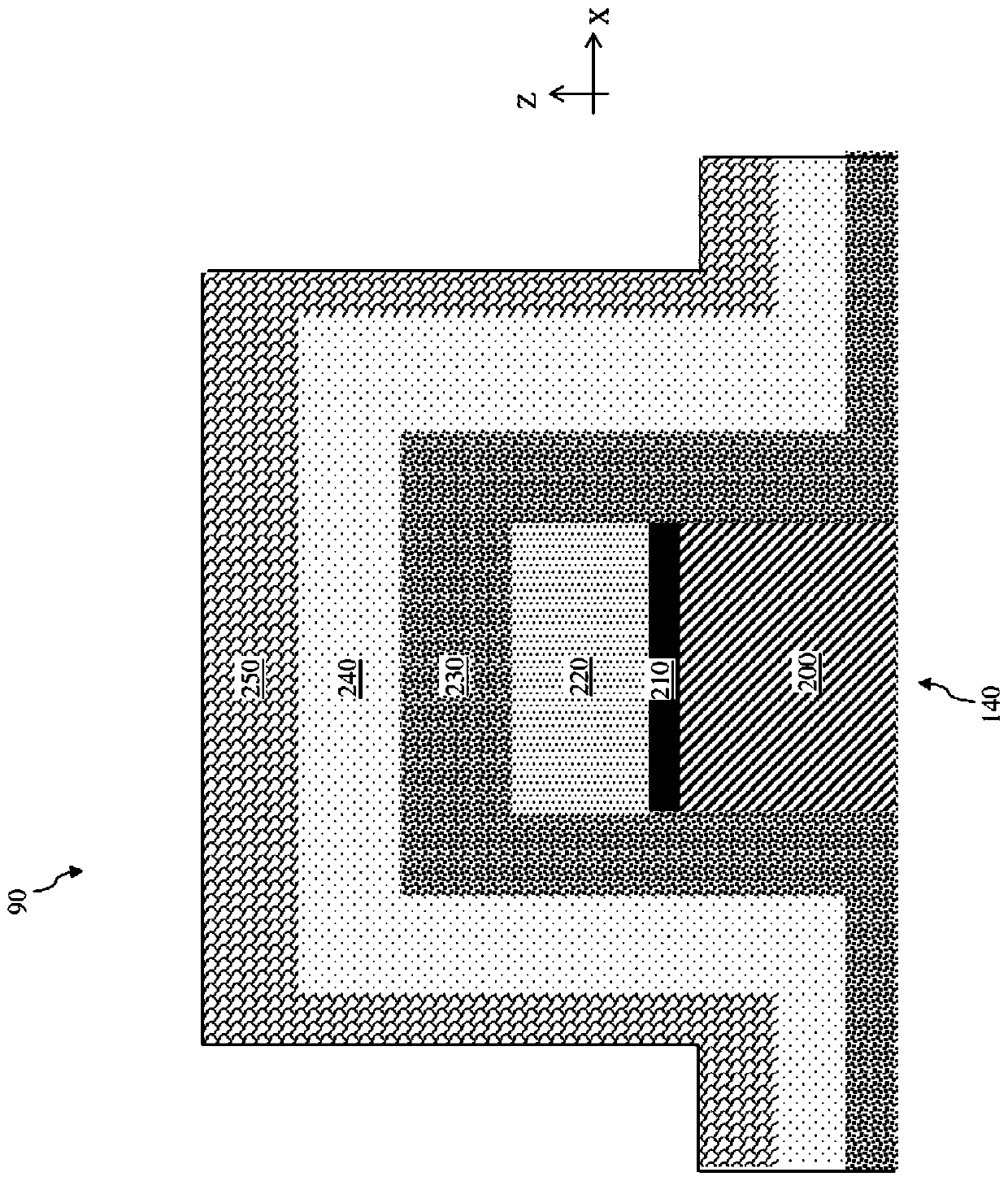

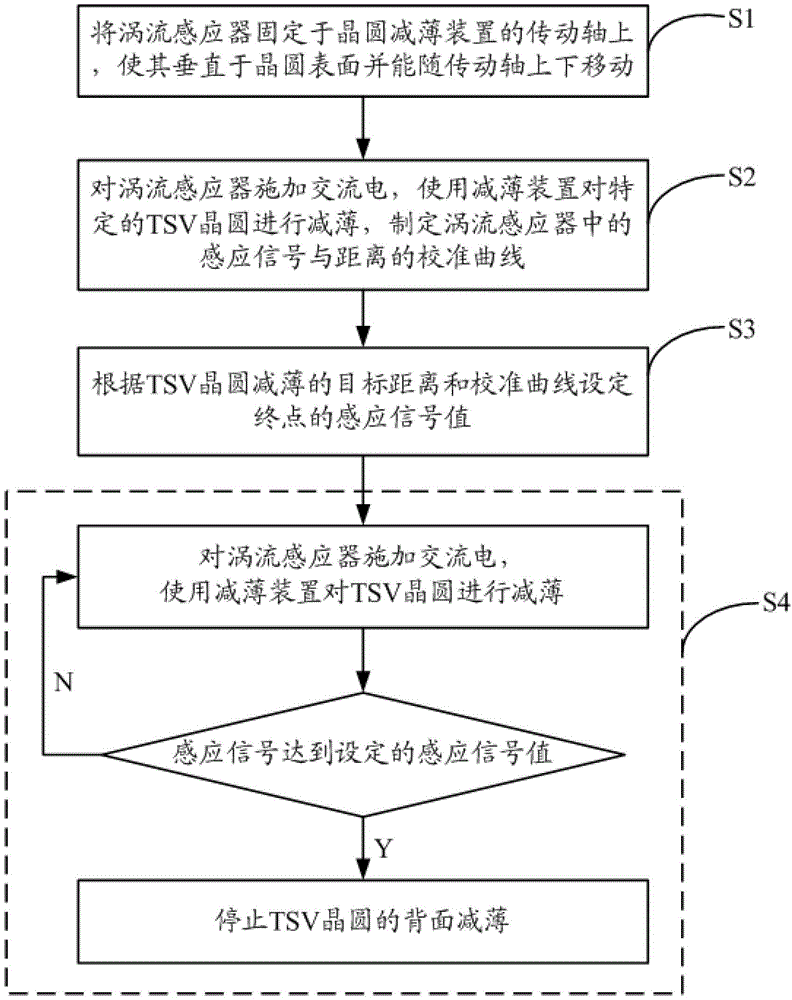

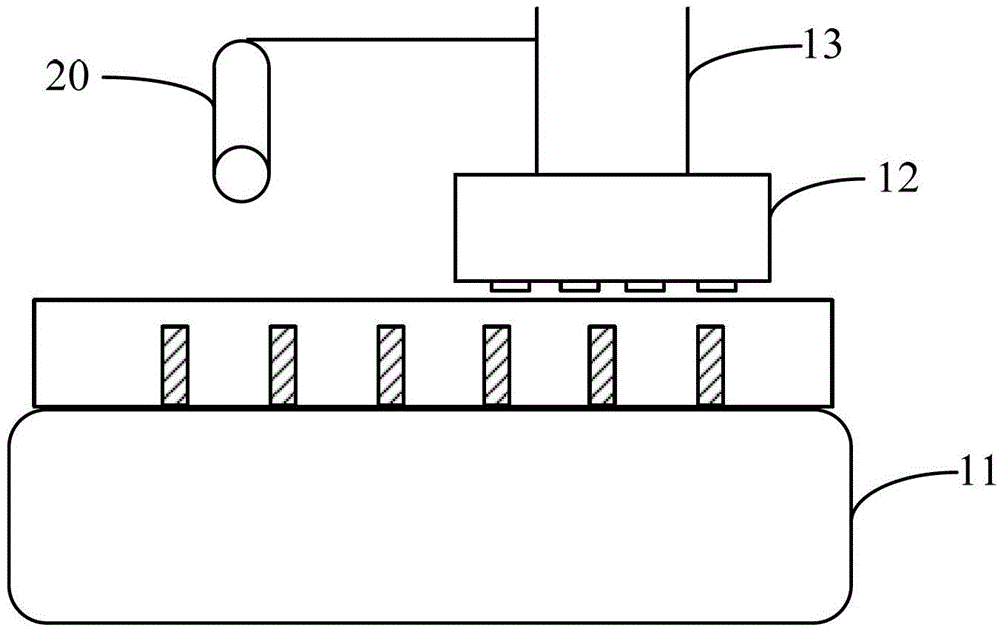

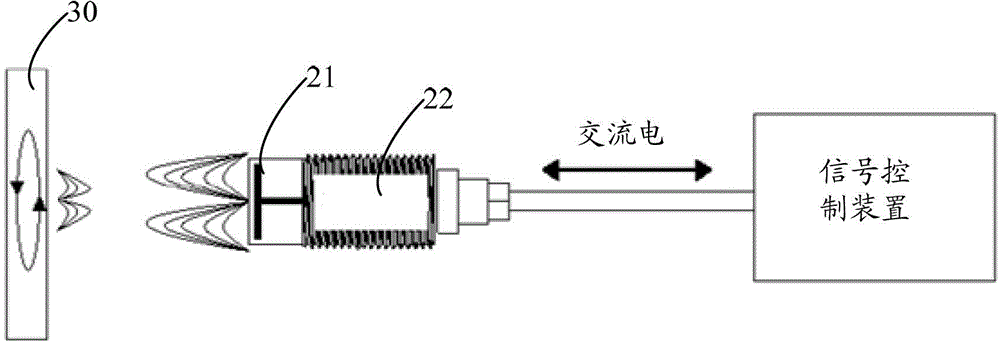

TSV wafer reverse side thinning control method and system based on vortex technology

ActiveCN103346117AReduce measurement errorEasy to installSemiconductor/solid-state device manufacturingCalibration curveSignal on

The invention discloses a TSV wafer reverse side thinning control method and system based on the vortex technology. The method includes the steps that a vortex sensor is fixed on a transmission shaft of a wafer thinning device and made to be perpendicular to the surface of a wafer and move up and down along with the transmission shaft; an alternating current is applied to the vortex sensor, the thinning device is used for thinning the specific TSV wafer, and a calibration curve of induction signals and distance of the vertex sensor is formulated; an induction signal value of a terminal point is set according to the thinning target distance of the TSV wafer and the calibration curve; the alternating current is applied to the vortex sensor, the thinning device is used for thinning the TSV wafer, and when the induction signals on the vortex sensor reach the set induction signal value, thinning of the reverse side of the TSV wafer is stopped. The TSV wafer reverse side thinning control method and system effectively achieves non-contact measurement, is small in measuring errors, and can accurately control the thickness of the wafer at the bottom of a metal conductive column. The vortex sensor is convenient to install, and low in process cost.

Owner:北京中科微知识产权服务有限公司

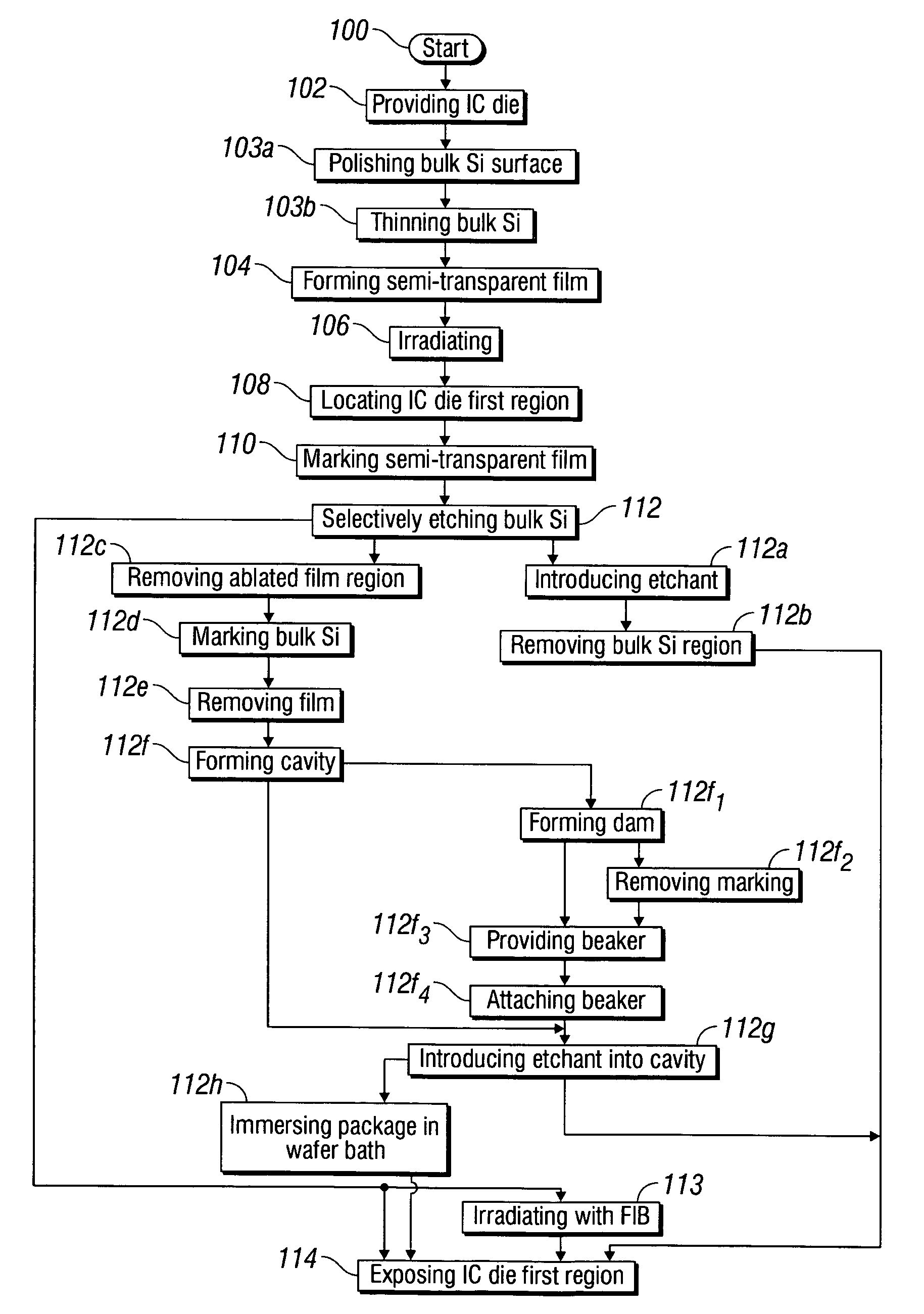

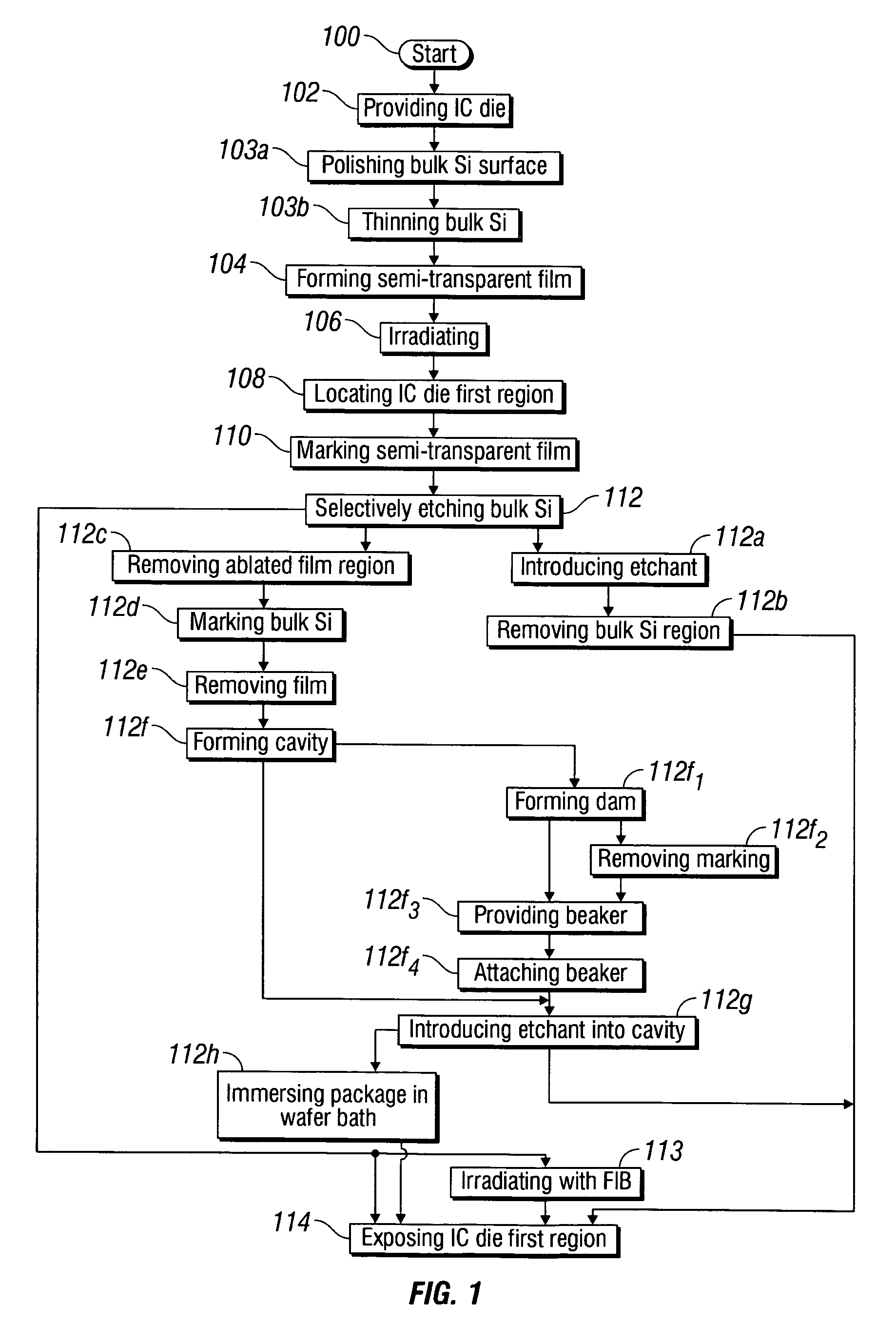

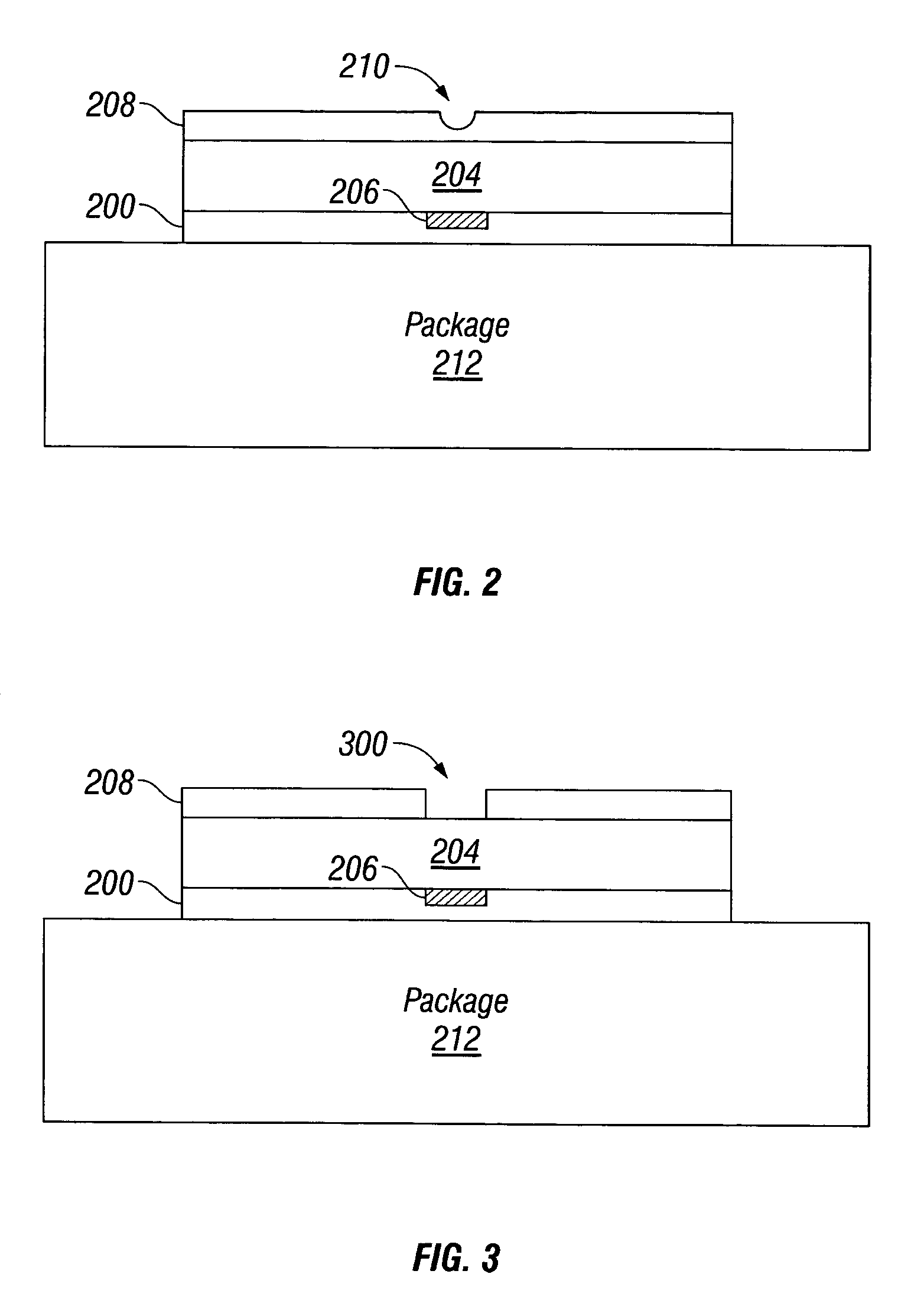

System and method for selectivity etching an integrated circuit

InactiveUS7402469B1Use minimizedConsiderable timeSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsLength waveSilicon

Owner:QUALCOMM INC

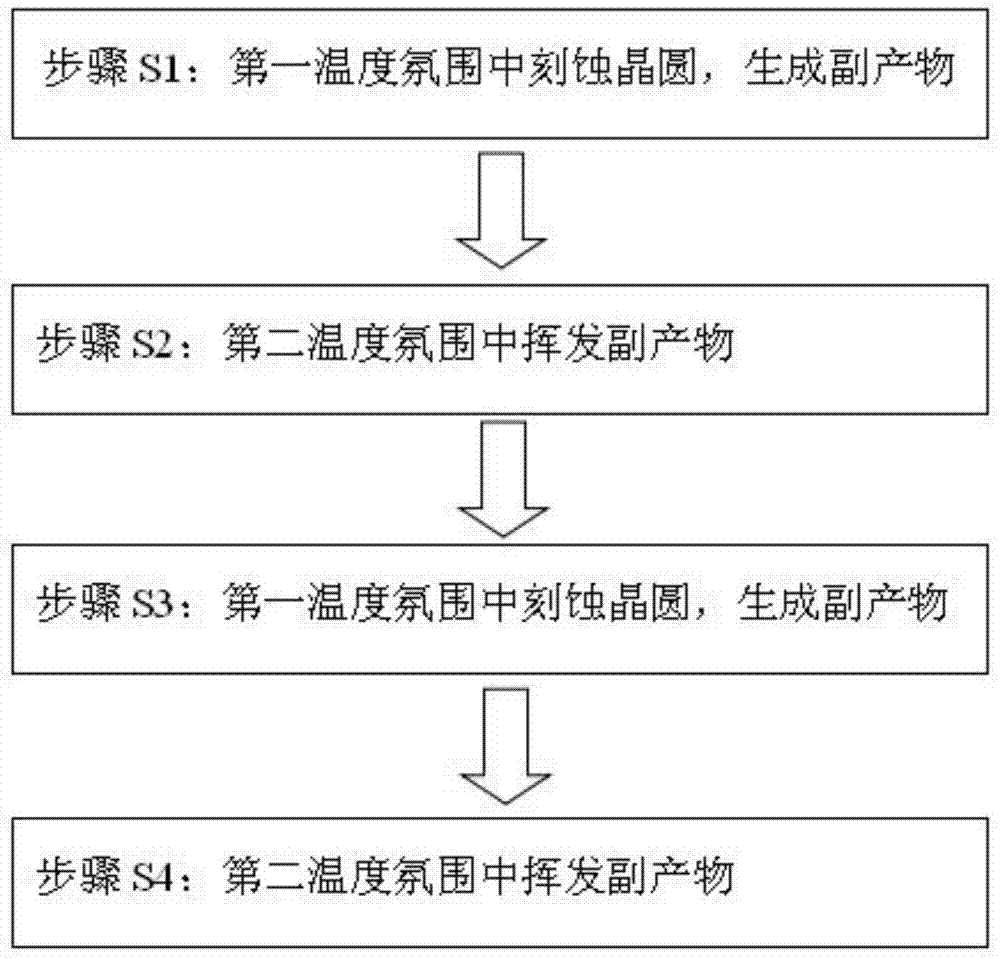

Etching device and method

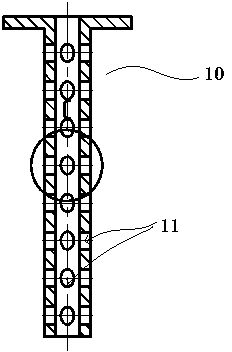

ActiveCN104269371AOptimizing the etch processImprove yieldSolid-state devicesSemiconductor/solid-state device manufacturingReaction chamberChemistry

The invention discloses an etching device and method. The etching device is provided with a reaction chamber which comprises a plurality of first substrates and a plurality of second substrates, wherein the first substrates and the second substrates are arranged alternatively. Wafers are conveyed into the reaction chamber, sequentially pass through the first substrate, the second substrate, the first substrate and the second substrate for being processed, and circulate in this way, so that the circulation process of etching, volatilizing, etching and volatilizing of the wafers is finished. Accordingly, the etching process of the wafers is optimized to a great extent, the process production of the multiple wafers can be carried out, the yield is high, it is ensured that by-products generated in the wafer etching process can be removed completely, and the yield of the wafers is greatly increased.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

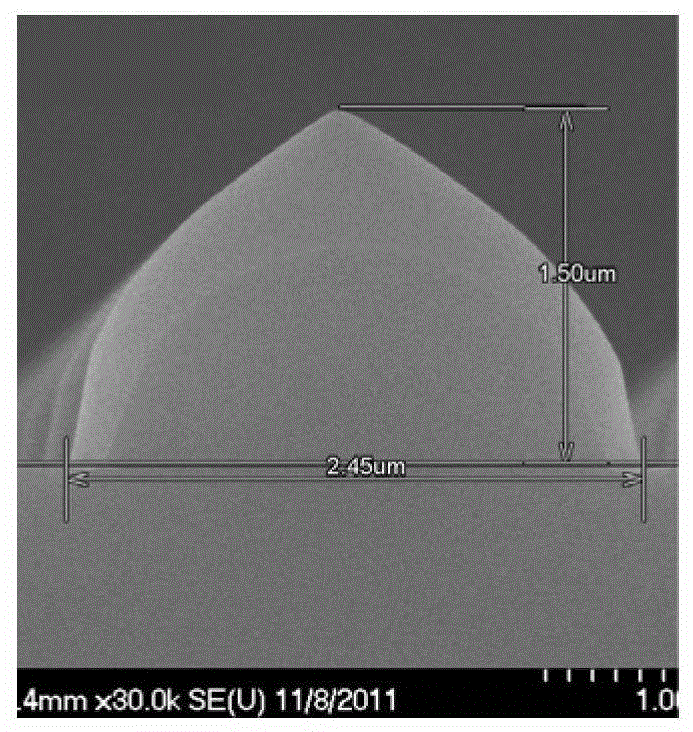

A pss patterned substrate etching method

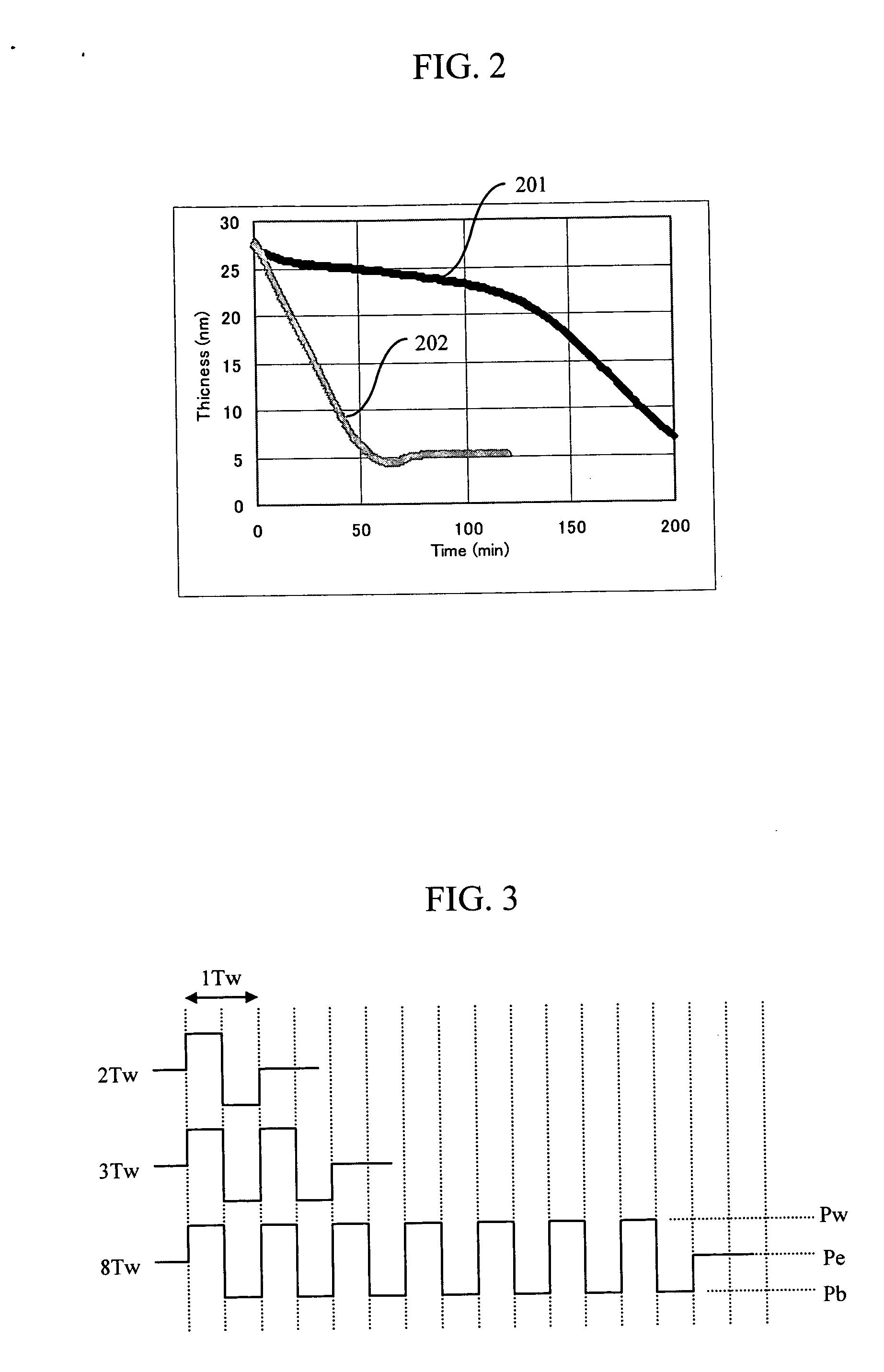

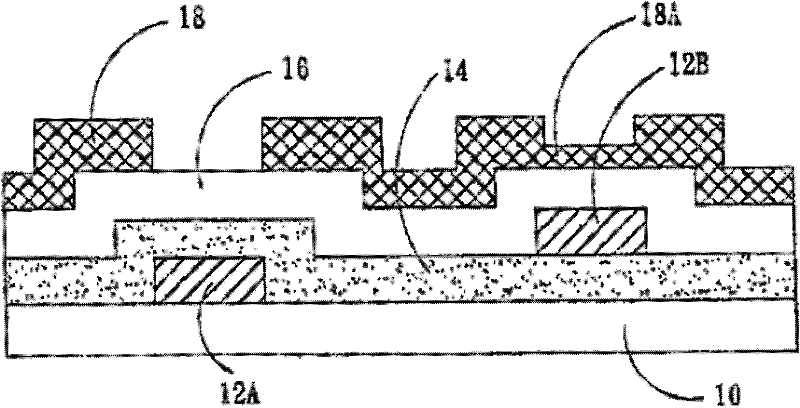

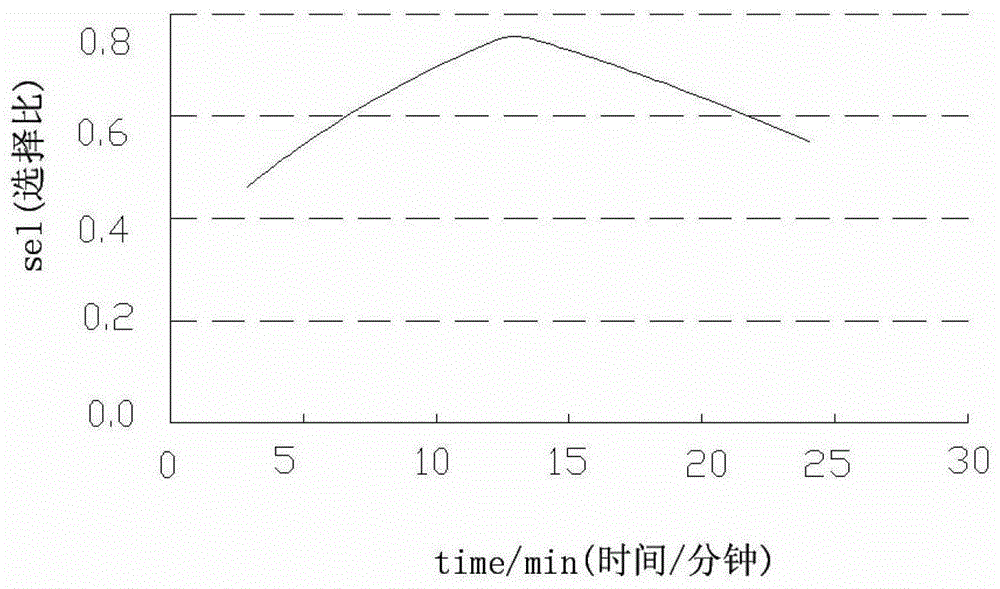

ActiveCN103887375BRF power increasedRF power reductionSemiconductor devicesEtchingPatterned substrate

The invention provides a PSS (Patterned Sapphire Substrate) etching method. The method includes: providing the substrate and manufacturing a mask with a needed pattern on the substrate; etching the substrate according to a main etching process; etching the substrate according to an over etching process; and ending the etching. The main etching process includes N etching sub-processes and as for two adjacent etching sub-processes, a lower-electrode radio-frequency power adopted in the latter etching sub-process is higher than a lower-electrode radio-frequency power which is adopted by the former etching sub-process and N is an integer larger than or equal to 3. The PSS etching method provided by the embodiment of the invention inhibits a problem, which exists in the prior art, that a method which reduces the lower-electrode power causes a large increase of the bottom width of the PSS pattern and causes reduction of production efficiency so that the bottom width is effectively inhibited and a selection ratio of the whole main etching process is improved at the same time and the PSS etching process is improved and the growth quality of a GaN epitaxy is improved.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

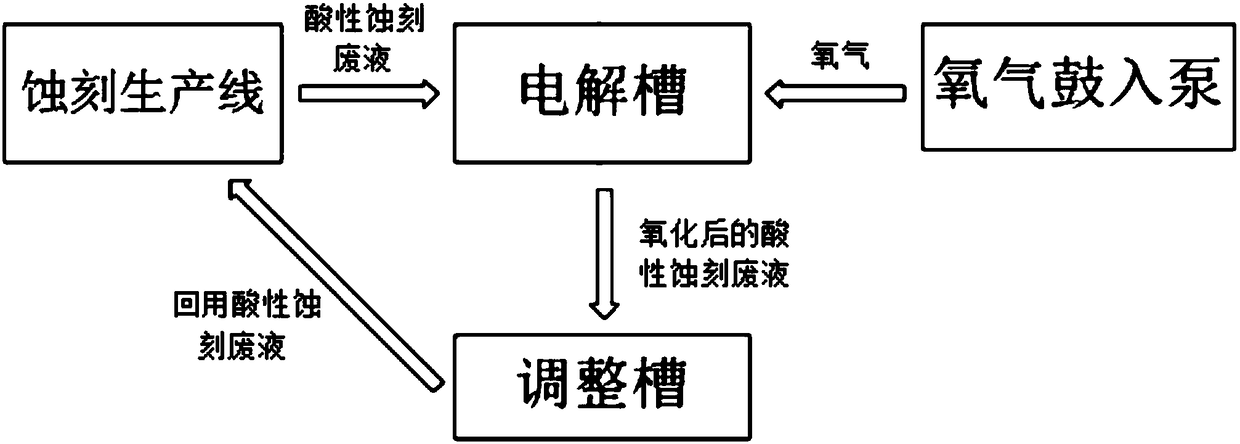

Method for regenerating acidic waste etching solution through synergistic oxidation by using hydrogen peroxide generated through oxygen cathode reduction and chlorine generated through anodic oxidation

The invention discloses a method for regenerating an acidic waste etching solution through synergistic oxidation by using hydrogen peroxide generated through oxygen cathode reduction and chlorine generated through anodic oxidation. The method includes the following steps that (1) the acidic waste etching solution flowing out of a printed circuit board production line is guided into an electrolyticbath through an etching bath, oxygen is introduced to the cathode of the electrolytic bath, meanwhile, the electrolytic bath is started, and the acidic waste etching solution is oxidized; and (2) theoxidized acidic waste etching solution is guided into a regulating tank, the acidity value and the total copper ion concentration of the oxidized acidic waste etching solution are regulated to a concentration range suitable for etching work, the oxidized acidic waste etching solution flows back to an etching working area, and the next round of etching is carried out. The method perfectly combinesthe two advantages that the oxygen is easily obtained and the hydrogen peroxide has high oxidizability; and moreover, operation is easy, the components of the etching solution are not changed, the stability of the etching process is improved, and the etching technology is improved.

Owner:SOUTH CHINA UNIV OF TECH

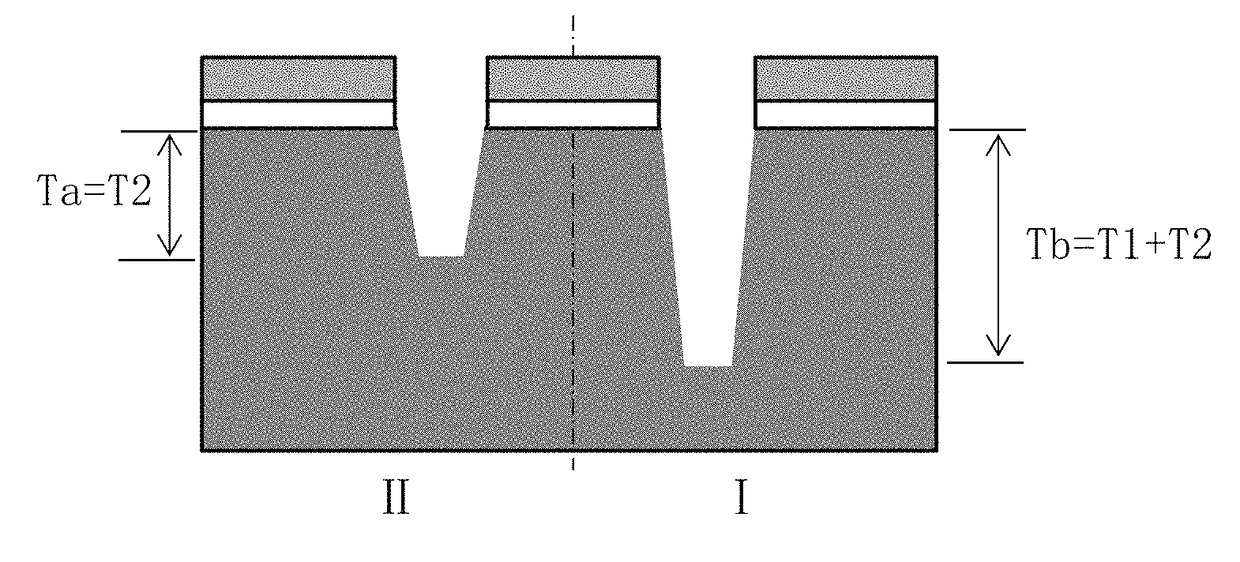

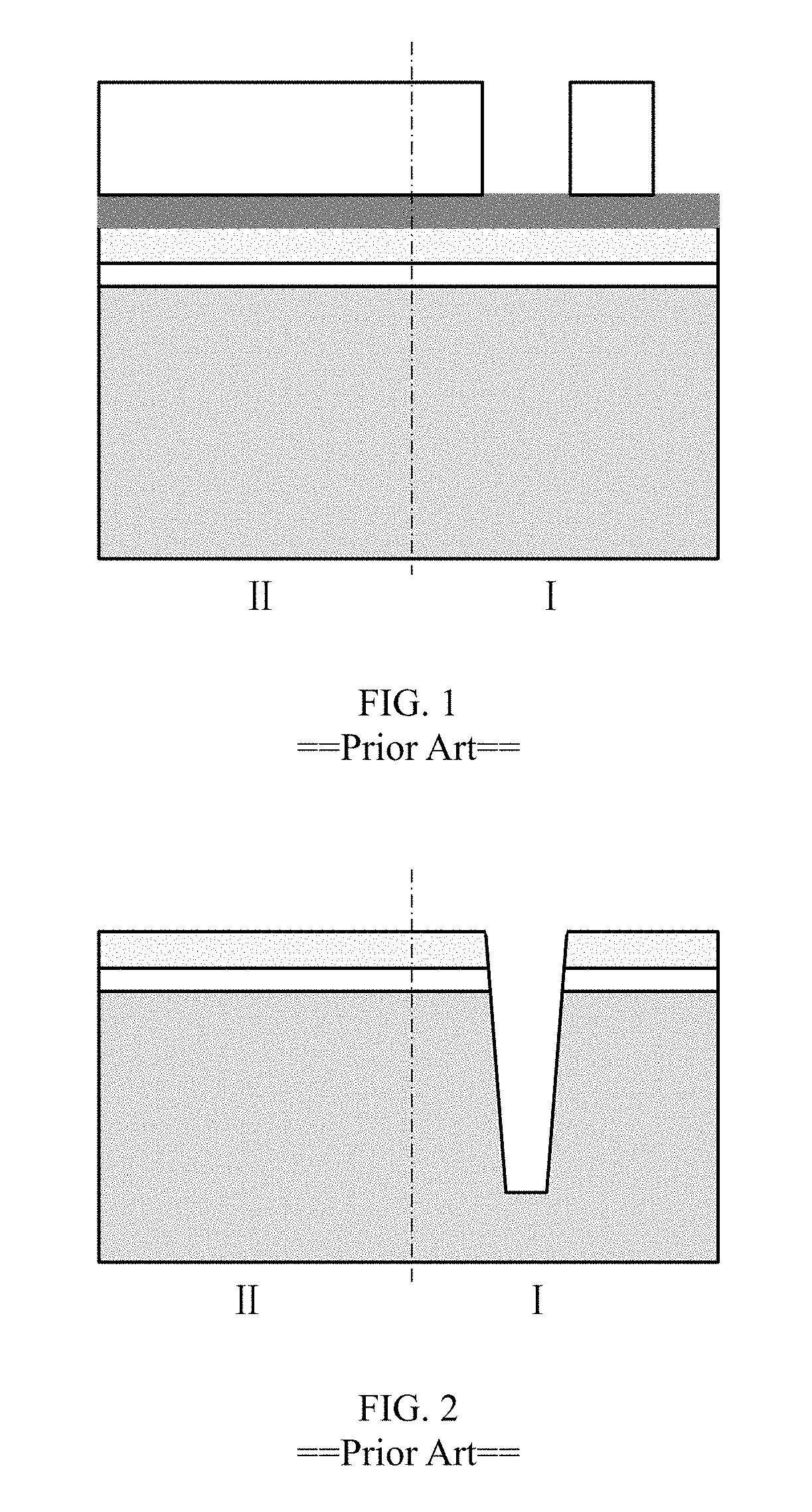

Method for forming shallow trenches of the dual active regions

ActiveUS9871064B1Meet needsLow-cost applicationSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSemiconductor

The invention disclosed a method for forming shallow trenches of the dual active regions. Firstly, forming an etch stop layer on a semiconductor substrate; secondly, using a first accurate photomask to expose and develop the semiconductor substrate, until the etch stop layer has been exposed on the top of the first shallow trench regions and the second shallow trench regions; thirdly, etching the etch stop layer entirely in the exposed regions; fourthly, using a second photomask to expose and develop the first shallow trench regions which require a deeper etch depth of the trench than that of the second shallow trench regions; fifthly, etching and forming preliminary entirely depth in the first shallow trench regions, and then removing the second photomask; at last, taking the etch stop layer as a mask, and simultaneously etching the first shallow trench regions and the second shallow trench regions to form the first hallow trenches and the second shallow trenches having different depths. The invention has realized a low-cost photomask application and an optimization of the etching process by optimizing the photomask design.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

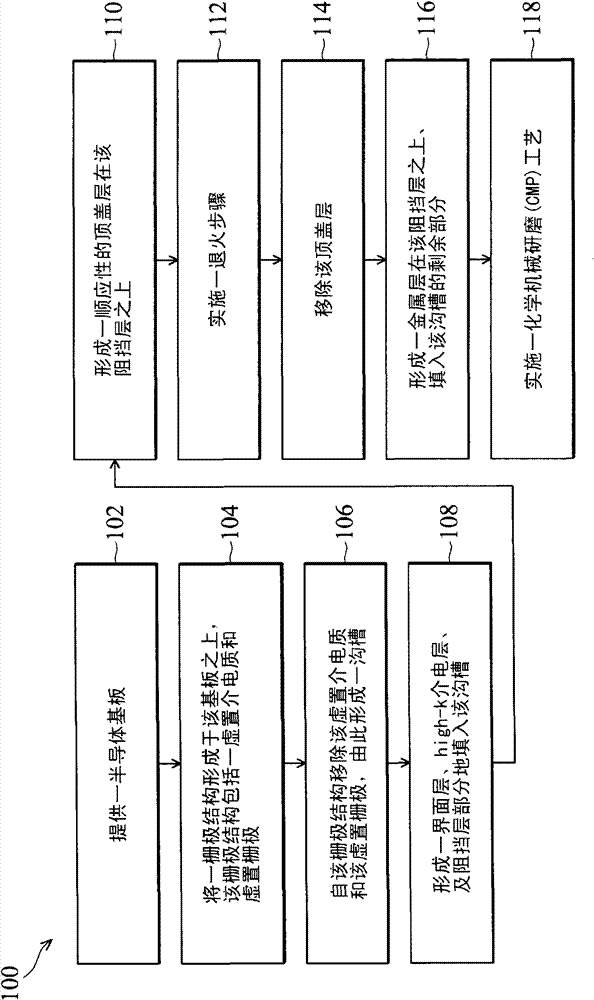

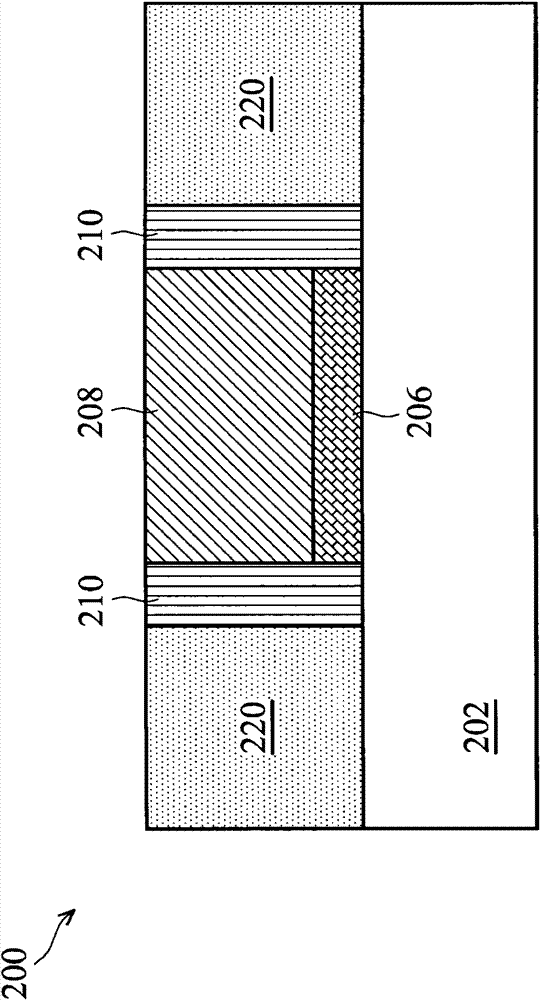

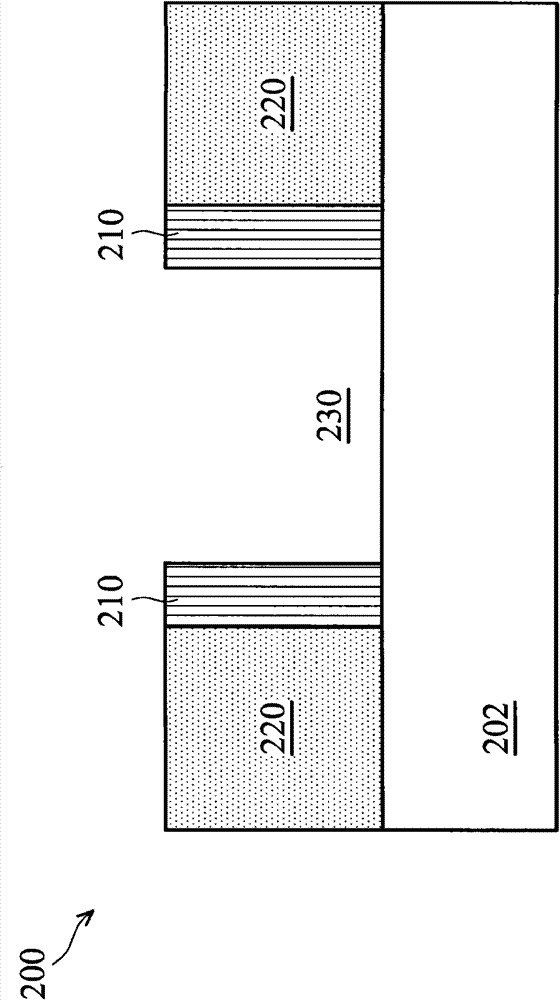

Method of fabricating high-k/metal gate device

ActiveCN102103994BImprove qualityCost-effectiveSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical conductorMetal device

The present disclosure provides a method that includes providing a semiconductor substrate; forming a gate structure over the semiconductor substrate, first gate structure including a dummy dielectric and a dummy gate disposed over the dummy dielectric; removing the dummy gate and the dummy dielectric from the gate structure thereby forming a trench; forming a boundary layer on the semiconductor substrate; forming a high-k dielectric layer on the boundary layer partially filling the trench; forming a barrier layer over the high-k dielectric layer partially filling the trench; forming an capping layer over the barrier layer partially filling the trench; performing an annealing process; removing the capping layer; forming a metal layer over the barrier layer filling in a remainder of the trench; and performing a chemical mechanical polishing (CMP) to remove the various layers outside the trench. The invention can improve the quality of the high-k dielectric layer in the final component.

Owner:TAIWAN SEMICON MFG CO LTD

Micromechanical tunable Fabry-Perot interferometer, an intermediate product, and a method for producing the same

ActiveUS9235043B2Reduce and avoid useHigh densitySpectrum generation using multiple reflectionPiezoelectric/electrostrictive devicesIntermediate productPhysics

Controllable Fabry-Perot interferometers include two mirrors with a space between them. The mirrors are such that at least one layer is made of silicon-rich silicon nitride. Additionally, the mirrors' surfaces are formed to be of a roughness which reduces the risk of the mirrors sticking to each other.

Owner:TEKNOLOGIAN TUTKIMUSKESKUS VTT

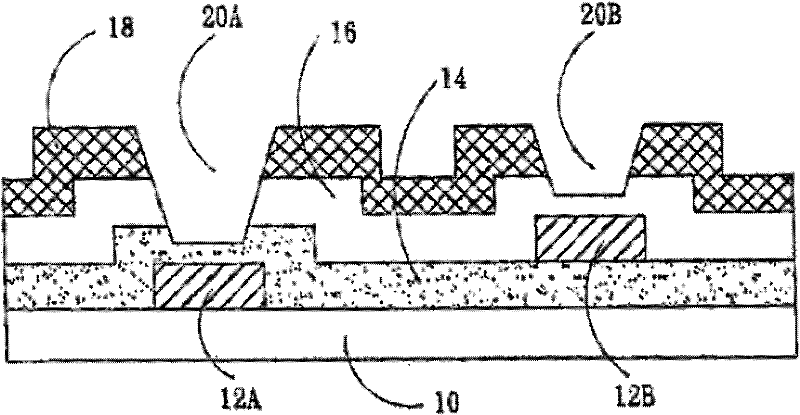

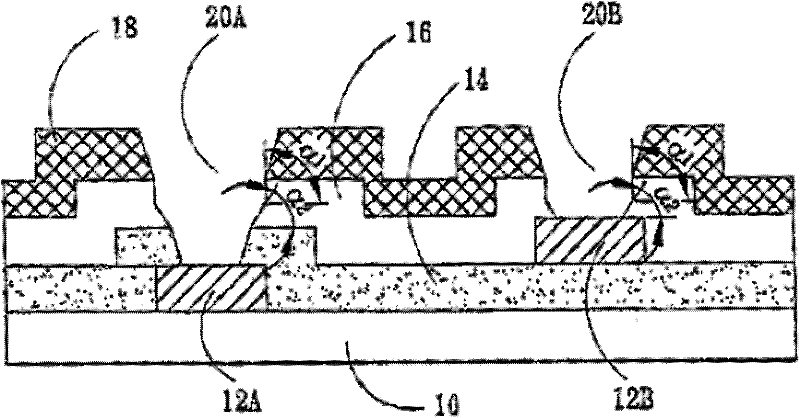

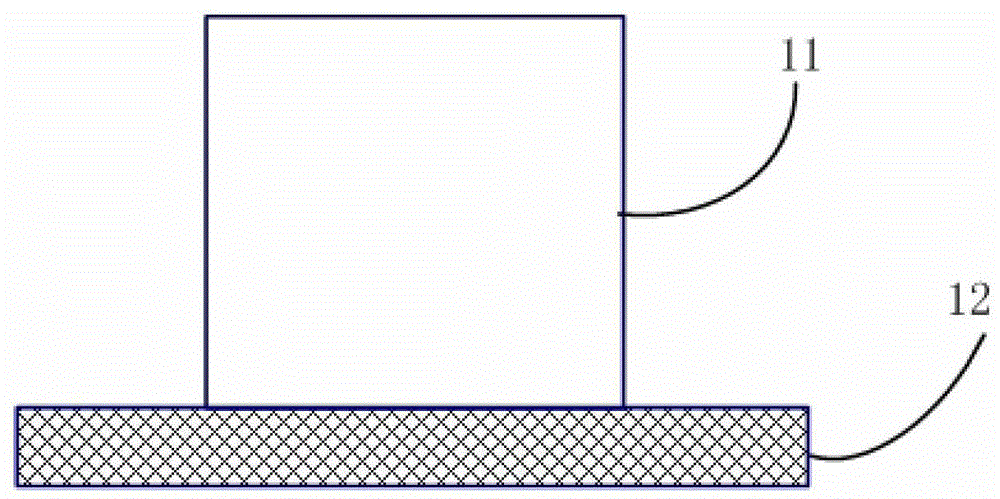

Semiconductor device and method for forming the same

ActiveCN110957367AOptimizing the etch processEtching process is efficient and more effectiveSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor structureDevice material

A semiconductor structure includes a first device and a second device. The first device includes: a first gate structure formed over an active region and a first air spacer disposed adjacent to the first gate structure. The second device includes: a second gate structure formed over an isolation structure and a second air spacer disposed adjacent to the second gate structure. The first air spacerand the second air spacer have different sizes. The invention also relates to the semiconductor device and a device for forming the same.

Owner:TAIWAN SEMICON MFG CO LTD

Thinning control method and system for backside of tsv wafer based on eddy current technology

ActiveCN103346117BReduce measurement errorPrecise thickness controlSemiconductor/solid-state device manufacturingSignal onEngineering

Owner:北京中科微知识产权服务有限公司

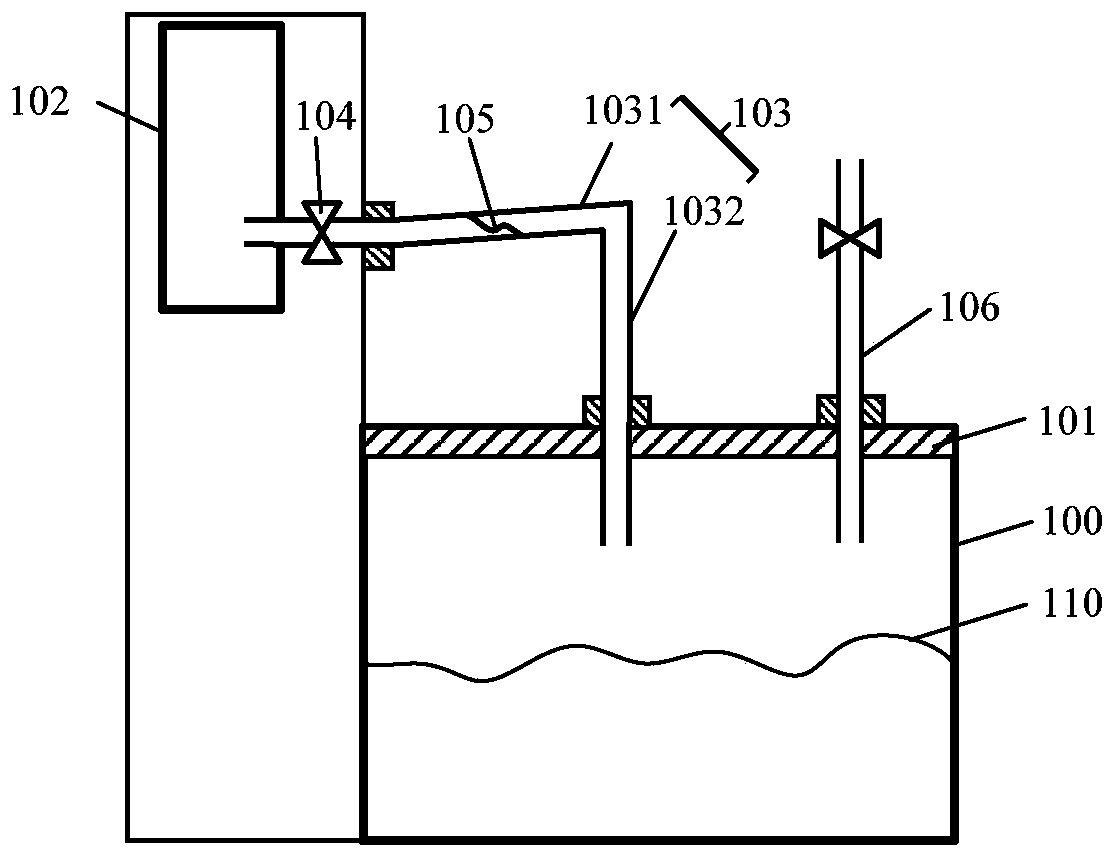

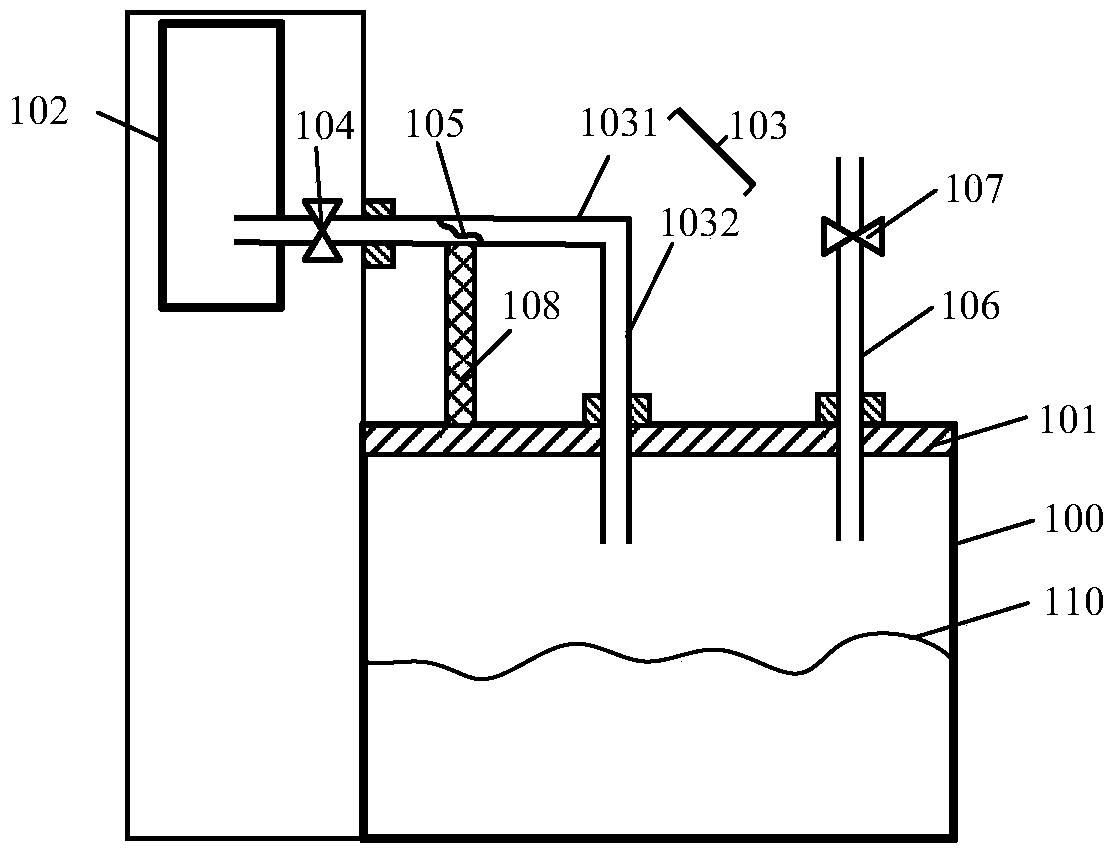

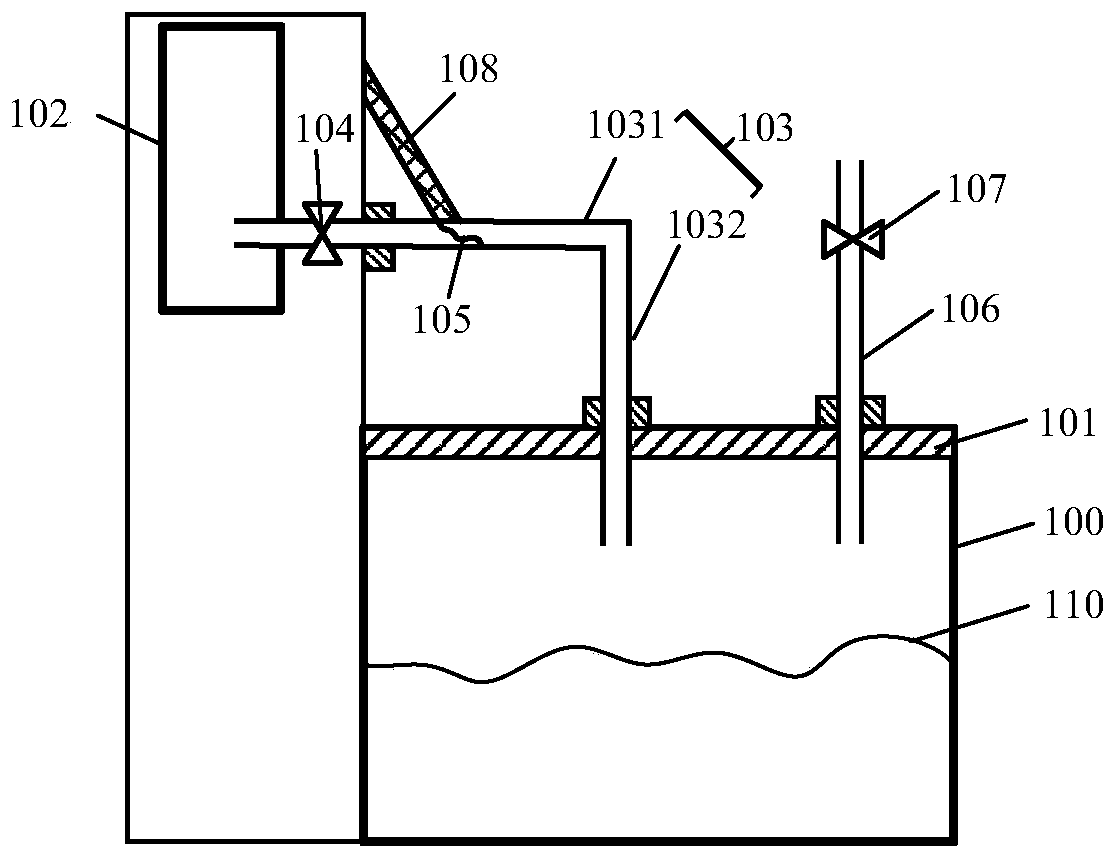

Groove type wet etching device

PendingCN111276431AAvoid deformationConcentration reachedSemiconductor/solid-state device manufacturingThermodynamicsProcess engineering

The invention discloses a groove type wet etching device. The device comprises a process tank and at least one acid liquor supply tank, a connecting duct and a support member, wherein the position ofthe process tank is lower than that of the acid liquor supply tank; wherein the acid liquor supply tank is communicated with the process tank through a connecting pipeline; the connecting pipeline atleast comprises a transverse pipeline and a longitudinal pipeline which are connected; the inlet end of the transverse pipeline is connected with the acid liquor supply tank; wherein the outlet end ofthe longitudinal pipeline is connected with the process tank, the acid liquor supply tank is used for storing acid liquor and supplying the stored acid liquor into the process tank through the connecting pipeline, and the process tank is used for diluting the acid liquor supplied by the acid liquor supply tank or mixing a plurality of supplied acid liquors so as to carry out an etching process; and the supporting part is in contact with the transverse pipeline and is used for keeping the transverse pipeline horizontal. The groove type wet etching device ensures that the concentration of the acid can be kept stable after each time of acid change.

Owner:YANGTZE MEMORY TECH CO LTD

Preparation method of multi-patterned mask

ActiveCN106783557BOptimizing the etch processSmall difference in morphologySemiconductor/solid-state device manufacturingAmorphous siliconEngineering

The present invention relates to a multiple graphical mask preparation method. The method comprises: providing a semiconductor substrate, and forming a hard mask layer on the semiconductor substrate; forming an amorphous silicon layer and a first polycrystalline silicon layer which are overlapped in order on part of the hard mask layer; forming a side lurch around the amorphous silicon layer and the first polycrystalline silicon layer; forming stress layers on the hard mask layer, the side wall and the amorphous silicon layer; performing heat annealing process of the semiconductor substrate, converting the amorphous silicon layer to a second polycrystalline silicon layer, wherein the width of the second polycrystalline silicon layer is larger than the width of the first polycrystalline silicon layer; and removing the second polycrystalline silicon layer, the stress layers and the first polycrystalline silicon layer. In the invention, the multiple graphical mask preparation method can reduce the morphology difference of the two side walls of the side wall so as to optimize the etching technology of the hard mark layer.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

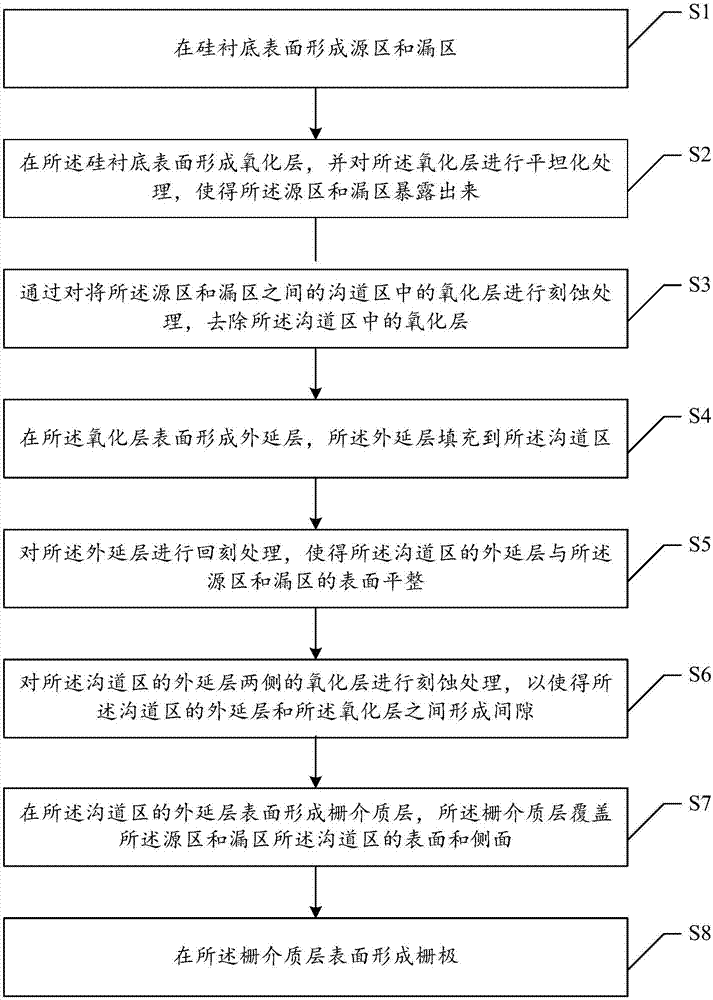

Fin field effect transistor and manufacturing method thereof

InactiveCN108010968AIncrease heightImprove current flow capacitySemiconductor/solid-state device manufacturingSemiconductor devicesOxideField-effect transistor

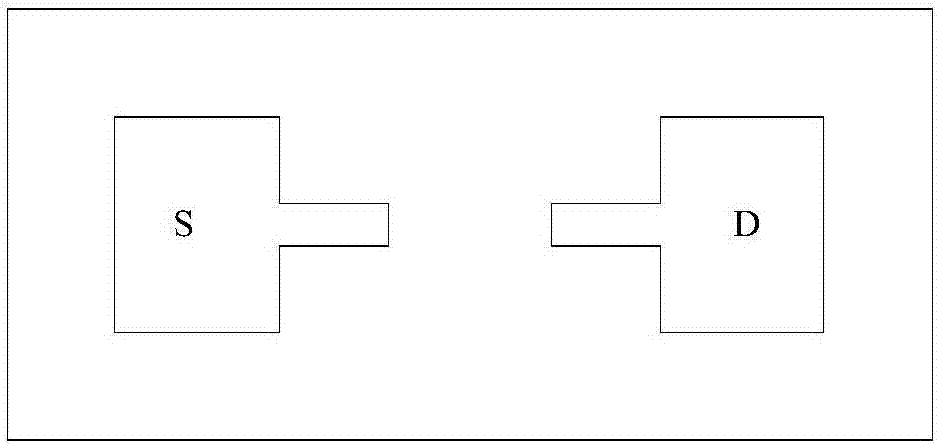

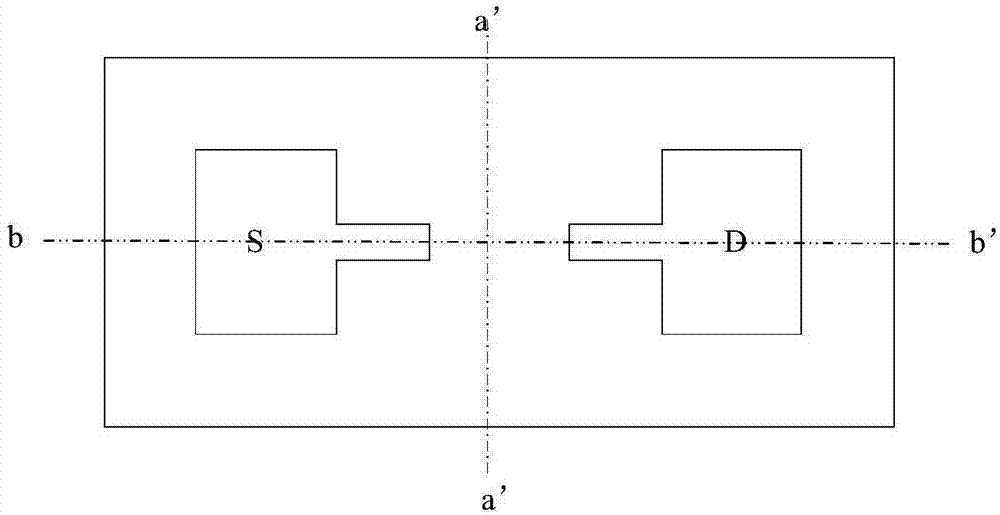

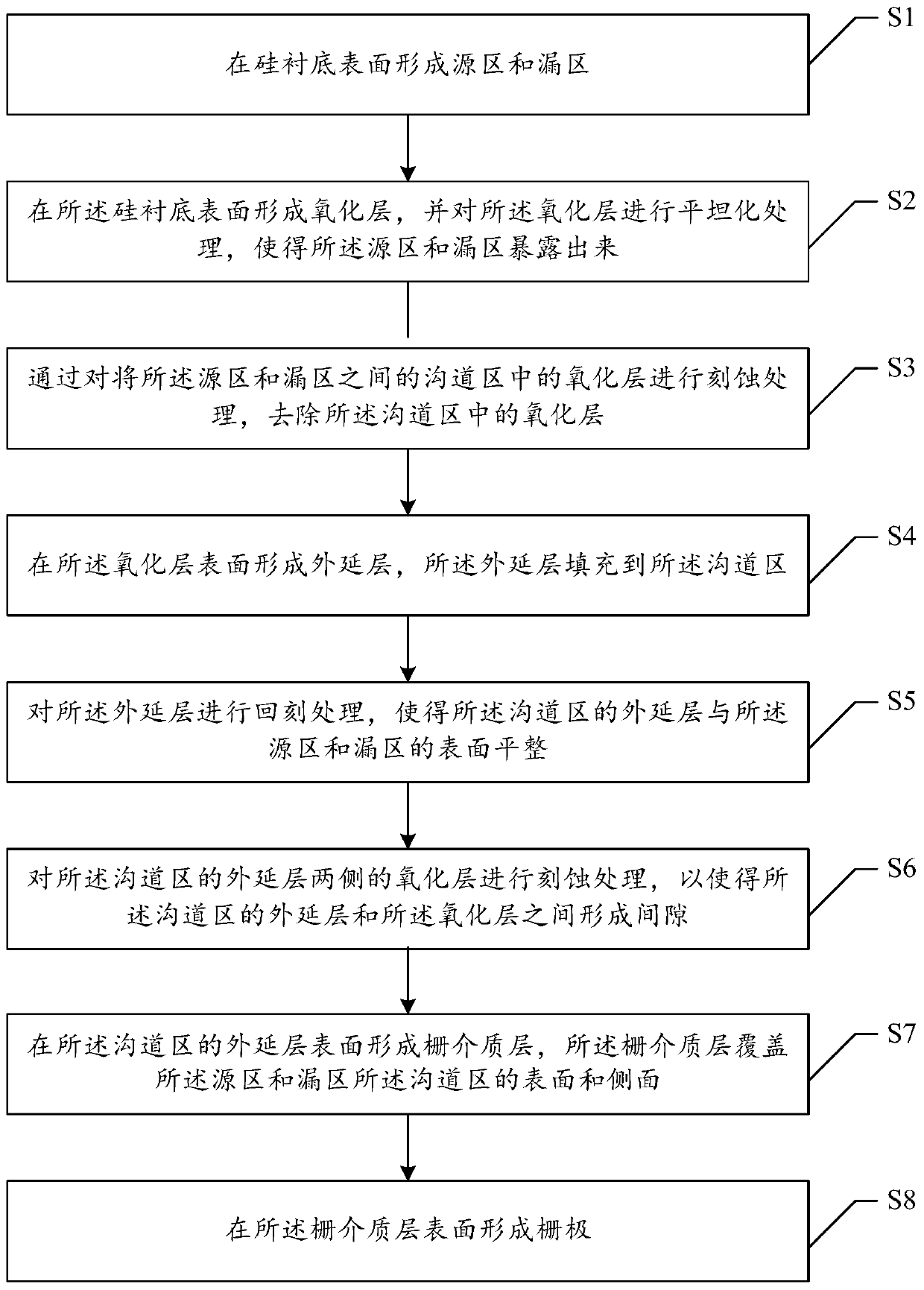

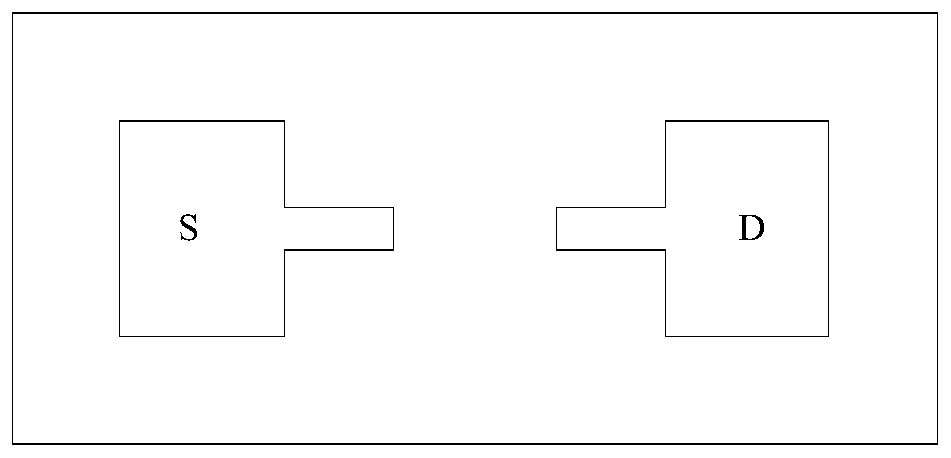

The invention provides a manufacturing method of a fin field effect transistor. The method includes: forming a source region and a drain region on the surface of a silicon substrate; forming an oxidelayer on the surface of the silicon substrate and performing planarization processing on the oxide layer to enable the source region and the drain region to be exposed; etching the oxide layer in a channel region between the source region and the drain region, and removing the oxide layer in the channel region; forming an epitaxial layer on the surface of the oxide layer, and performing etching-back processing on the epitaxial layer, wherein the channel region is filled with the epitaxial layer; etching the oxide layer at two sides of the epitaxial layer in the channel region; forming a gate dielectric layer on the surface of the epitaxial layer of the channel region, wherein the gate dielectric layer covers the source region, the drain region and the channel region; and forming a gate onthe surface of the gate dielectric layer. The invention also provides a fin field effect transistor manufactured by employing the above method.

Owner:NANJING LISHUI HIGH-TECH VENTURE CAPITAL MANAGEMENT CO LTD

Fin field effect transistor and manufacturing method thereof

InactiveCN108010968BGuaranteed performanceImprove flatnessSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricPhysical chemistry

The invention provides a manufacturing method of a fin field effect transistor. The method includes: forming a source region and a drain region on the surface of a silicon substrate; forming an oxidelayer on the surface of the silicon substrate and performing planarization processing on the oxide layer to enable the source region and the drain region to be exposed; etching the oxide layer in a channel region between the source region and the drain region, and removing the oxide layer in the channel region; forming an epitaxial layer on the surface of the oxide layer, and performing etching-back processing on the epitaxial layer, wherein the channel region is filled with the epitaxial layer; etching the oxide layer at two sides of the epitaxial layer in the channel region; forming a gate dielectric layer on the surface of the epitaxial layer of the channel region, wherein the gate dielectric layer covers the source region, the drain region and the channel region; and forming a gate onthe surface of the gate dielectric layer. The invention also provides a fin field effect transistor manufactured by employing the above method.

Owner:NANJING LISHUI HIGH-TECH VENTURE CAPITAL MANAGEMENT CO LTD

Method for electroplating circuit board

InactiveCN108966517AOptimizing the etch processShorten the production cyclePrinted element electric connection formationCopper platingOptoelectronics

The invention provides a method for electroplating a circuit board. After cleaning and activating a substrate after forming holes, the surface of the substrate and the inner walls of the holes are sprayed with a coating of the charged dopant substance by an ion implantation process, the coated substrate is cleaned, and then copper plating is performed on the coating by VCP plating, so that the thickness of the surface copper and the thickness of the hole copper electroplated on the circuit board are uniform, the extreme difference is reduced, the requirements of fine circuit fabrication are satisfied, and the surface copper base meeting requirements is provided for making fine circuit patterns on the circuit board, which is more conducive to the etching process of the circuit board, improves the yield of the product, and also avoids the need for the copper reduction process when the copper surface of the flash plating and VCP plating is too thick. The circuit board production cycle isgreatly shortened and the production cost is lowered.

Owner:PEKING UNIV FOUNDER GRP CO LTD +1

Display device contact hole forming method

ActiveCN102683266BRemove defects with poor uniformity controlAvoid over etchingSemiconductor/solid-state device manufacturingDisplay devicePartial thickness

The embodiment of the invention discloses a display device contact hole forming method which includes the following steps of: providing a substrate on which a first metal layer, an insulating layer, a second metal layer, a passivated layer and a patterning photoresist layer are sequentially formed; performing a first etching step to remove the entire thickness of the passivated layer and the partial thickness of the insulating layer above the first metal layer, and at the same time to remove the partial thickness of the corresponding halftone photoresist above the second metal layer; performing an ashing step to totally remove the corresponding halftone photoresist above the second metal layer; and performing a second etching step to remove the insulating layer retained in a deep hole above the first metal layer so as to expose the surface of the first metal layer and at the same time to remove the passivated layer retained in a shallow hole above the second metal layer so as to expose the surface of the second metal layer. The scheme of the invention can overcome the disadvantage that the uniformity of the remnant film of the photoresist is difficult to control, and the etching processes are optimized; the process of controlling the etching speed is simple; and over etching of the metal wirings can be avoided to the largest extent.

Owner:SHANGHAI AVIC OPTOELECTRONICS