Method for embedding radio frequency chip into silicon cavity

A radio frequency chip and cavity technology, which is applied in the field of embedding radio frequency chips in silicon cavities, can solve the problems of uneven bottom, difference, unfavorable chip grounding interconnection, etc., and achieves increased height and flatness, efficient contact, etching, etc. The effect of process optimization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 2

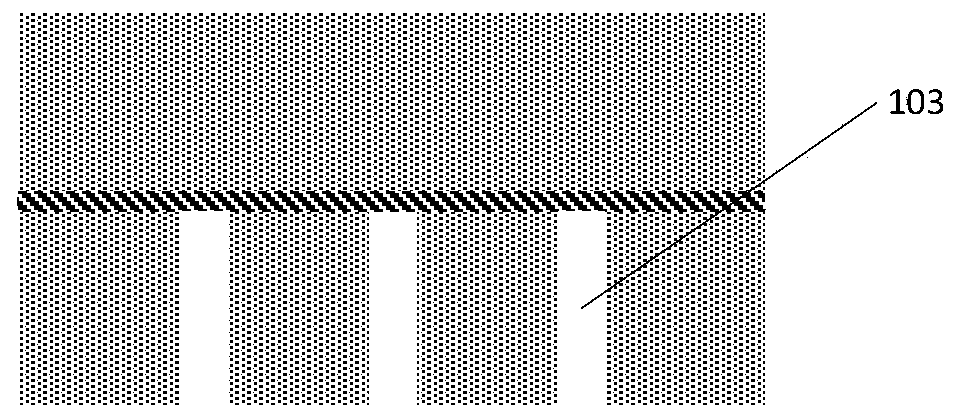

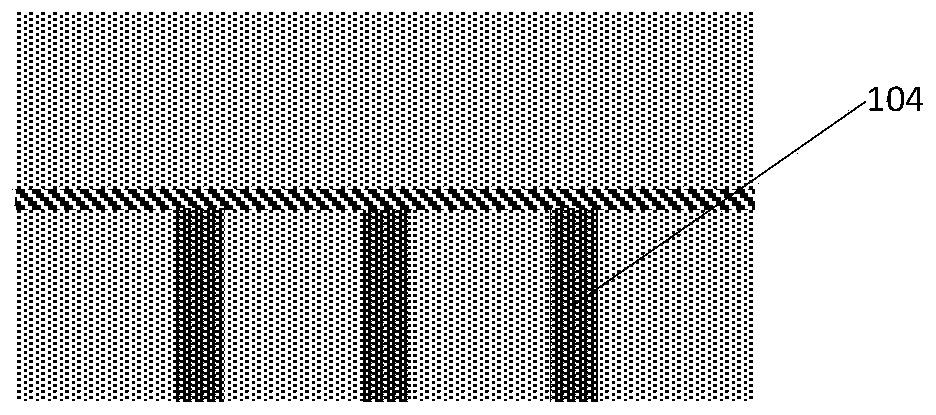

[0040] like Figure 9 to Figure 14 As shown, the difference between embodiment 2 and embodiment 1 is that the TSV hole 103 in step 101) is first etched to stay in the SOI layer 102, and then the etching is continued with ventilation so that the bottom of the TSV passes through the SOI layer 102. Other processes are the same. details as follows:

[0041] A method for embedding a radio frequency chip in a silicon cavity, specifically comprising the steps of:

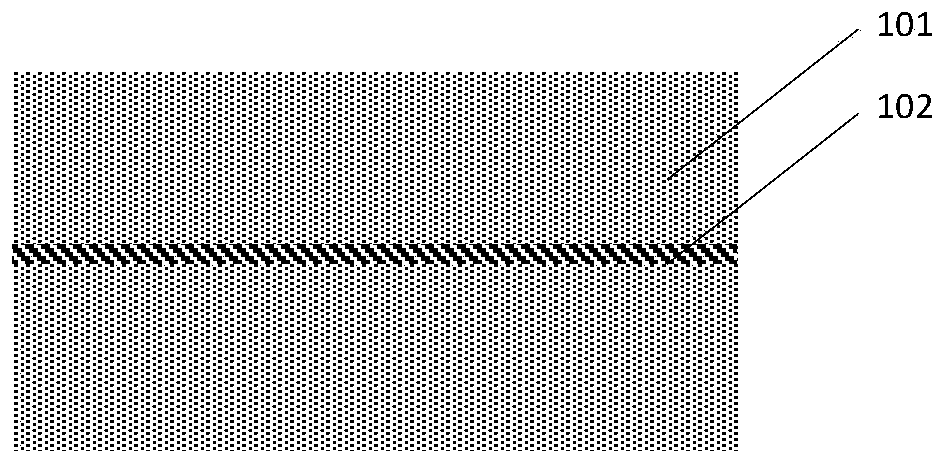

[0042]101) Metal pillar forming step: making TSV holes 103 on the lower surface of the carrier plate 101 with the SOI layer 102 through photolithography and etching processes. The diameter range of the TSV holes 103 is between 1um and 1000um, and the depth is between 10um and 1000um . Wherein, the TSV hole 103 is firstly etched to stay in the SOI layer 102 , and then continues to etch through ventilation so that the bottom of the TSV passes through the SOI layer 102 .

[0043] Deposit silicon oxide or silicon nitride o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More