Semiconductor embedded mixed packaging structure, and manufacturing method of the same

A technology of hybrid packaging and packaging structure, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve the problems that hinder the development of miniaturization of semiconductor packaging device assembly, complex solder reflow process control, and occupation of circuit boards. Surface area and other issues, to achieve the effect of reducing the assembly area, releasing the surface area, and reducing circulation and transfer

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0078] The preferred embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings, so that the advantages and features of the present invention can be more easily understood by those skilled in the art, so as to define the protection scope of the present invention more clearly.

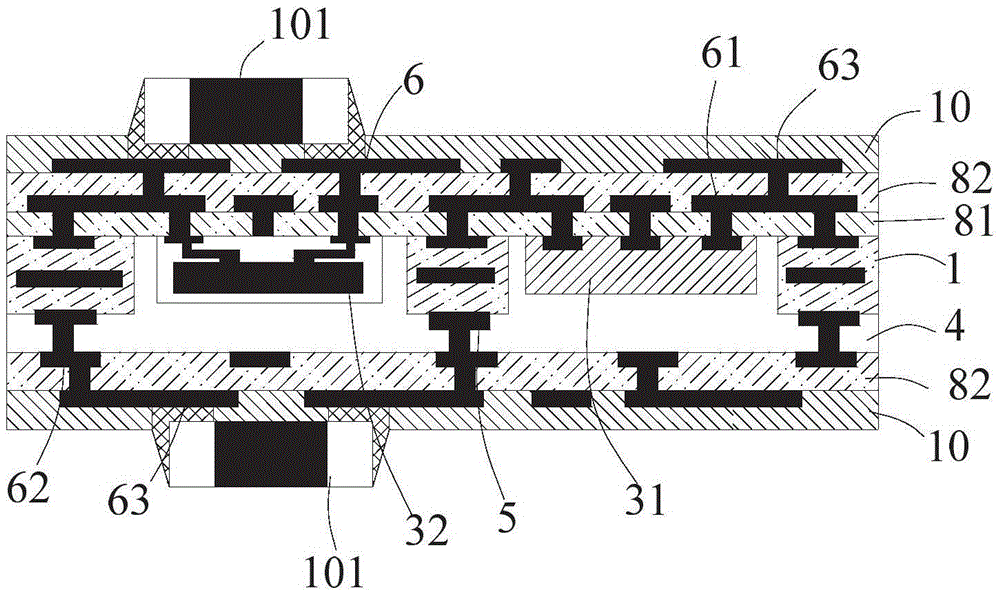

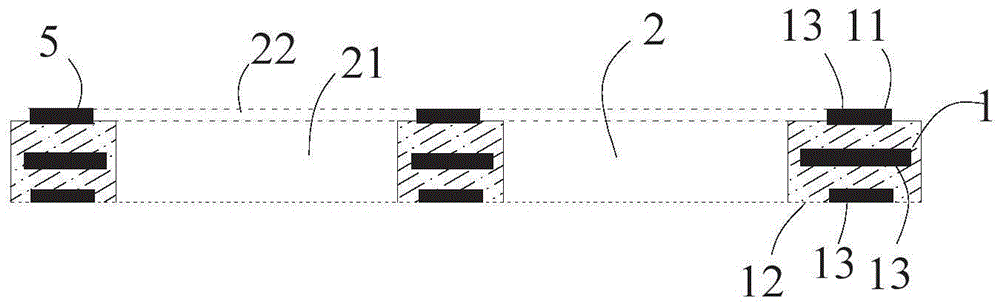

[0079] Semiconductor embedded hybrid package structure in a specific embodiment of the present invention, refer to figure 1 As shown, the package structure specifically includes:

[0080] Circuit board 1, that is, a circuit carrier for packaging semiconductor chips (Bare Die) and semiconductor chip packages (Semiconductor Package), which has a first surface 11 and a second surface 12 arranged oppositely;

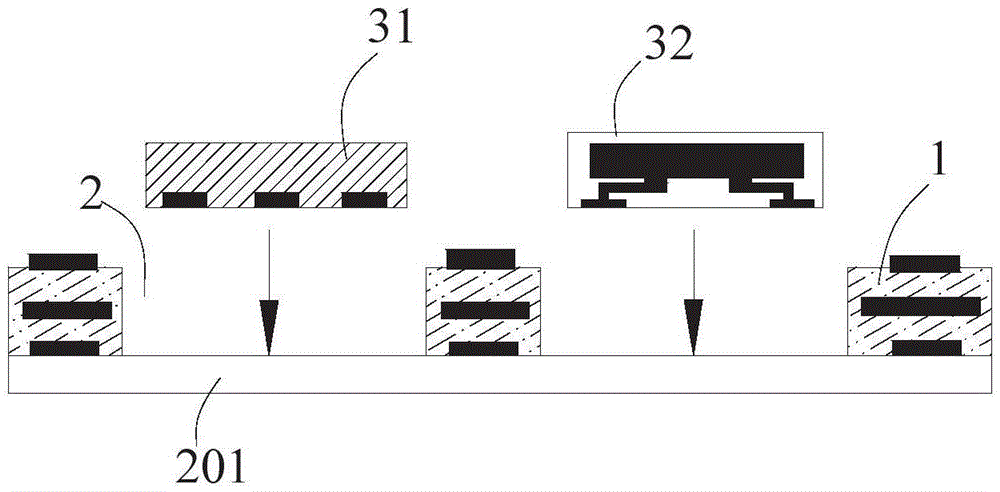

[0081] At least one opening or cavity 2 for accommodating the semiconductor chip 31 and at least one semiconductor chip package 32 provided in the circuit board 1;

[0082] A semiconductor chip 31 and a semiconductor chip package 32 disposed i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More