Three-dimensional storage and formation method therefor

A memory, three-dimensional technology, which is applied in the manufacture of electric solid-state devices, semiconductor devices, and semiconductor/solid-state devices, etc., can solve the problems of reducing chip space utilization, large size, and complicated manufacturing process of flash memory storage units, and improve space utilization. , the effect of simplifying the process and reducing the volume

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] As mentioned in the background art, the manufacturing process of the existing three-dimensional NAND flash storage unit is complicated and the volume is large, which will reduce the space utilization rate of the chip.

[0029] Combining with a three-dimensional NAND gate flash storage unit, the reason why the manufacturing process of the three-dimensional NAND flash storage unit is complicated and the volume is large is analyzed.

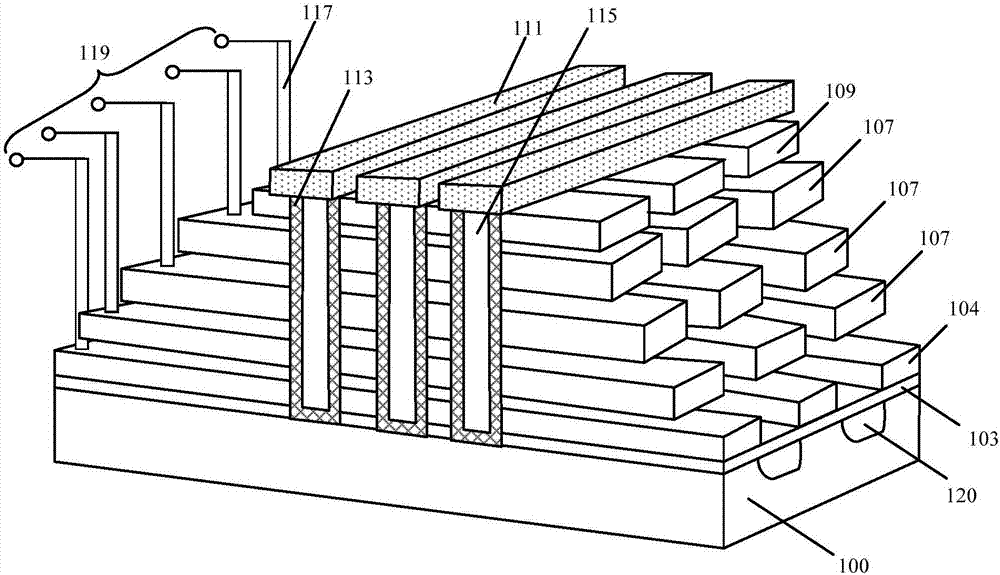

[0030] Please refer to figure 1 , figure 1 It is a structural schematic diagram of an existing three-dimensional NAND gate flash storage unit, including: a substrate 100; an isolation layer 103 located on the surface of the substrate 100; a bottom selection gate 104 located on the surface of the isolation layer 103; Several layers of overlapping control gates 107 on the gate 104; a top selection gate 109 located on the control gate 107; The source line doped region 120 in the bottom; the channel via hole (not marked) passing through the top...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More