Patents

Literature

1276results about How to "Achieve electrical connection" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

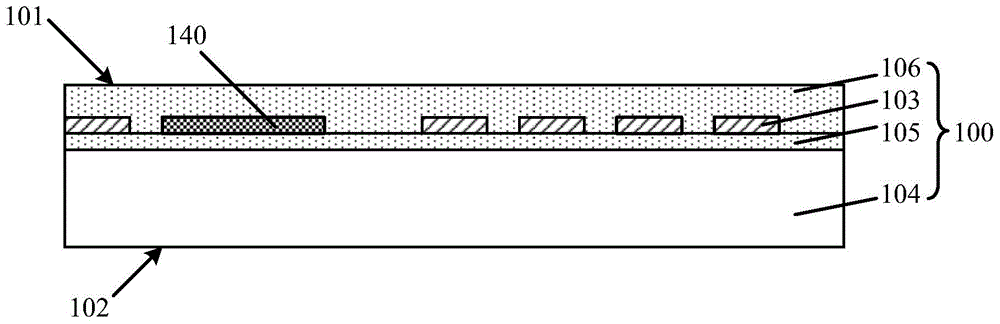

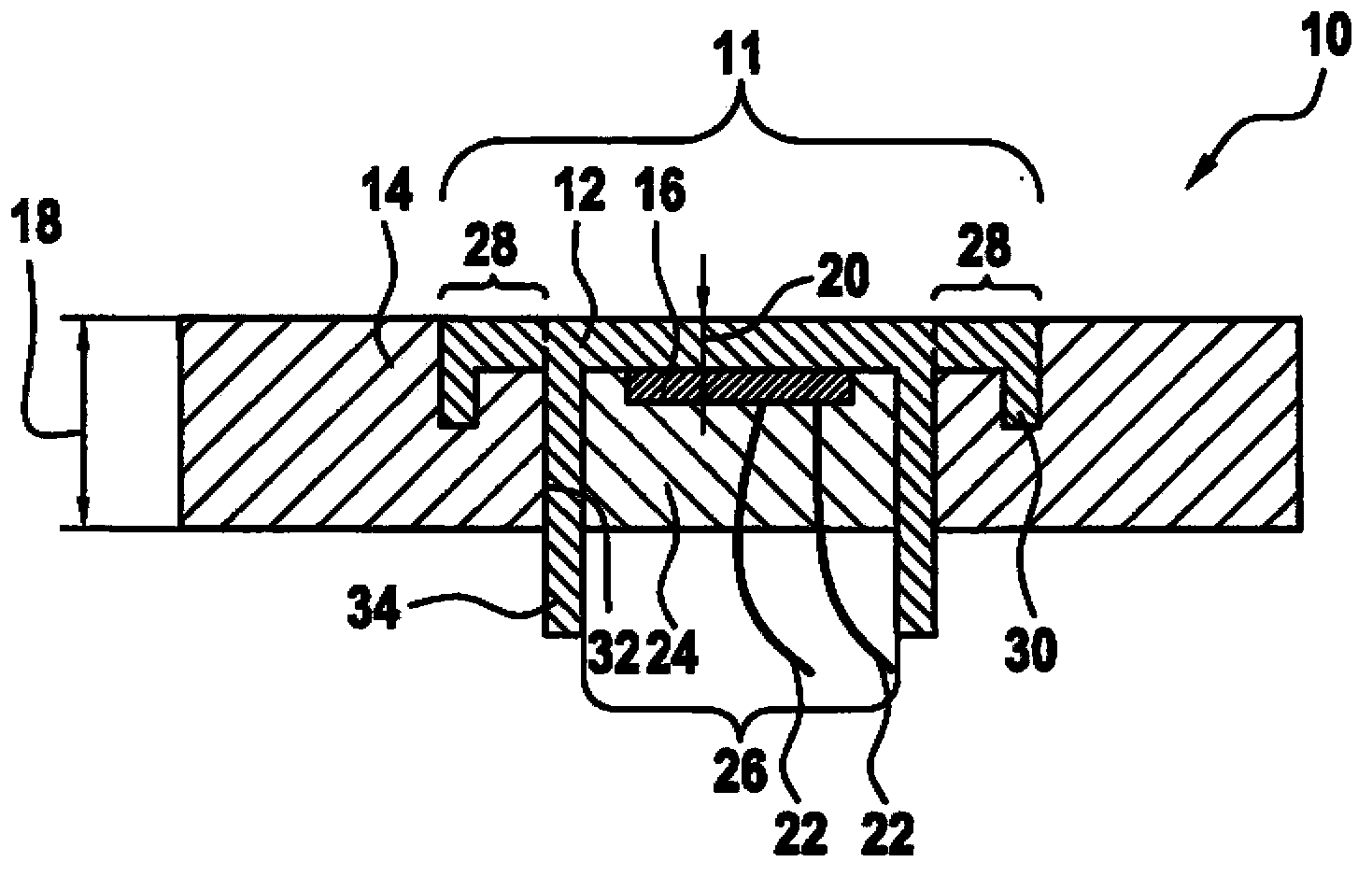

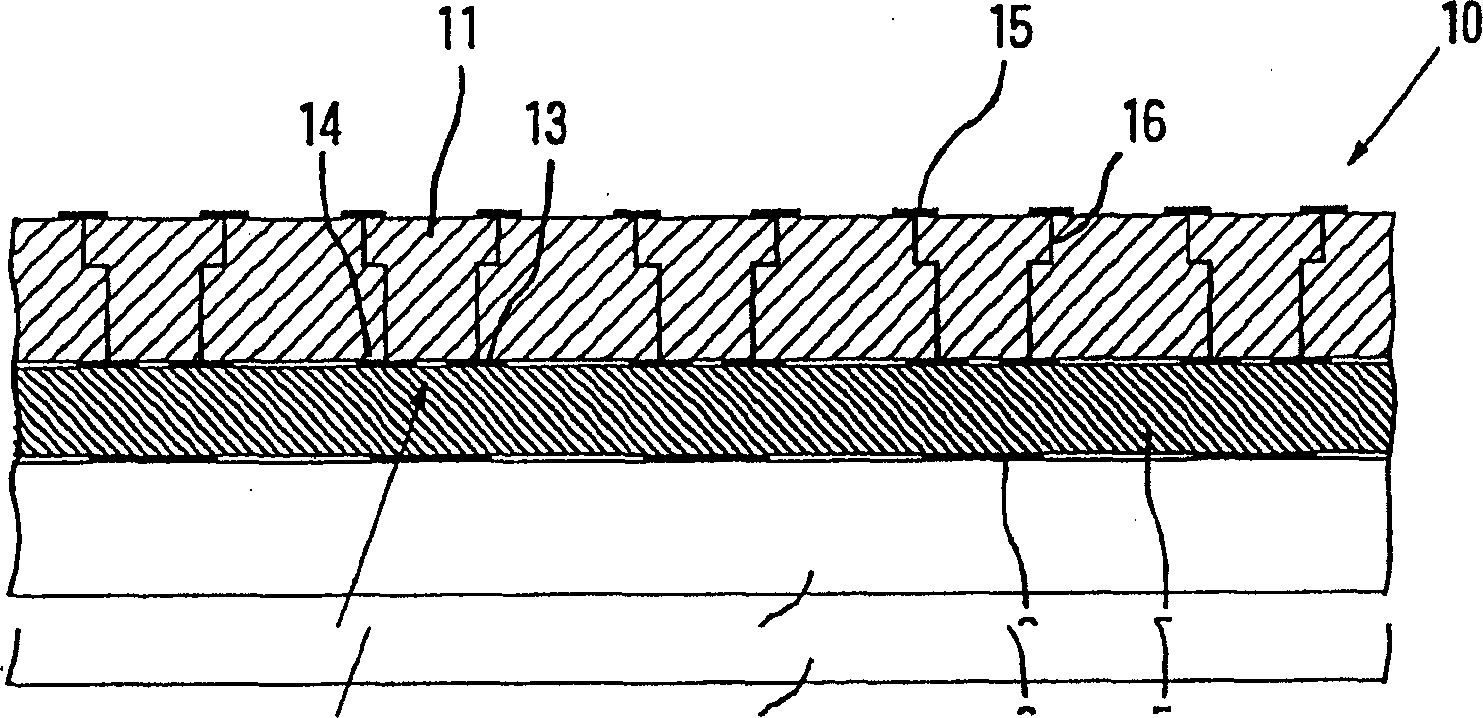

Wafer-level fingerprint recognition chip packaging structure and method

InactiveCN104201115ASimplify the packaging processReduce damageMeasurement apparatus componentsSemiconductor/solid-state device detailsFingerprintComputer science

Disclosed is a wafer-level fingerprint recognition chip packaging structure and method. The method includes: providing a substrate which comprises a plurality of induction chip areas and is provided with a first surface and a second surface opposite to the first surface, wherein a first surface of each induction chip area comprises an induction area; forming a covering layer on the first surface of the substrate; forming a plug structure in each induction chip area of the substrate, wherein one end of each plug structure is electrically connected with the corresponding induction area, and the other end of each plug structure is exposed out of the second surface of the substrate. By the forming method, the packaging process of a fingerprint recognition chip can be simplified, the requirement on sensitivity of the induction chip is lowered, and the packaging method is wider in application.

Owner:CHINA WAFER LEVEL CSP

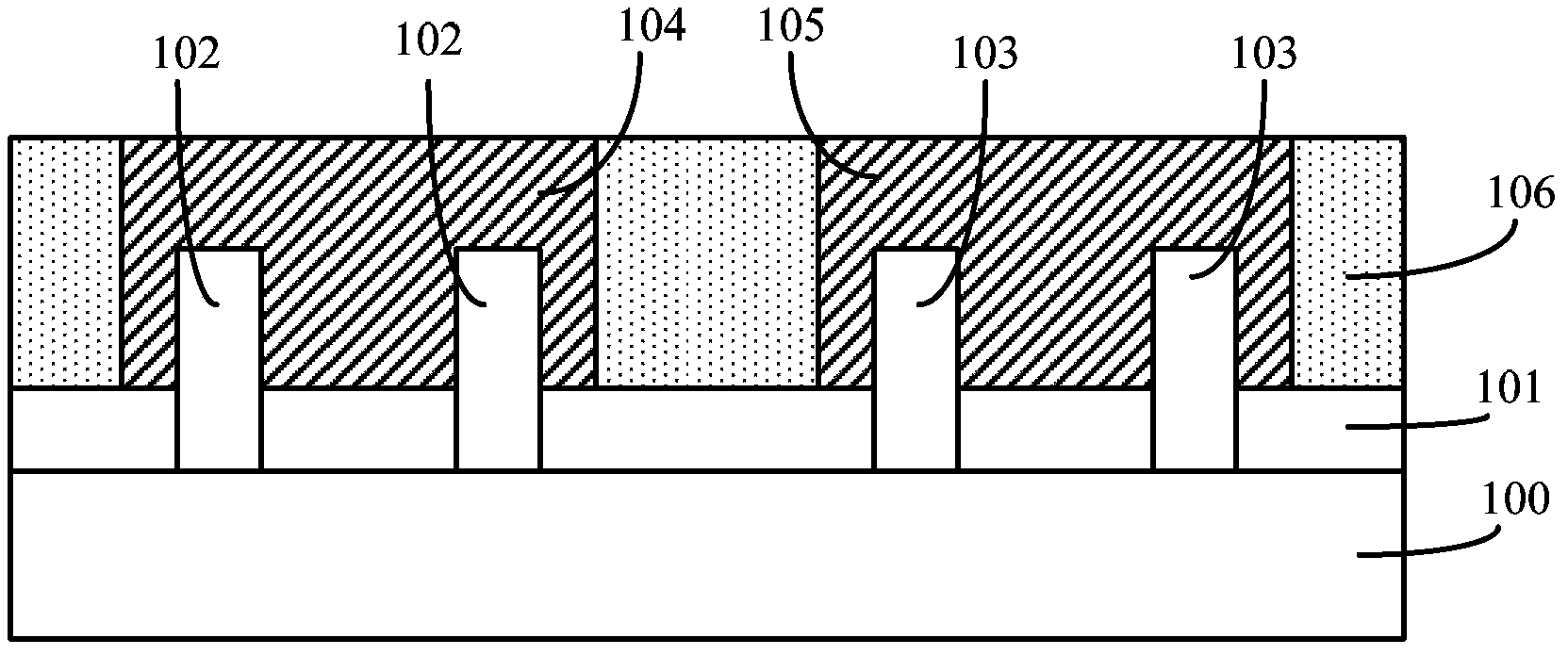

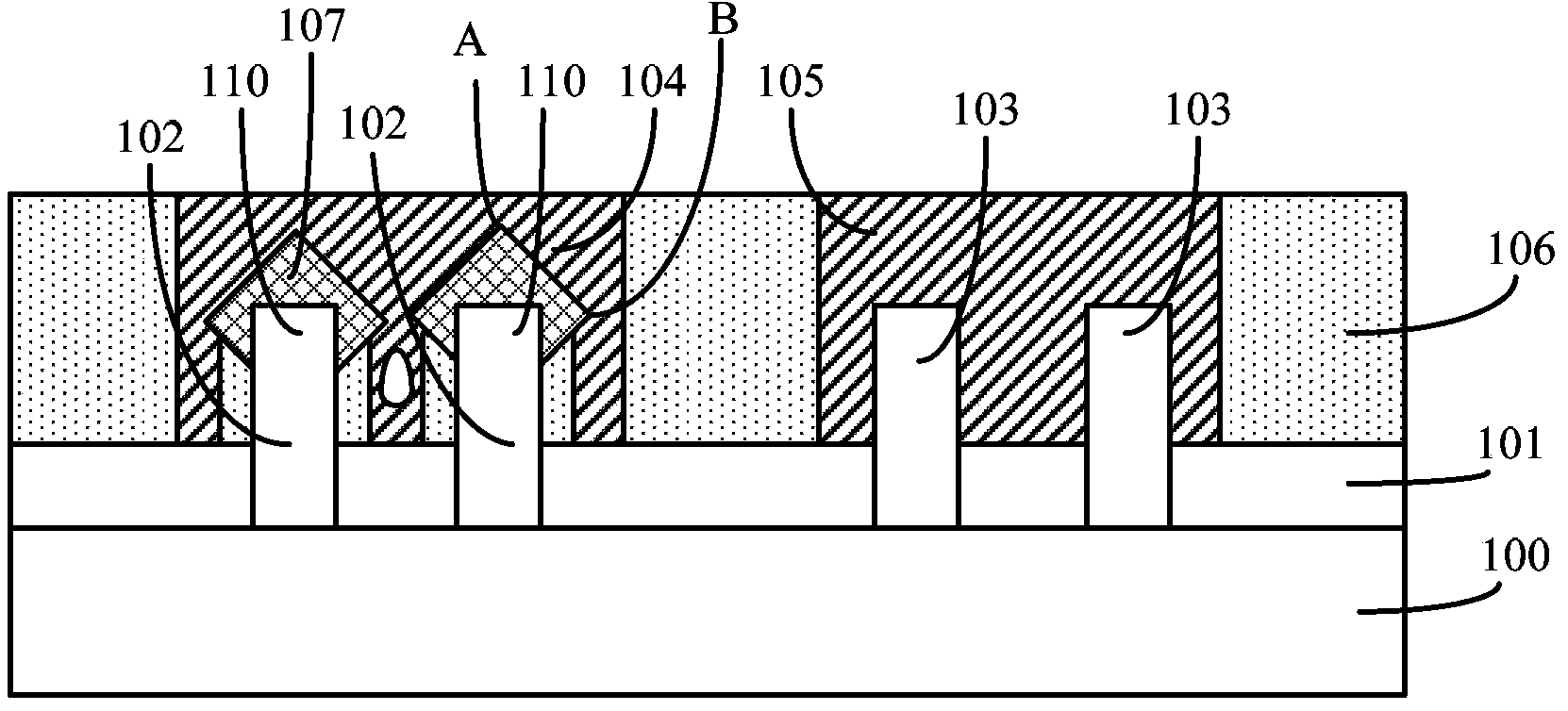

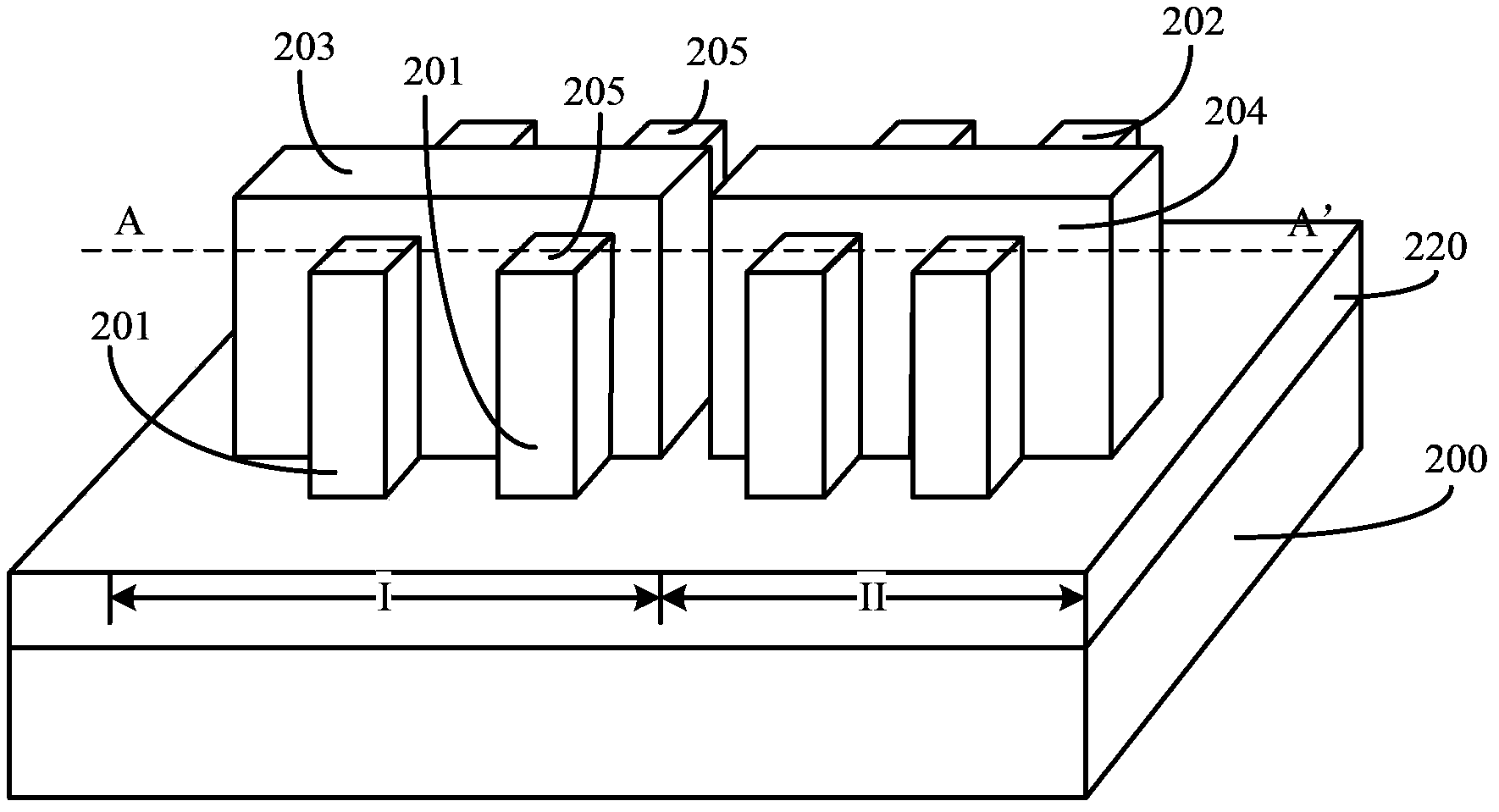

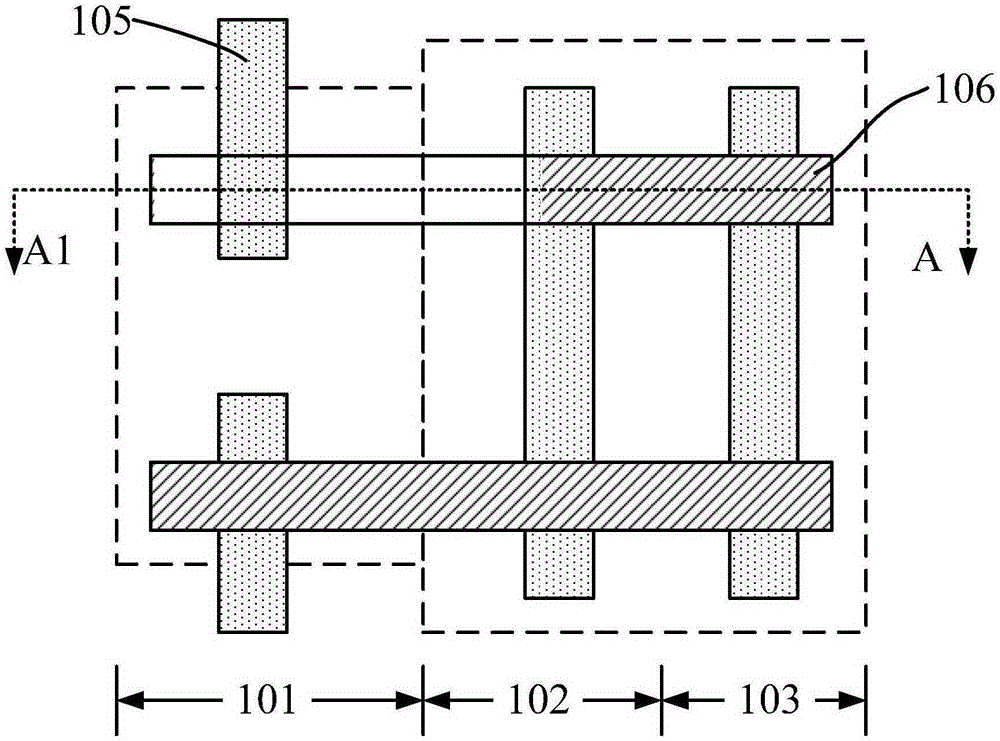

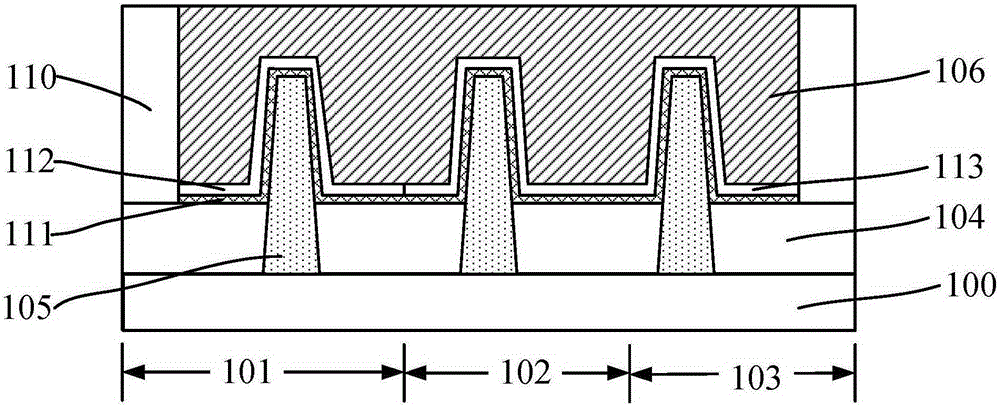

Semiconductor structure and forming method thereof

ActiveCN104124174AIncrease distanceGuaranteed mobilityTransistorSemiconductor/solid-state device manufacturingSemiconductor structureEngineering

Provided are a semiconductor structure and a forming method thereof. The forming method comprises the steps that a semiconductor layer is formed in a source region and a drain region of a first fin part, covers the top surface and part of the side wall surface of the first fin part and is provided with protruded first ridge corners and second ridge corners, the first ridge corners are located on the top surface of the first pin part, and the second ridge corners are located on the surface of a side wall of the first fin part; a barrier layer is formed on a substrate, the first fin part and the surface of the semiconductor layer and fills a space between the adjacent second ridge corners, so that the adjacent second ridge corners are connected through the barrier layer; a dielectric layer is formed on the surface of the barrier layer, a first opening in the dielectric layer is exposed out of the barrier layer on the surfaces of at least two adjacent first ridge corners, the position of a side wall of the first opening in contact with the barrier layer is higher than the horizontal positions of the second ridge corners; the barrier layer at the bottom of the first opening is etched until the barrier layer is exposed out of the surface of the semiconductor layer, and a first conductive layer is formed on the surface of the semiconductor layer in the first opening. The performance of a formed semiconductor device is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

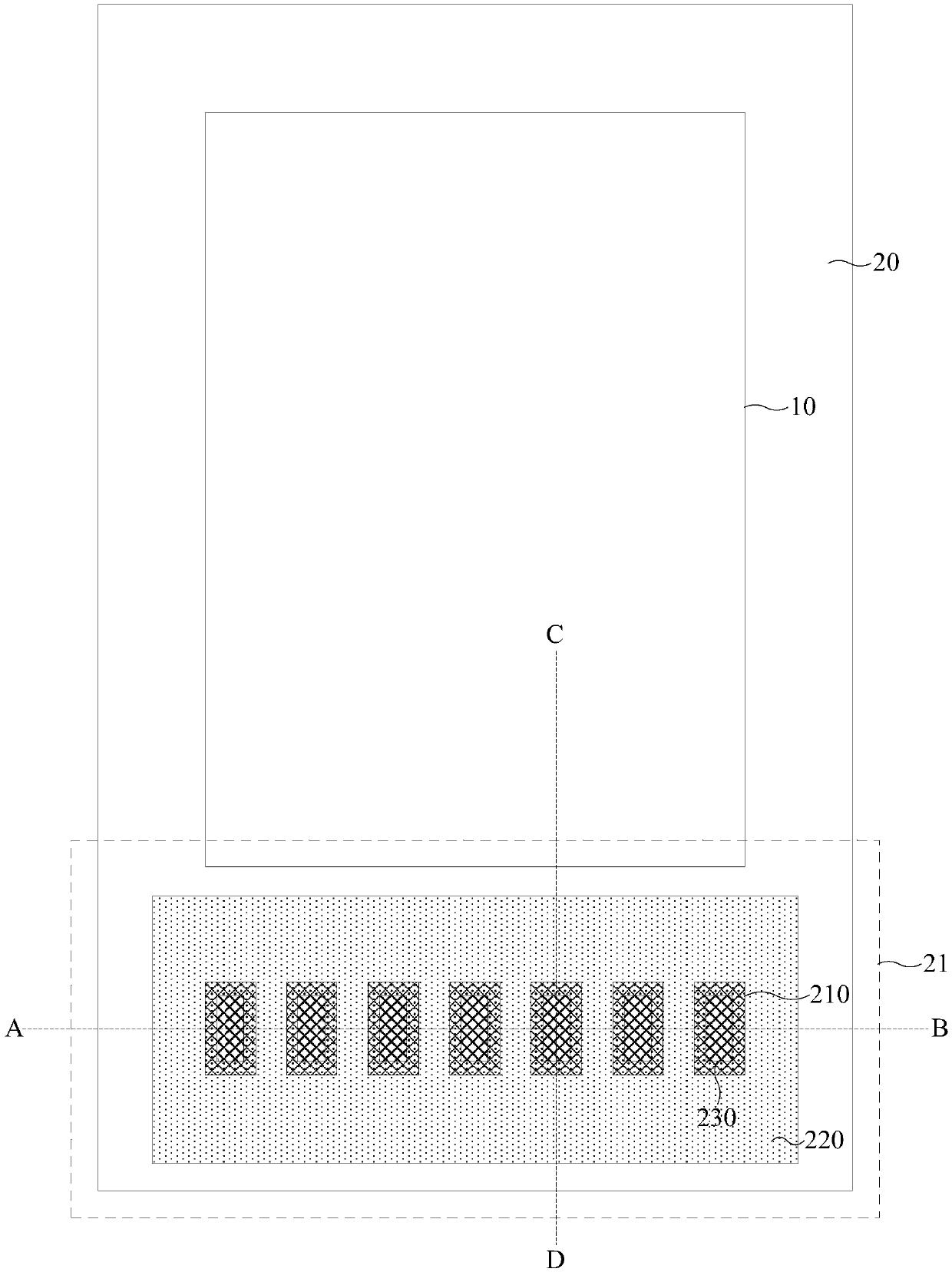

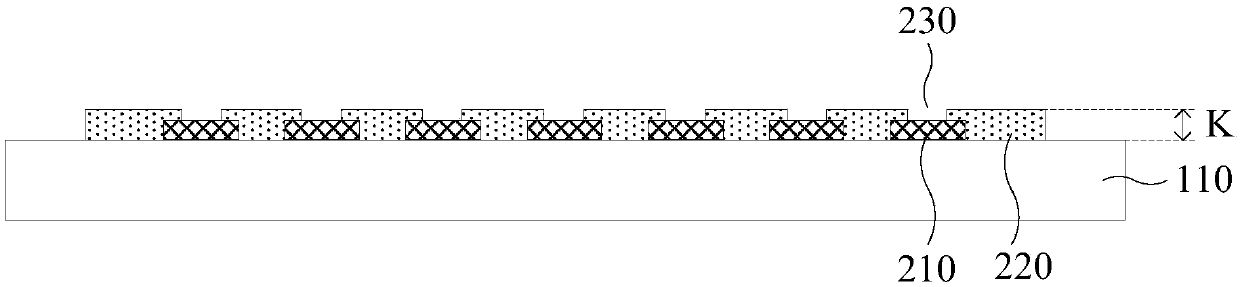

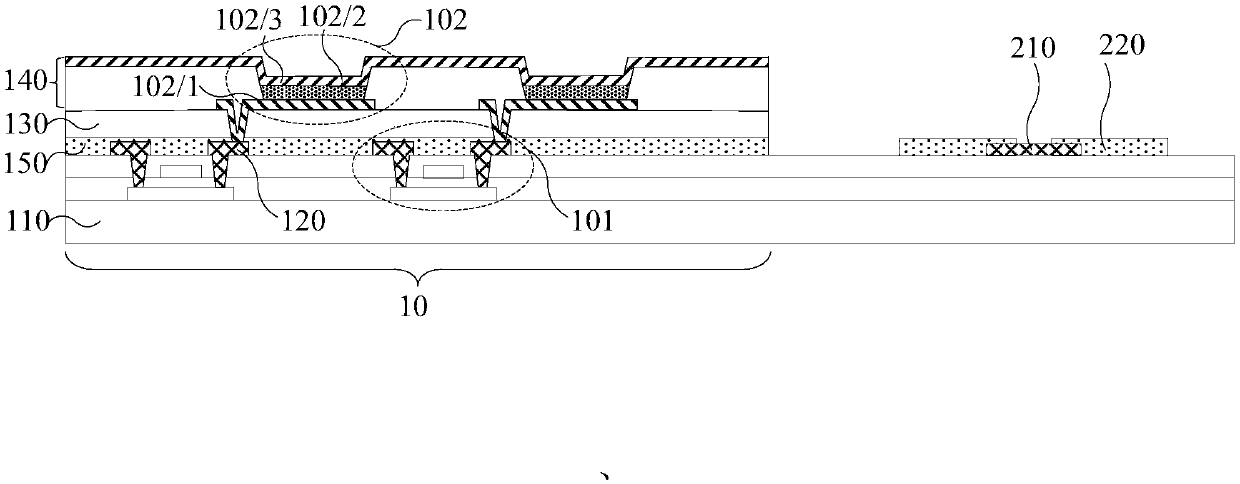

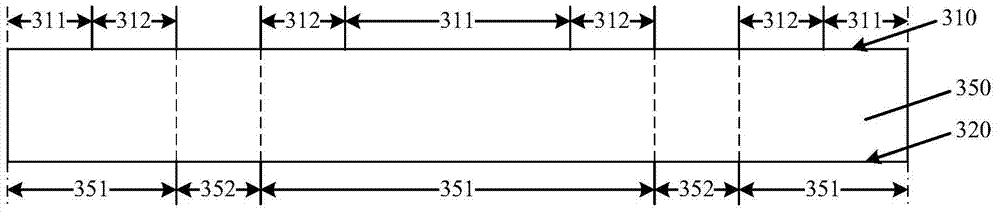

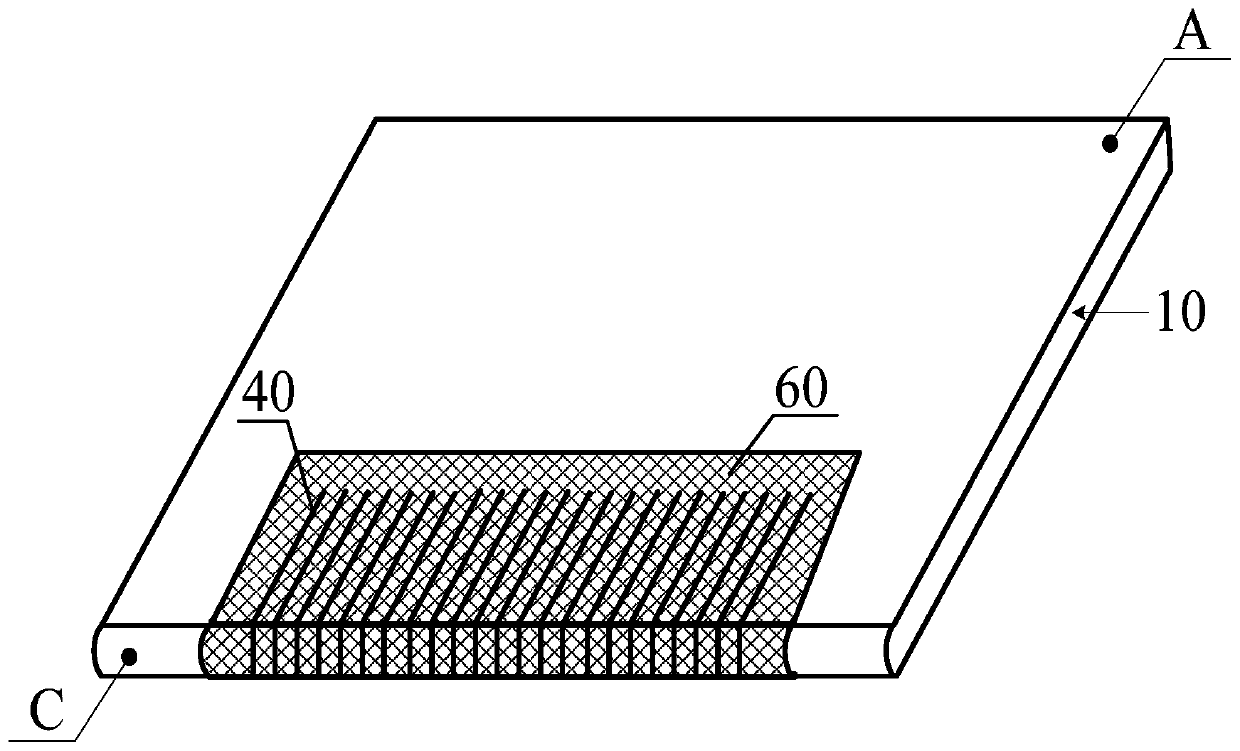

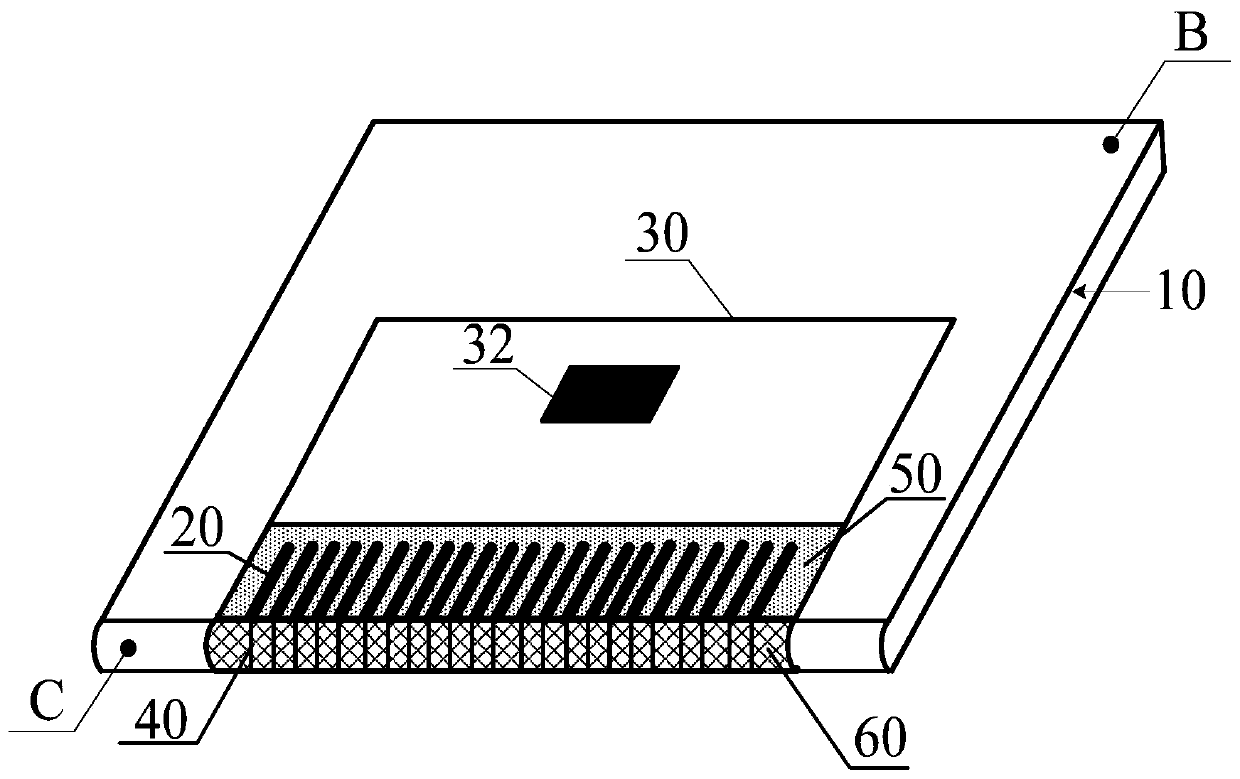

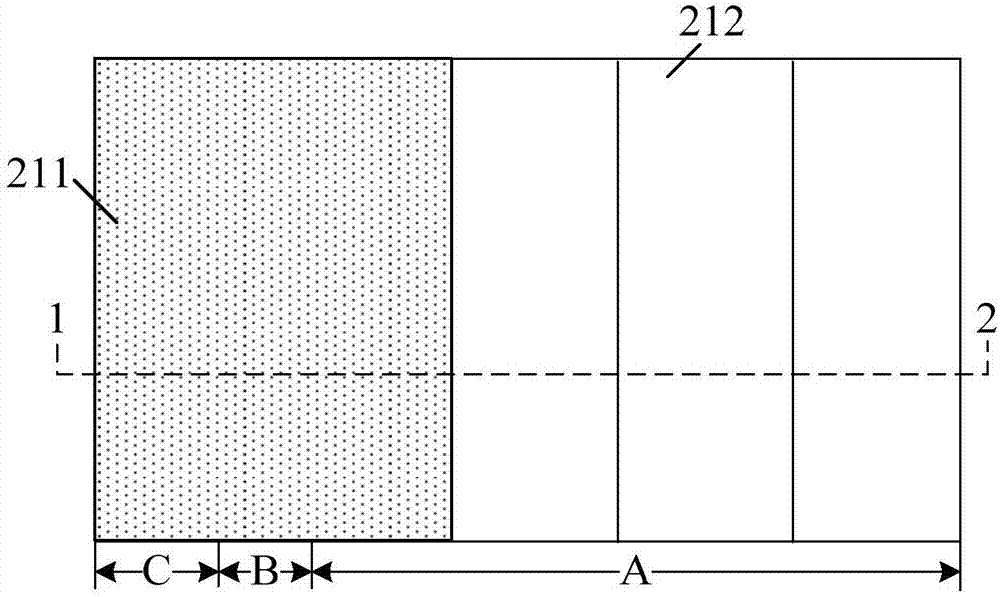

Array substrate, display panel and display device

InactiveCN109659304AAchieve electrical connectionEffective deformationSolid-state devicesNon-linear opticsElectrical connectionDisplay device

The invention discloses an array substrate, a display panel and a display device. The array substrate includes a display area and a non-display area disposed around the display area; the non-display area includes a binding area arranged at one side of the display area, and the binding area is provided with a plurality of binding pads; the array substrate comprises a substrate, a protection layer is arranged at one sides, far away from the substrate, of the binding pads, the protection layer comprises a plurality openings which are in one-to-one correspondence with the binding pads, and the openings penetrate the partial surfaces, where the binding pads are exposed, of the protection layer; and the thickness value of the protection layer is in a range of 0.3-0.6[Mu]m. According to the technical scheme provided by the embodiment, when the flexible printed circuit board and the array substrate are subjected to alignment deviation, a gold finger and conducting particles between the corresponding binding pads still can generate effective deformation to achieve electrical connection of the gold finger and the corresponding binding pads.

Owner:EVERDISPLAY OPTRONICS (SHANGHAI) CO LTD

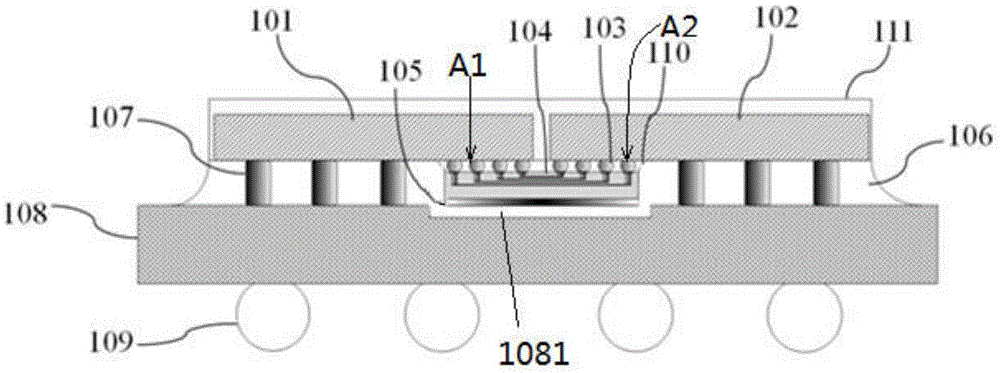

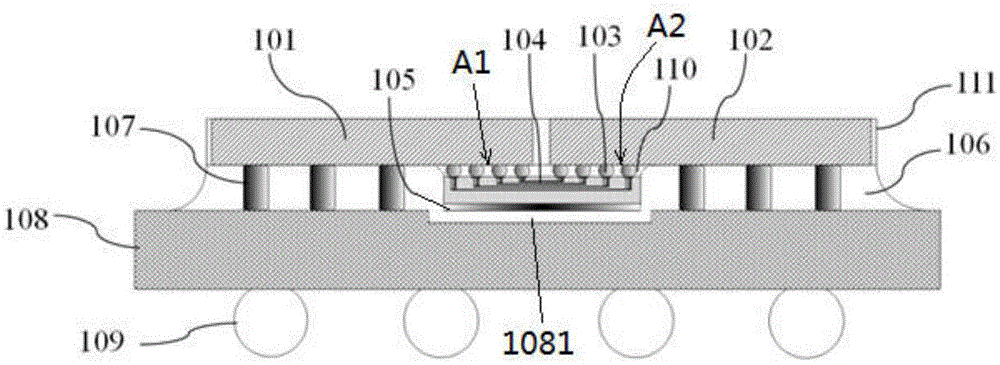

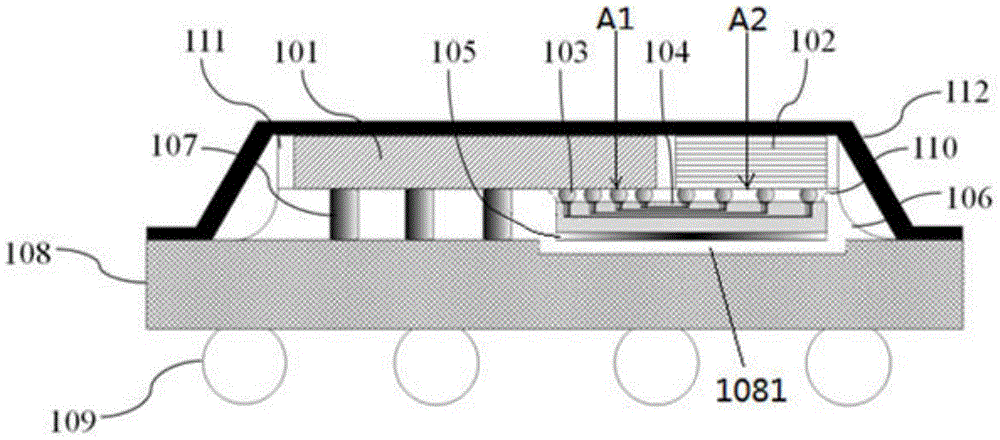

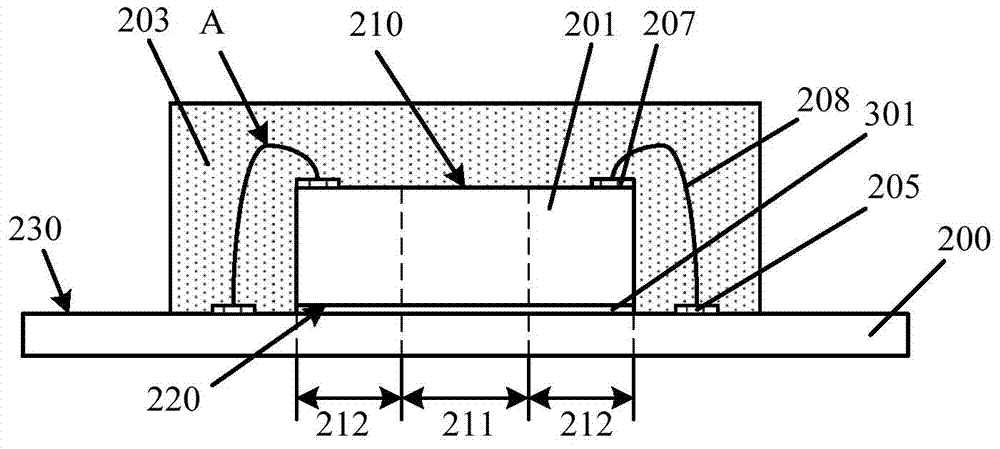

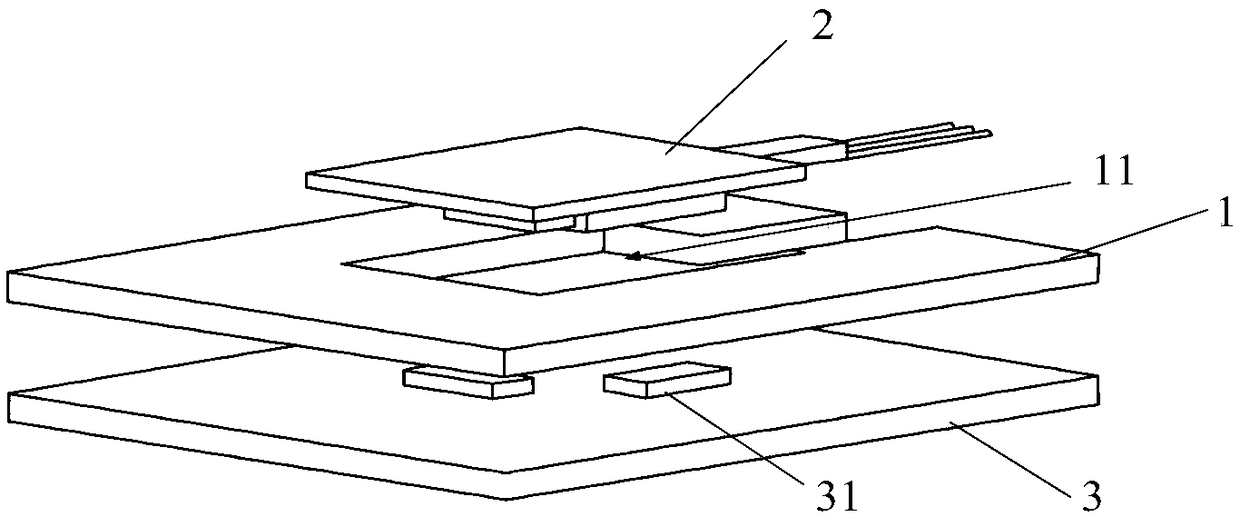

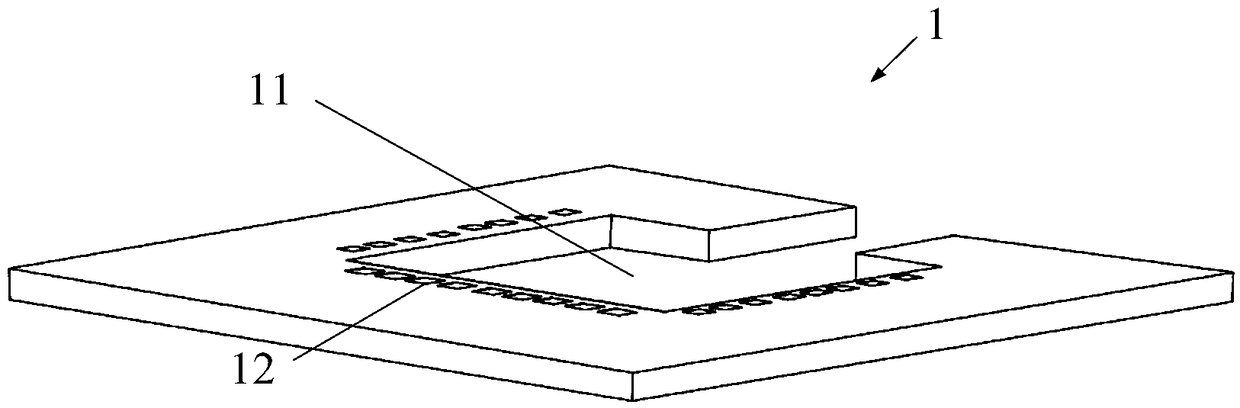

Encapsulation structure, electronic equipment and encapsulation method

ActiveCN105655310ASimple preparation processLow costSemiconductor/solid-state device detailsSolid-state devicesMiniaturizationElectrical connection

The invention discloses an encapsulation structure which comprises a substrate, a fan-out unit and a wiring layer, wherein the fan-out unit comprises a first chip and a second chip; the first chip comprises a first pin array; the second chip comprises a second pin array; the fan-out unit also comprises a third pin array; the first pin array, the second pin array and the third pin array are opposite to the substrate; the wiring layer is bridged between the first pin array and the second pin array and used for connecting the first pins in the first pin array to corresponding second pin in the second pin array; the substrate is provided with a welding pad electrically connected with the wiring layer in the substrate; the third pin array is connected with the welding pad. The invention also discloses electronic equipment and an encapsulation method. The encapsulation structure disclosed by the invention has the advantages of low difficulty in production, low cost and miniaturization.

Owner:HUAWEI TECH CO LTD

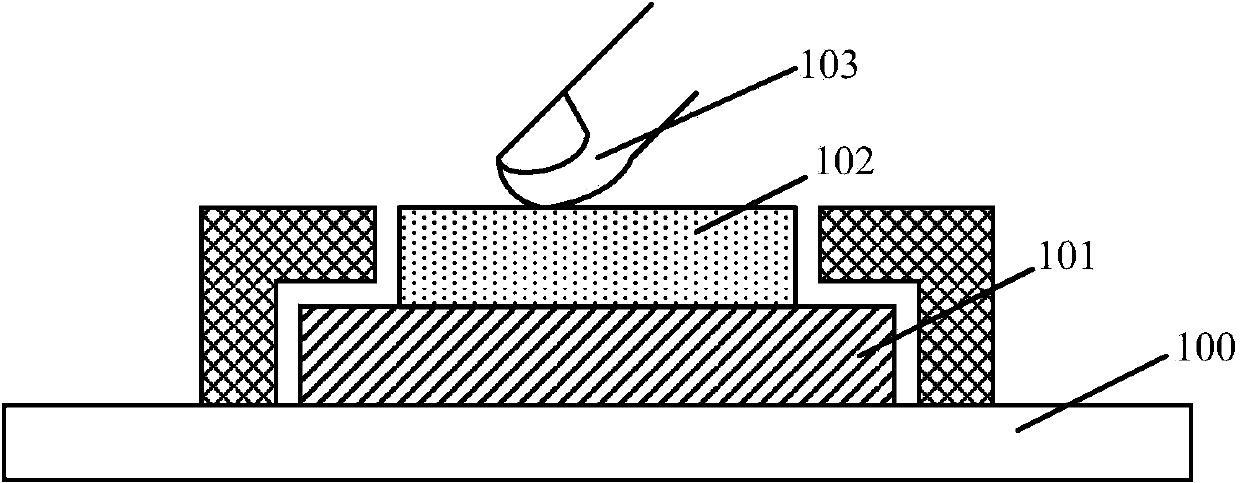

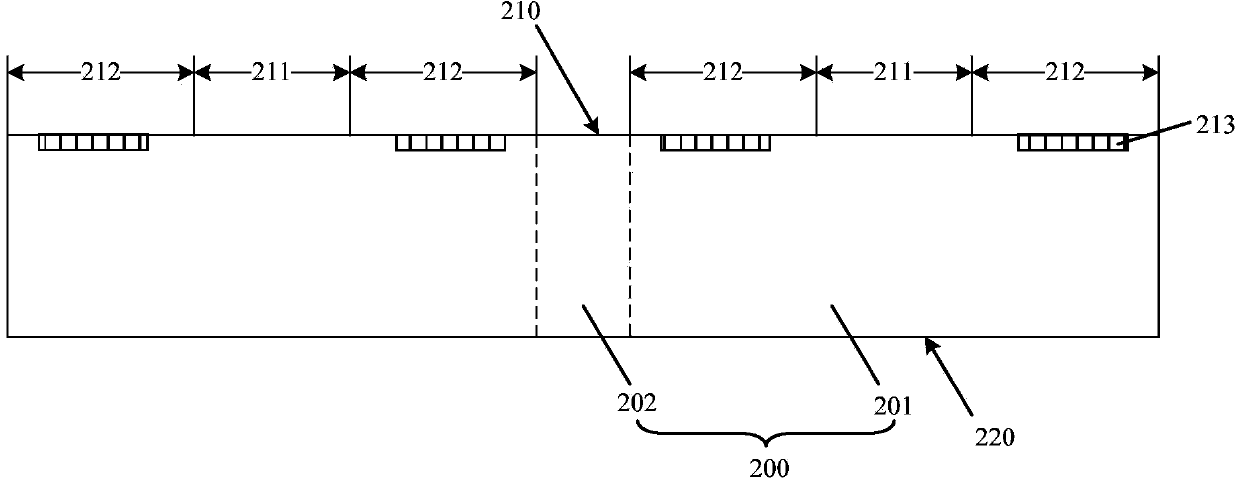

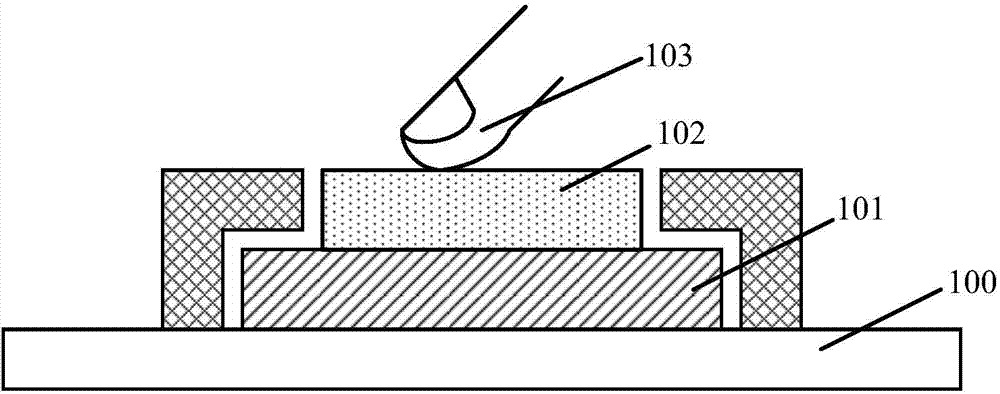

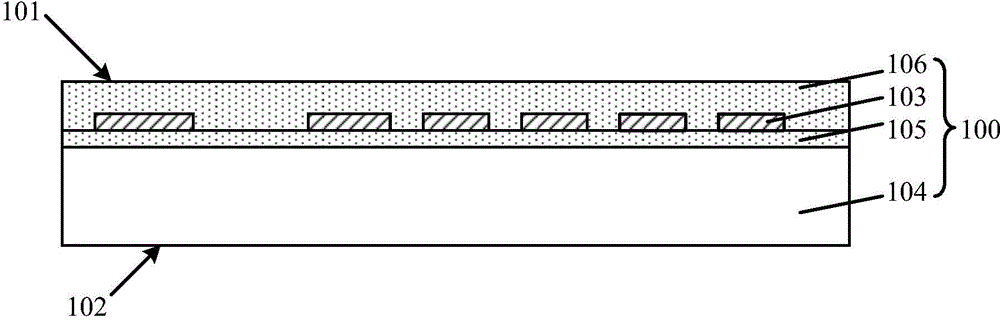

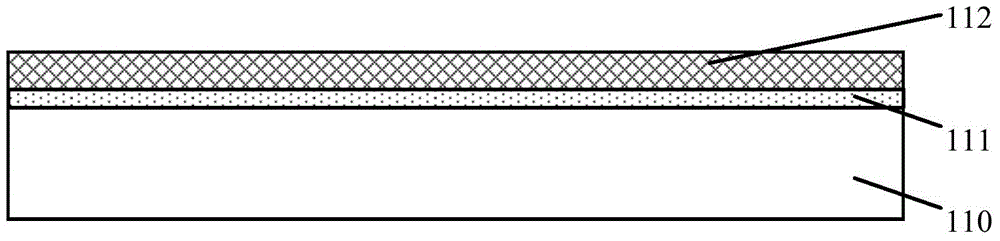

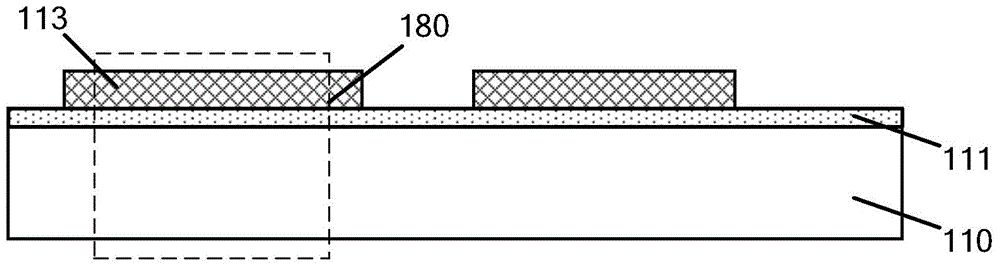

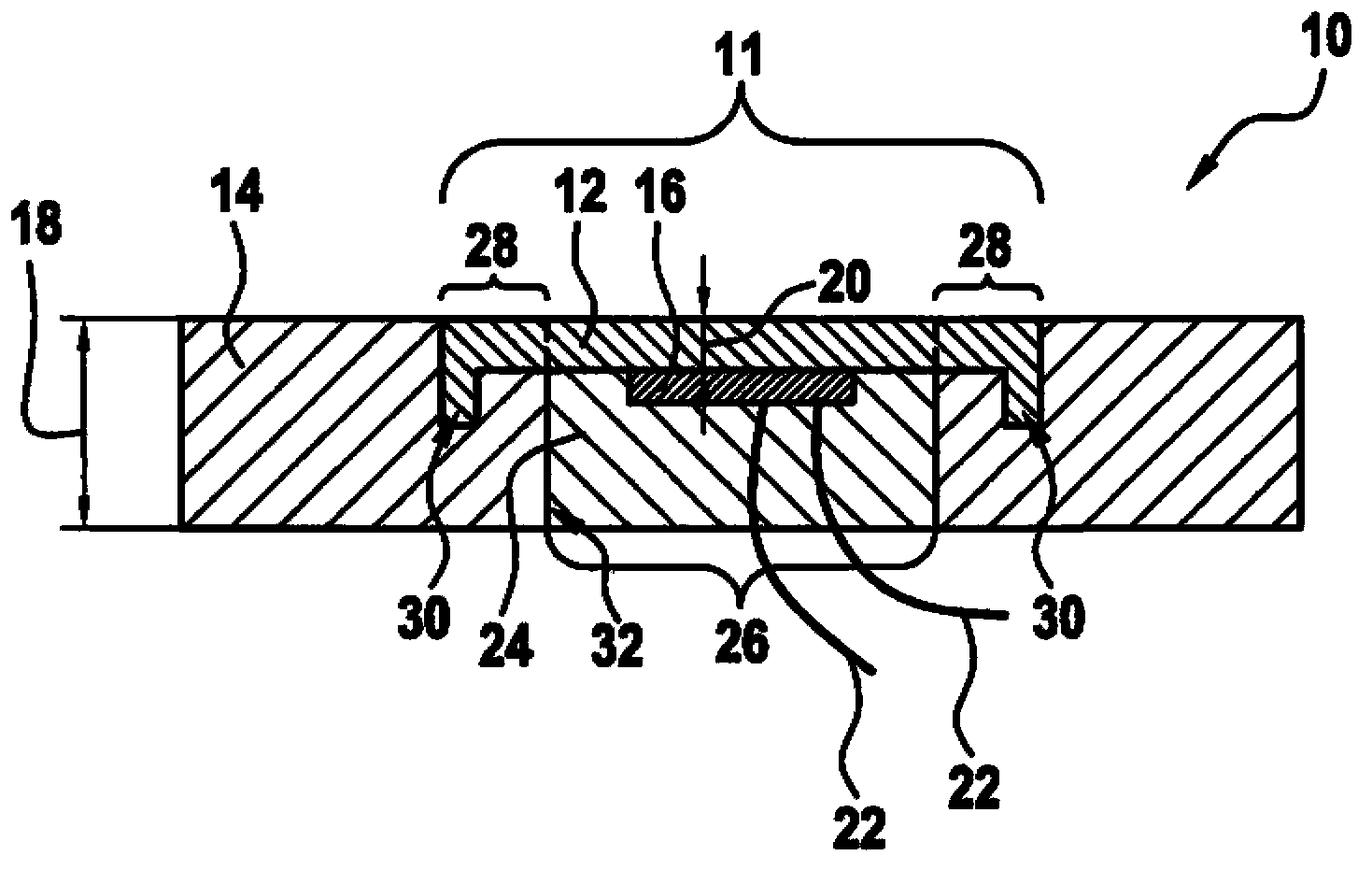

Fingerprint identification chip packaging structure and packaging method

InactiveCN104851853AHigh sensitivityReduce thicknessSemiconductor/solid-state device detailsSolid-state devicesPlastic packagingFingerprint

The invention provides a fingerprint identification chip packaging structure and a packaging method. The packaging method comprises the steps that a substrate is provided; an induction chip is coupled at the surface of the substrate, the induction chip is provided with a first surface and a second surface which is opposite to the first surface, the second surface of the induction chip is arranged at the surface of the substrate, the first surface of the induction chip comprises induction areas and peripheral areas surrounding the induction areas, grooves are formed in the peripheral areas, the surfaces of the side walls and the bottom parts of the grooves and the surface of the peripheral areas are provided with re-wiring layers, and the side walls of the induction chip are exposed out of the grooves; and a plastic packaging layer is formed at the surface of the substrate, the plastic packaging layer surrounds the induction chip, the plastic packaging layer fills the grooves, and the plastic packaging layer is exposed out of the surface of the induction areas. Sensitivity of the induction chip in the packaging structure is enhanced, and the size of the packaging structure is reduced.

Owner:CHINA WAFER LEVEL CSP

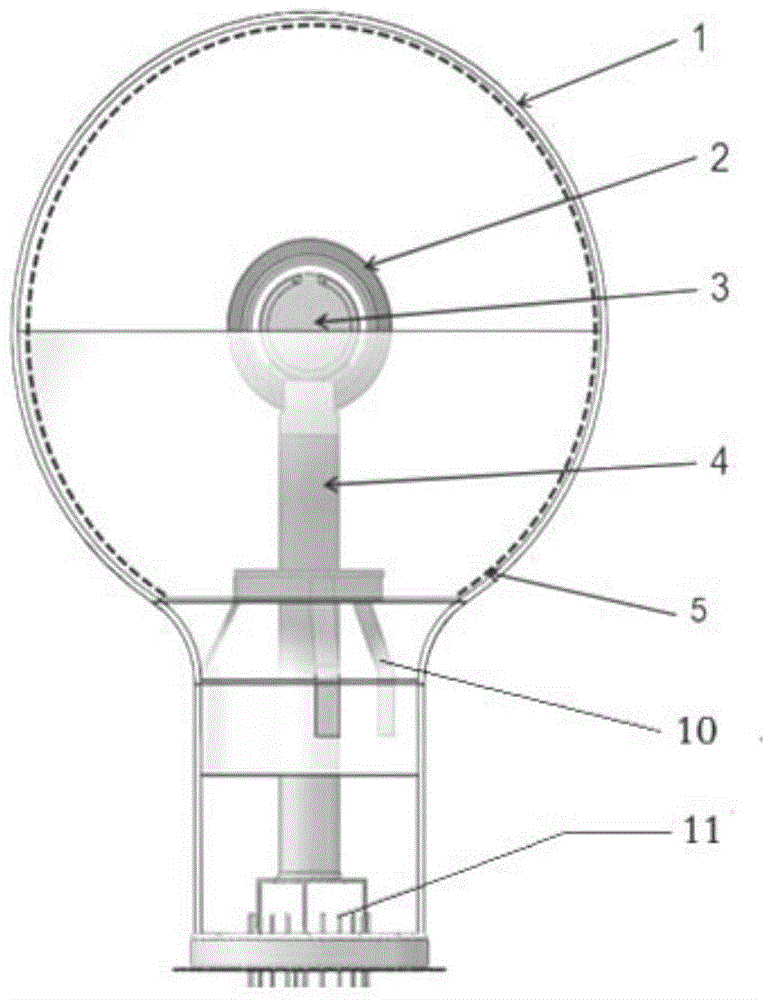

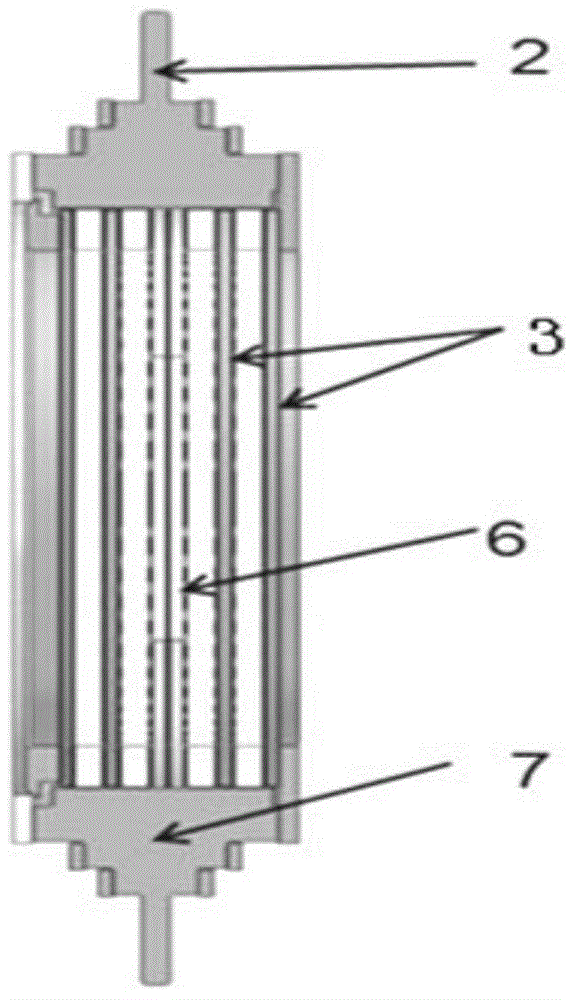

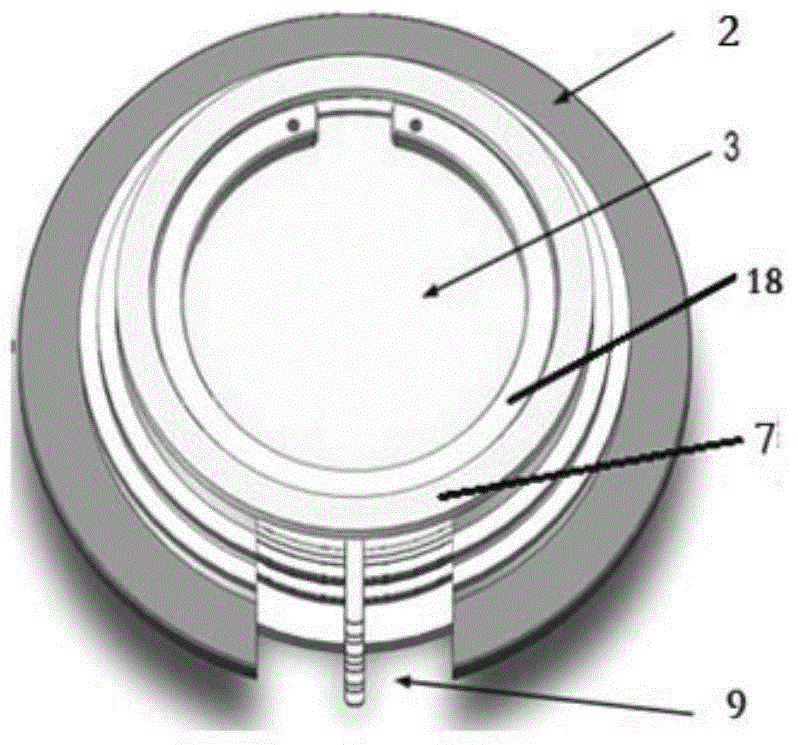

Photomultiplier of electrostatic focusing micro-channel plates

ActiveCN103915311AAchieve electrical connectionReduce transit time differenceMultiplier anode arrangementsPhotocathodePhotomultiplier

The invention discloses a photomultiplier of electrostatic focusing micro-channel plates. The photomultiplier comprises a photocathode, an electron multiplier, an anode, a focusing electrode, a power supply electrode and a supporting post for supporting the focusing electrode, the electron multiplier and the anode, the focusing electrode, the electron multiplier and the anode are arranged in a glass vacuum container, and a signal lead of the anode and the power supply electrode penetrate through the glass vacuum container to be connected with an external circuit. The photomultiplier is characterized in that the centers of the focusing electrode, the electron multiplier and the anode are coaxial, the electron multiplier comprises the two pairs of micro-channel plates arranged in parallel, and certain gaps are reserved between the micro-channel plates. Compared with the prior art, all stages of voltages of the micro-channel plates are independently adjusted, and high gains and good photoelectron spectra are achieved.

Owner:INST OF HIGH ENERGY PHYSICS CHINESE ACAD OF SCI +2

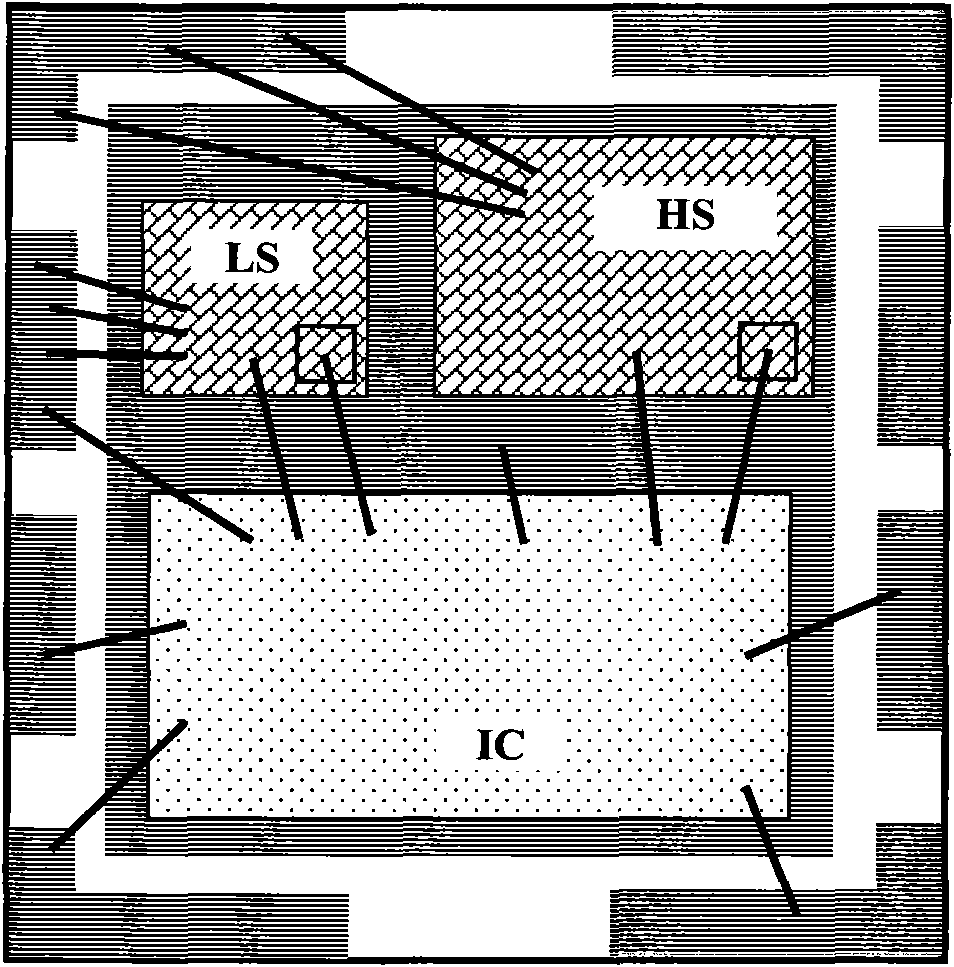

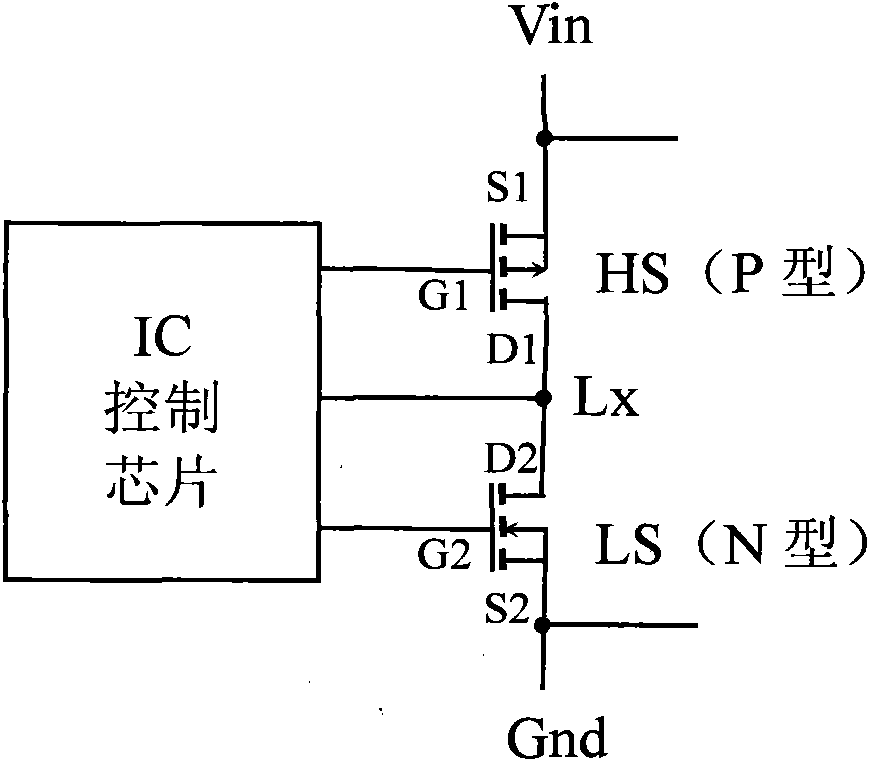

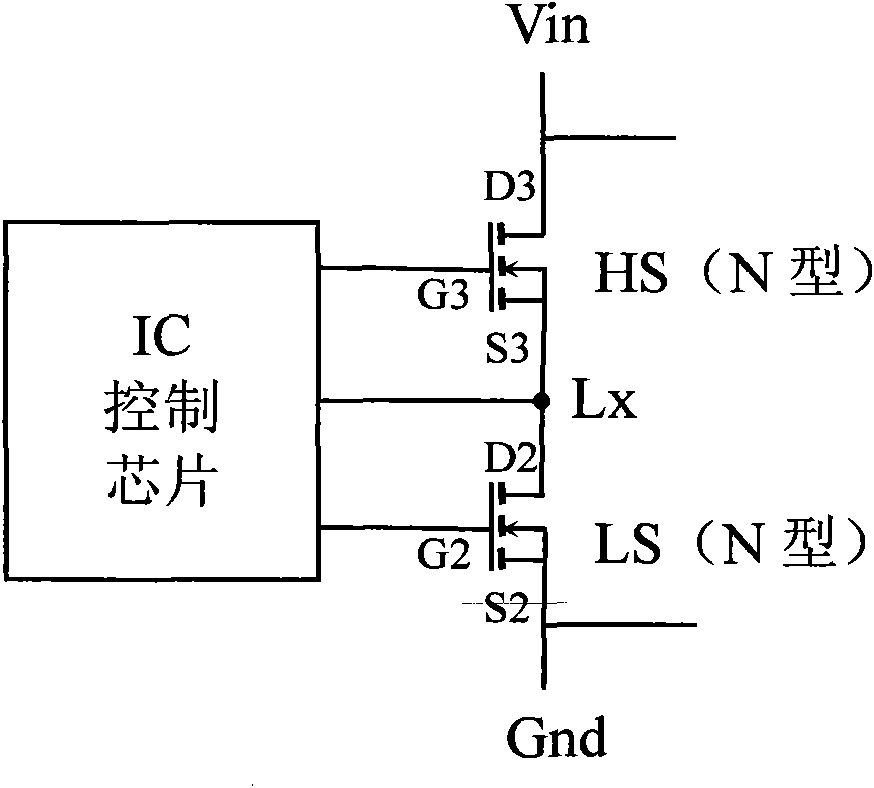

Integrally-packaged power semiconductor device

ActiveCN102760724AEffective coolingSmall sizeSemiconductor/solid-state device detailsSolid-state devicesPower semiconductor deviceMOSFET

The invention relates to an integrally-packaged power semiconductor device. A top source electrode of an inverted low-end MOSFET (Metal-Oxide-Semiconducotr Field Effect Transistor) chip is electrically connected to the top surface of a chip base; a bottom drain electrode of a high-end MOSFET chip or a top source electrode of the inverted high-end MOSFET is electrically connected with a bottom drain electrode of the low-end MOSFET chip through a first metal connecting plate; a second metal connecting plate is stacked on the high-end MOSFET chip; and the chip base is also provided with a control chip and is electrically connected with the electrodes of the high-end MOSFET chip and the low-end MOSFET chip. According to the invention, a plurality of chips are stereoscopically packaged so as to reduce the whole size of the semiconductor device; in addition, the product performance of the semiconductor device is improved by largening the size of each chip in a packaging body which has the same size as that of the chip; and because the top source electrode of the low-end MOSFET chip and the top surface of the chip base are connected, the bottom surface of the packaged and exposed chip base is connected with a ground electrode, and the shape of the exposed bottom surface is simplified, and the area of the exposed bottom surface is maximized so as to facilitate heat dissipation.

Owner:ALPHA & OMEGA SEMICON INT LP

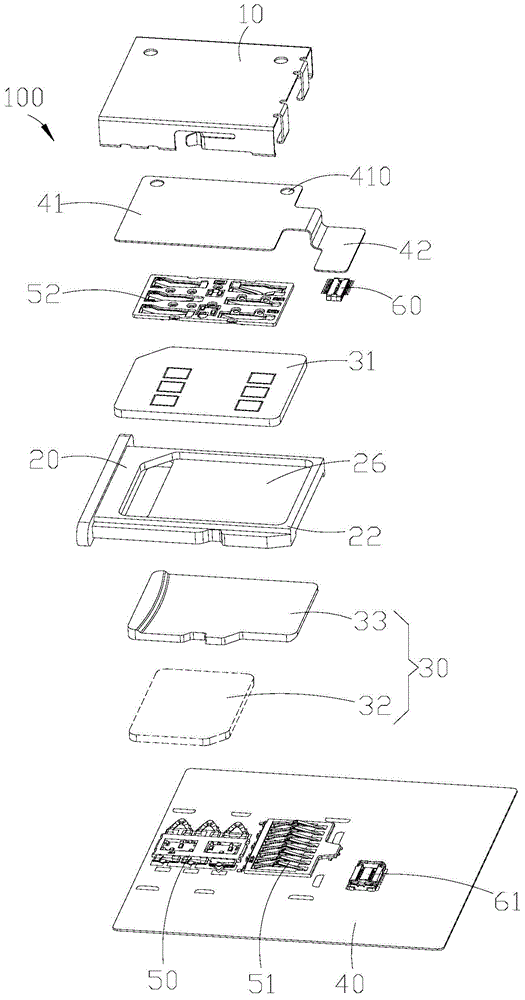

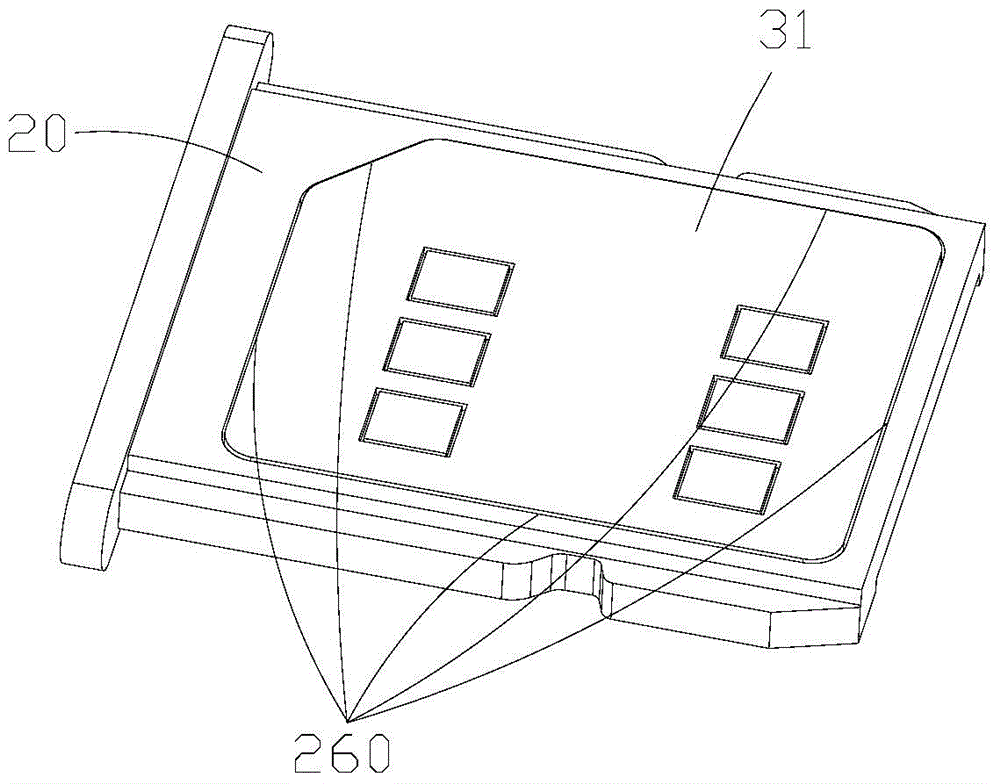

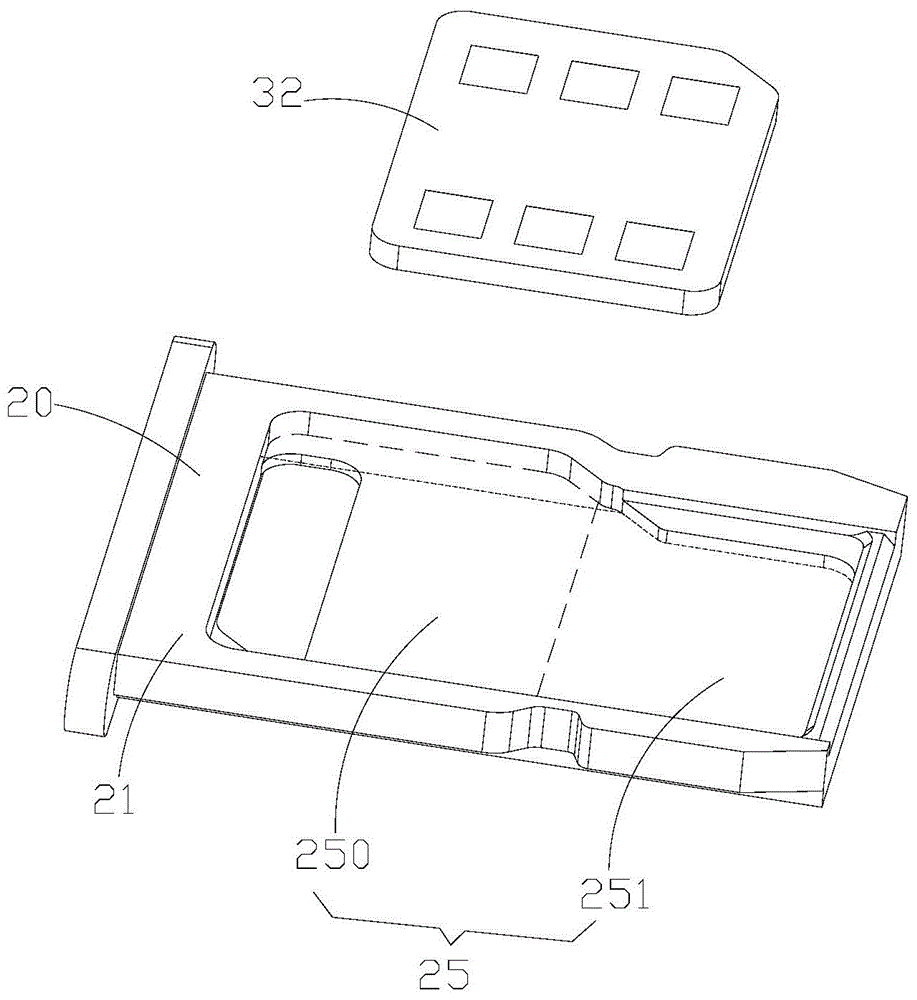

Electronic device capable of supporting multiple cards

ActiveCN104638485AEasy to replaceShorten the lengthCoupling device detailsEngineeringSubscriber identity module

The invention provides an electronic device capable of supporting multiple cards. The electronic device comprises two circuit boards, a card seat, a card cover and a card support; the card seat comprises a first SIM (subscriber identity module) card seat and a TF (Micro SD) card seat which are arranged on a first circuit board side by side, and a second SIM card seat arranged on a second circuit board; the second circuit board and the second SIM card seat on the second circuit board are integrally mounted on the inner lateral surface of the card cover; the card support is provided with a first side for supporting a first electronic card and a second side which is backed to the first side and is used for supporting a second electronic card; the first electronic card is selectively an SIM card or a TF card and is correspondingly and electrically connected with the first SIM card seat or the TF card seat; the second electronic card is electrically connected with the second SIM card seat; the second circuit board is provided with an external part extending out of the card cover; a first connector is arranged on the external part; a second connector is arranged on the first circuit board; the first connector is electrically connected with the second connector. Both front and reverse sides of one card support can be used for placing the electronic cards, and thus, design of placing various different electronic cards on double layers is implemented.

Owner:GUANGDONG OPPO MOBILE TELECOMM CORP LTD

Silicon photonic optical transceiver module

The invention discloses a silicon photonic optical transceiver module. The silicon photonic optical transceiver module comprises a circuit board and an optical component; the circuit board is arrangedin a hollow region, and the hollow region is used for accommodating the optical component; the circuit board is provided with a plurality of first bonding pads along the periphery of the hollow region; a plurality of second bonding pads are arranged at the edge of the optical component; and after the optical component and the circuit board are attached in a reverse mounting mode, the second bonding pads are attached to the corresponding first bonding pads so as to implement electrical connection. The electrical connection is established between the circuit board and the optical component by the first bonding pads and the second bonding pads, an electric signal connection path is short, a stray capacitance is small, high-frequency transmission loss is low, high-frequency characteristics are improved, and the problem of high-frequency inhibition caused by a gold-wire bonding wire currently can be effectively improved. Meanwhile, the optical component and the circuit board are attached in a reverse buckling mode, the design structure is compact, and the size of the silicon photonic optical transceiver module can be effectively reduced.

Owner:GUANGXUN SCI & TECH WUHAN

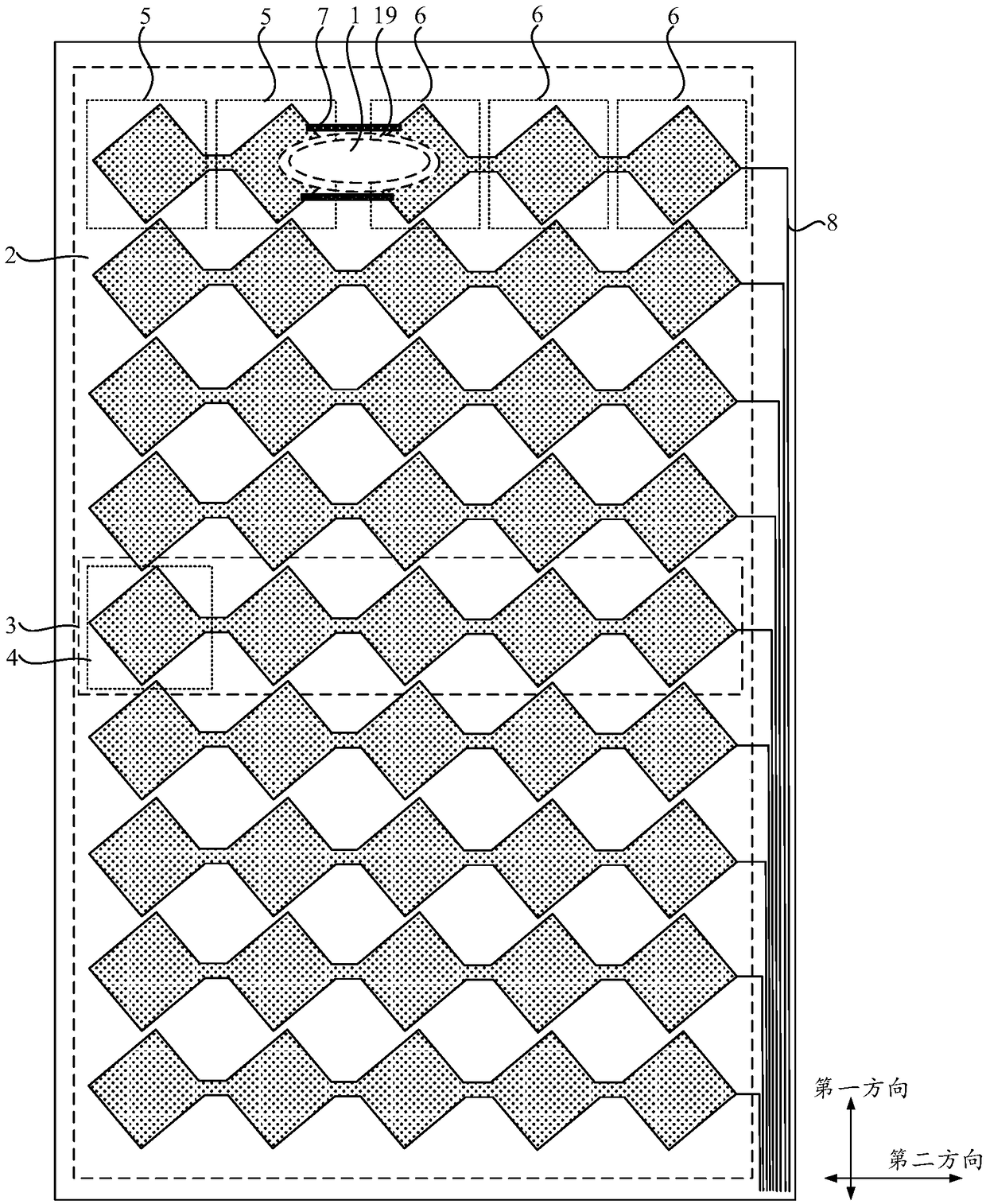

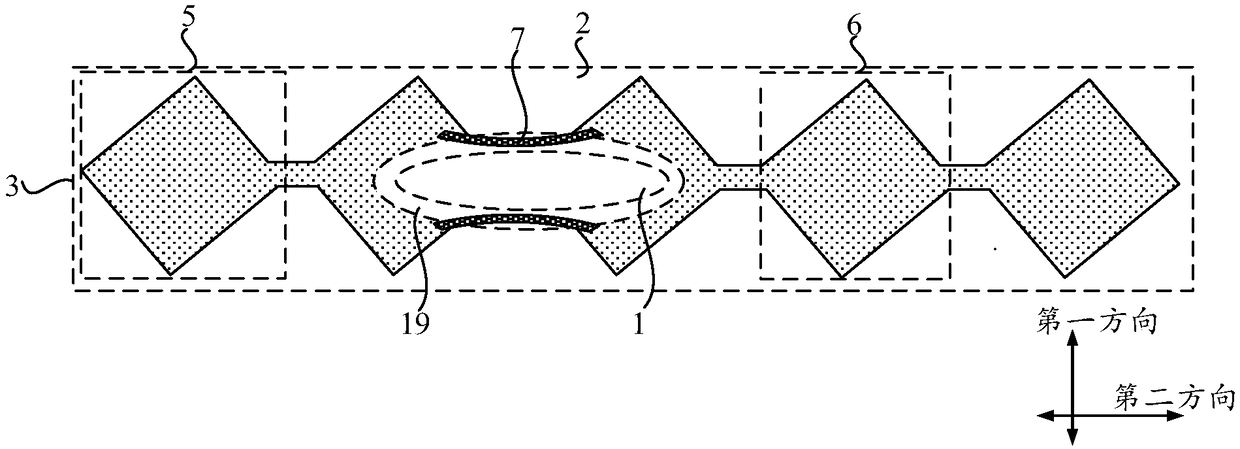

A display panel and a display device

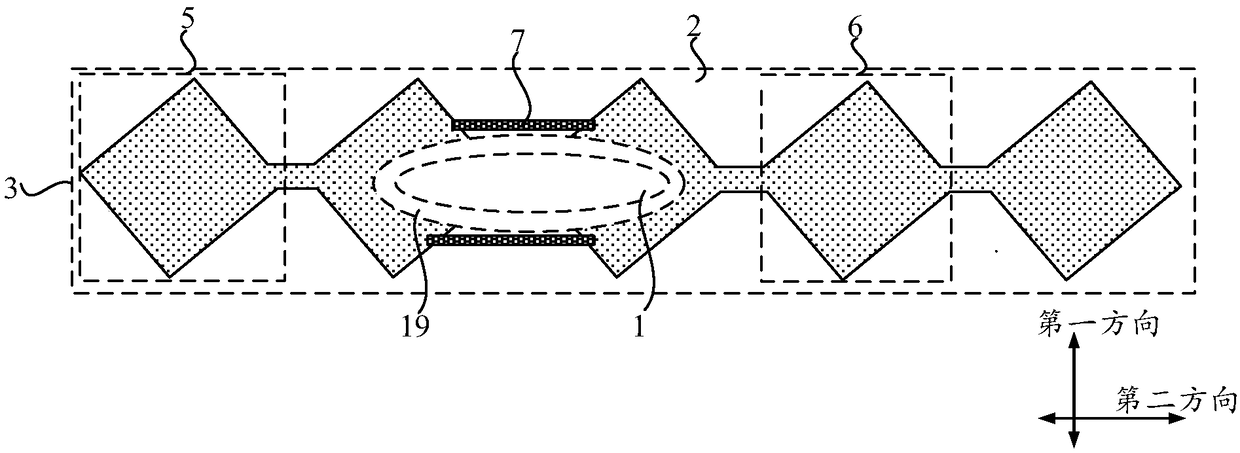

ActiveCN109388288AAchieve electrical connectionGuaranteed touch performanceInput/output processes for data processingDisplay deviceComputer science

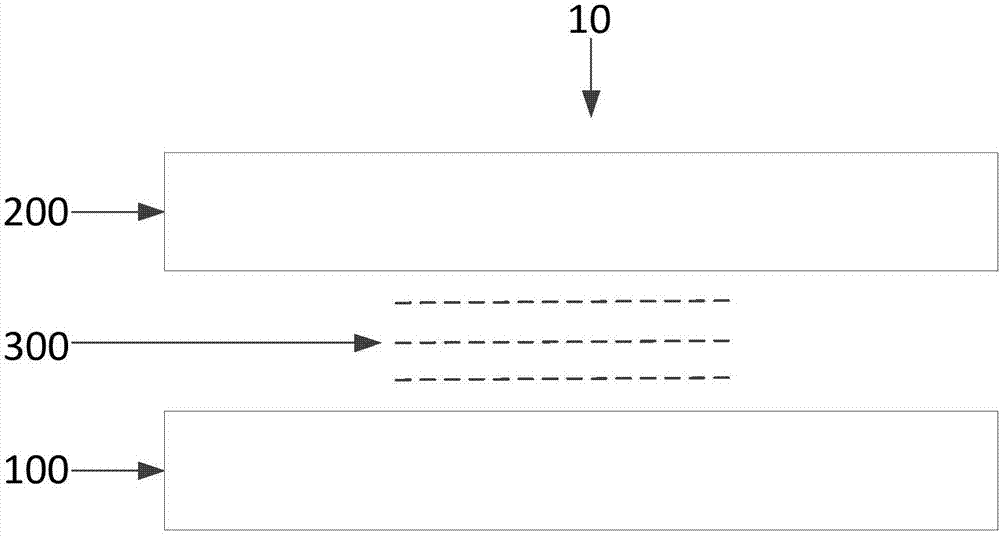

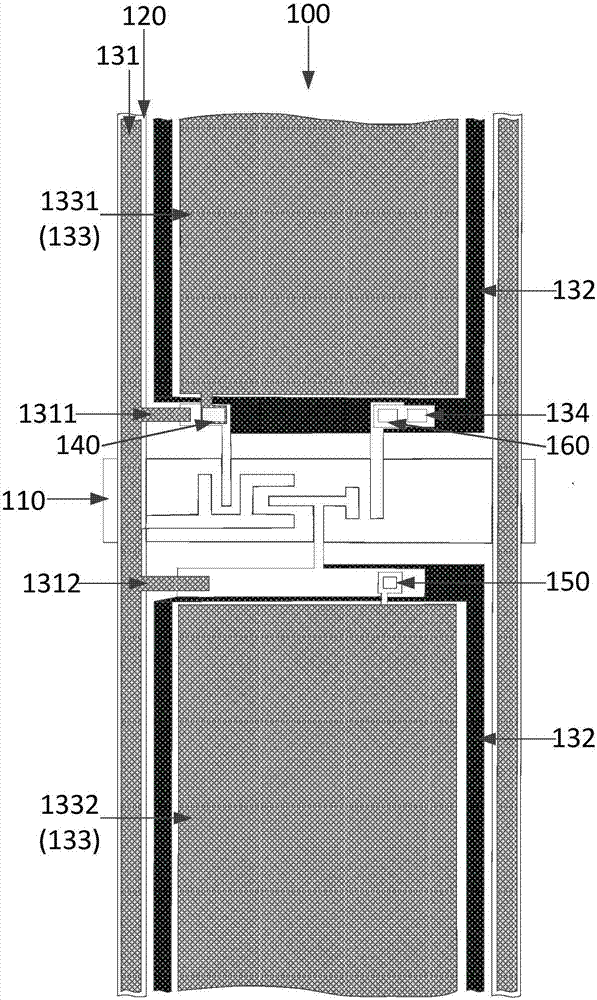

The embodiment of the invention provides a display panel and a display device, which relate to the display technical field and improve the detection precision of the touch position. The display panelcomprises a high light transmission area, a border area and a picture display area. The picture display area is provided with a touch electrode, the touch electrode comprises a touch electrode strip arranged in a first direction, and the touch electrode strip comprises a touch electrode block arranged in a second direction; for at least one touch electrode strip, the plurality of touch electrode blocks includes a plurality of first touch electrode blocks and a plurality of second touch electrode blocks, wherein the first touch electrode blocks and the second touch electrode blocks are touch electrode blocks located on both sides of a border region in a touch electrode strip, and the plurality of first touch electrode blocks are electrically connected with each other, and the plurality of second touch electrode blocks are electrically connected with each other. The display panel further includes an electrode connection structure electrically connected to the first touch electrode blockand the second touch electrode block. The display panel is used for realizing screen display.

Owner:WUHAN TIANMA MICRO ELECTRONICS CO LTD

Wireless charging device, power receiving device and wireless flat-panel charging system

InactiveCN102647015AAvoid inconvenienceEasy to useElectromagnetic wave systemElectric powerElectricityElectrical connection

Owner:SHENZHEN FEIFAN IND

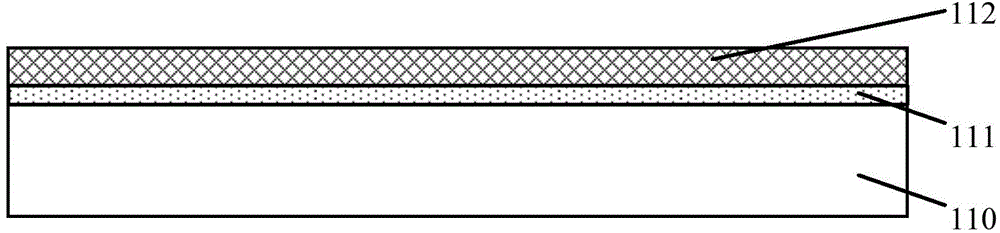

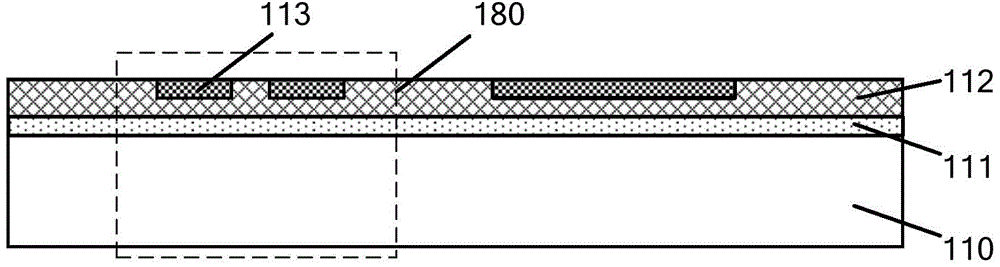

Binding method of display device and display substrate

ActiveCN109739057AThe binding process is simpleAchieve electrical connectionPrinted circuit assemblingNon-linear opticsEngineeringElectrical connection

The invention discloses a binding method of a display device and a display substrate, and belongs to the field of display technology. The display device includes a display substrate, a binding structure and a circuit board, wherein the binding structure is arranged on the display substrate, is made of a conductive tape, and has a certain stickiness; and the binding structure can be directly bondedto the first conductive structure of the circuit board. The electrical connection between the binding structure and the first conductive structure can be realized without using ACF to bond the binding structure to the first conductive structure; the process of binding the display substrate is effectively simplified; and the cost is lowered.

Owner:BOE TECH GRP CO LTD

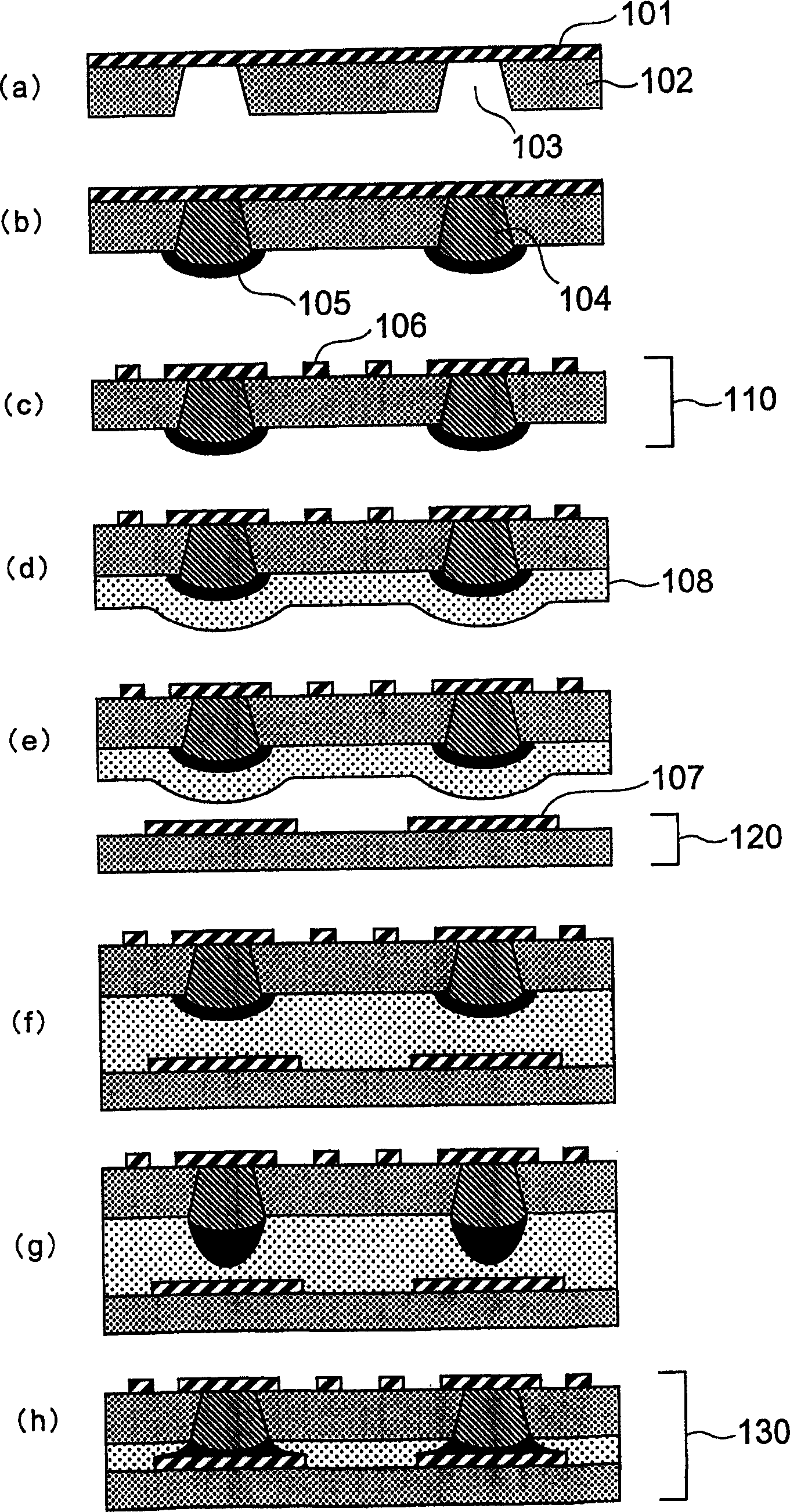

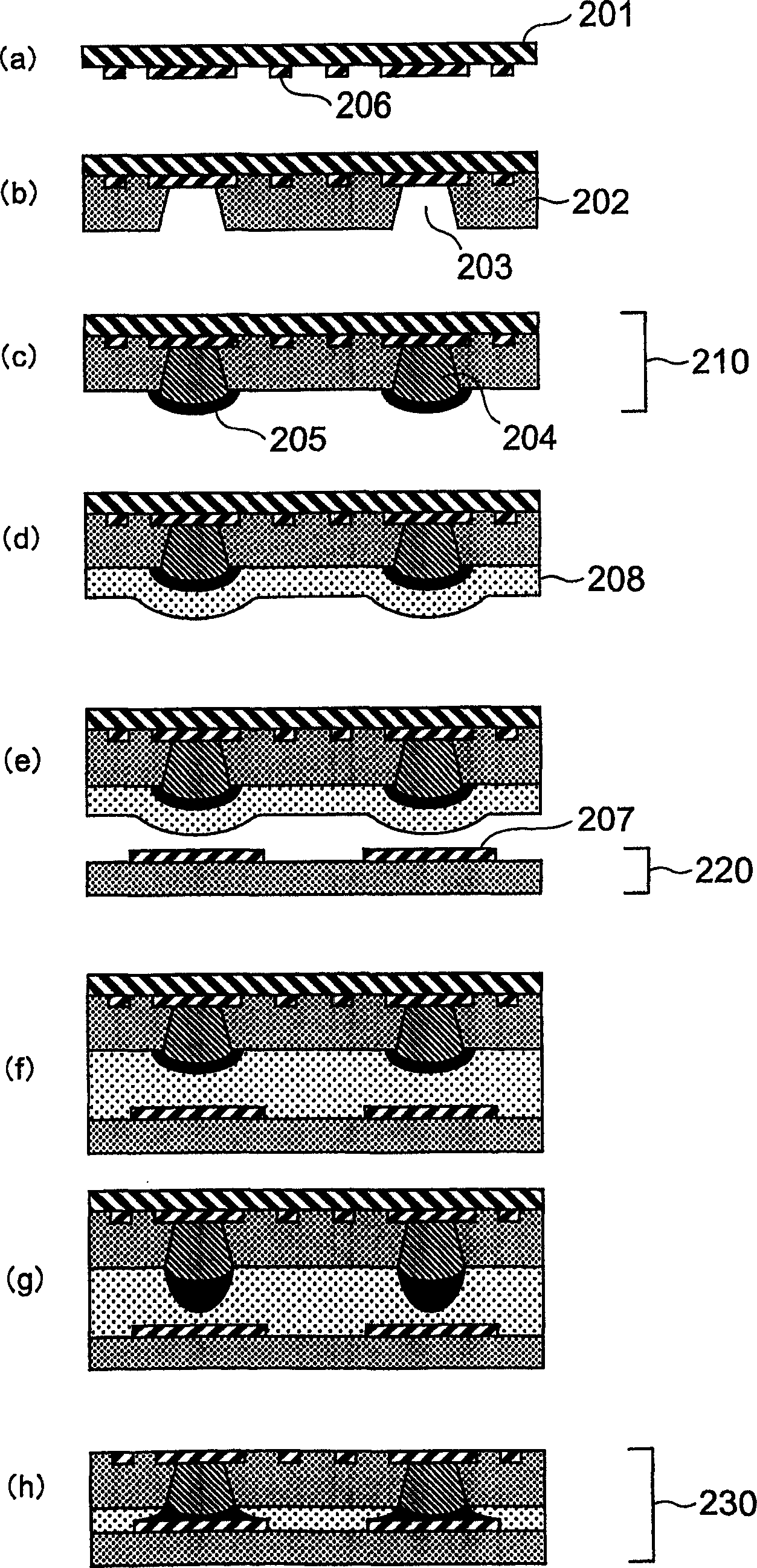

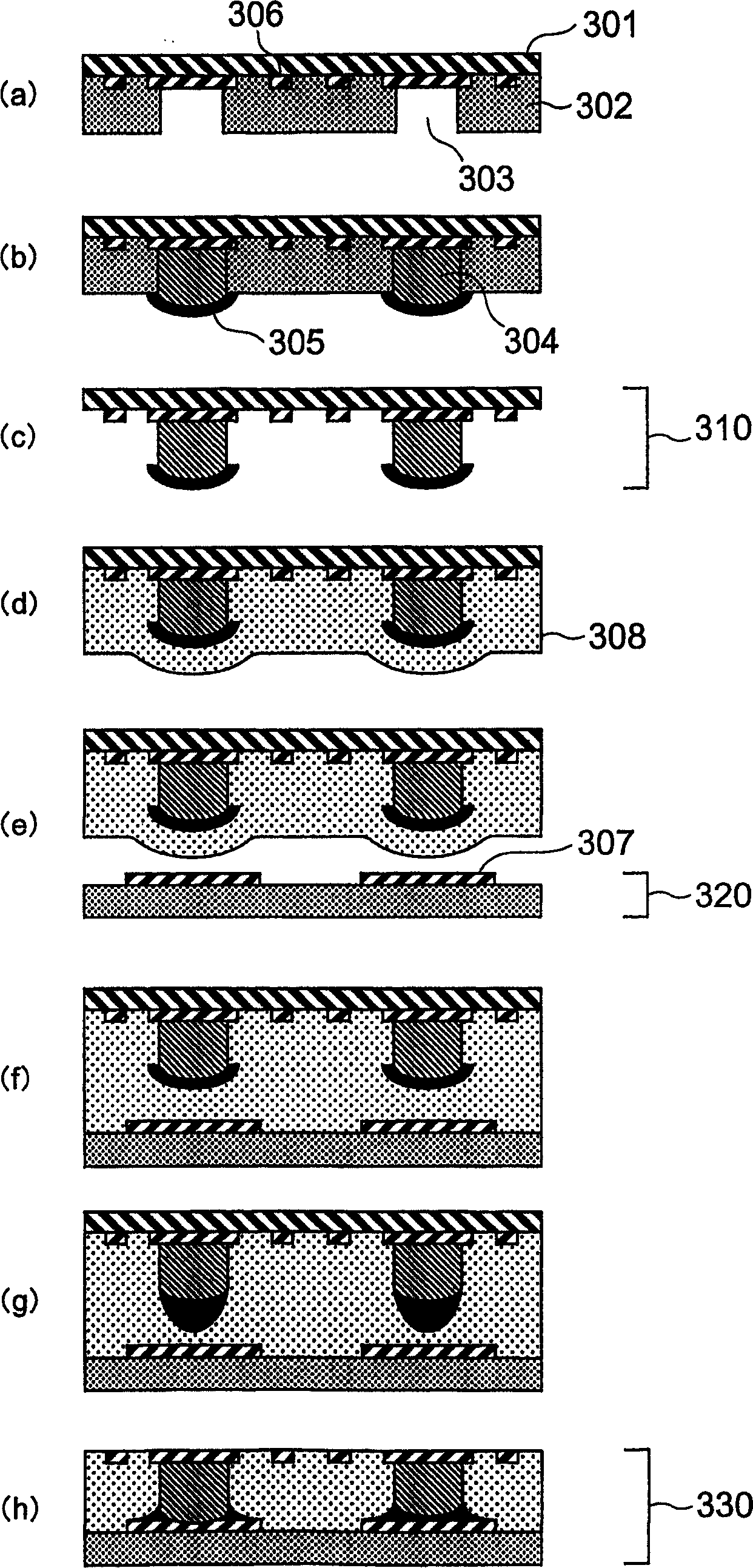

Method of manufacturing electronic part and electronic part obtained by the method

InactiveCN1498520AImprove reliabilityAchieve electrical connectionPrinted circuit assemblingInsulating substrate metal adhesion improvementElectrical conductorEngineering

In a process for producing an electronic part which comprises soldering (A) an electronic member having conductor portions I for electric connection having a solder layer or a solder bump (a solder portion) on a surface of a tip and (B) an electronic member to be connected having conductor portions II for electric connection arranged at positions corresponding to positions of conductor portions I by pressing (A) to (B) under heating via an adhesive layer, the solder portion is brought into contact with the adhesive layer, the solder portion is melted by heating at a temperature of or higher than a melting point of the solder, the soldering is conducted by pressing the melted solder portion, and the adhesive layer is cured. An electronic part is obtained in accordance with the process. Electric connection is surely achieved and a highly reliable electronic part can be obtained with excellent productivity.

Owner:SUMITOMO BAKELITE CO LTD

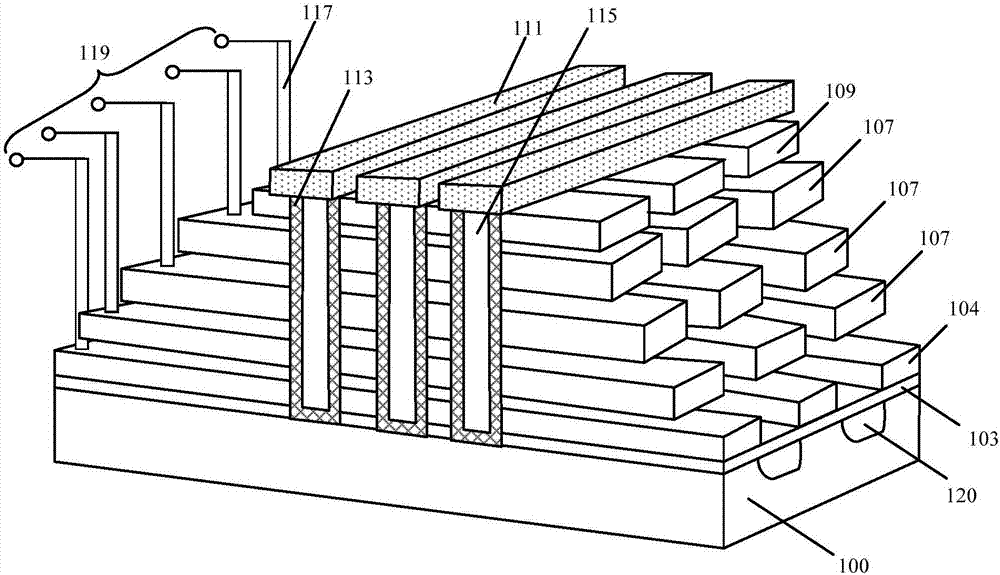

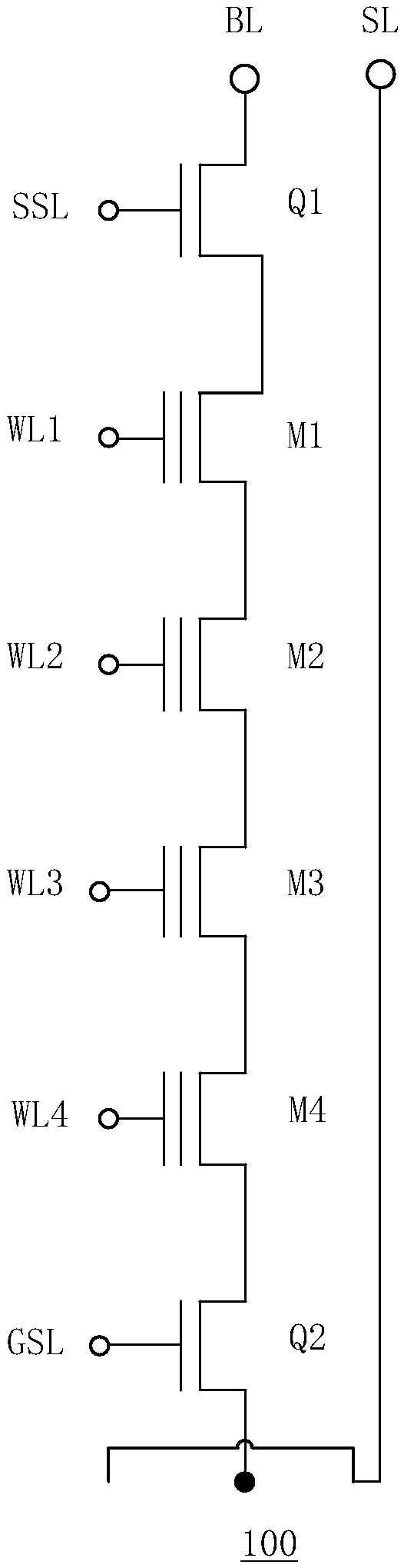

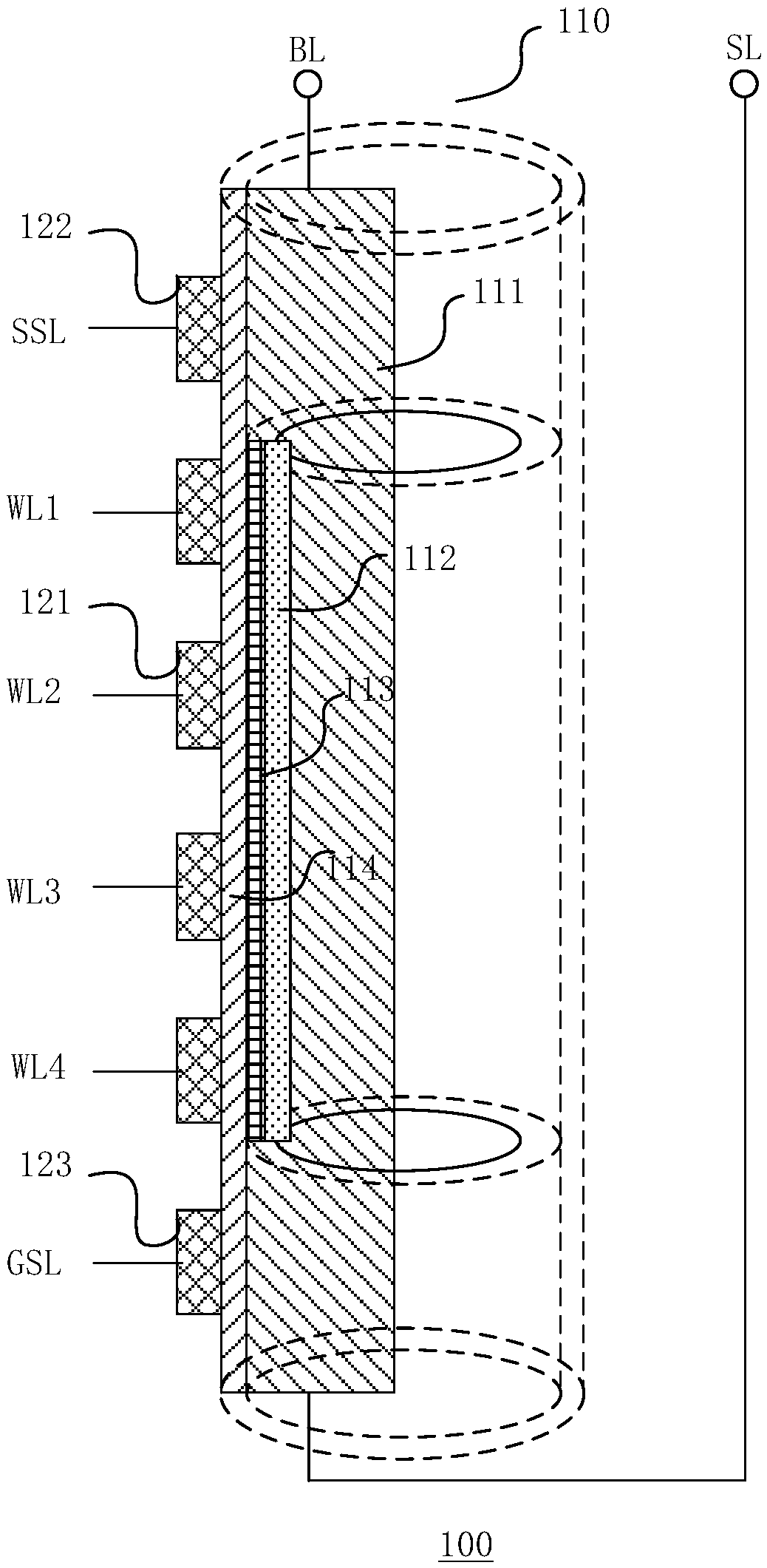

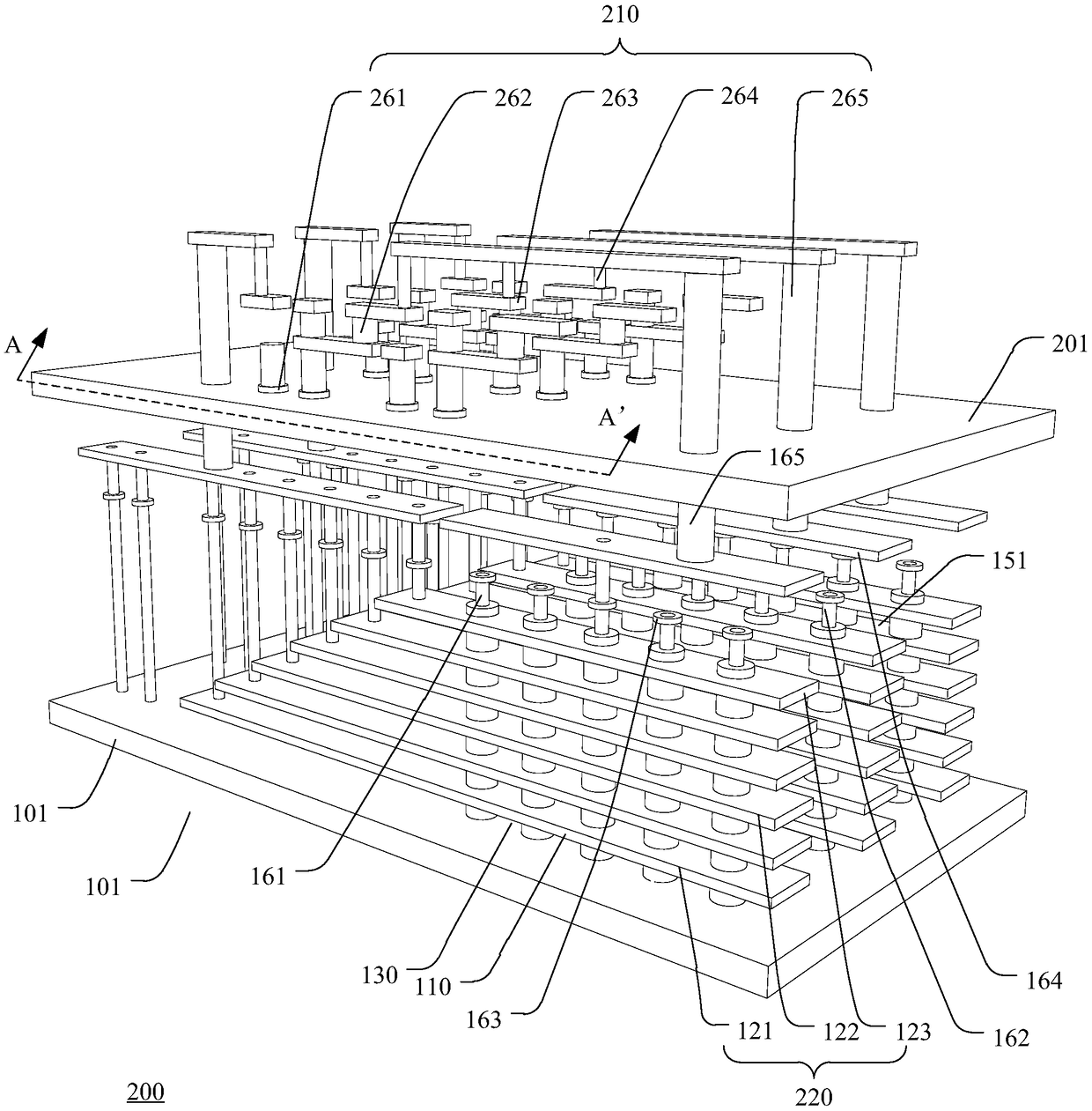

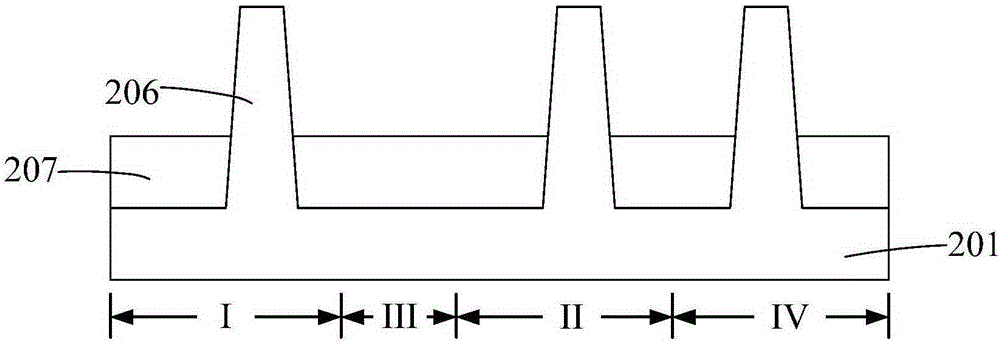

Three-dimensional storage and formation method therefor

ActiveCN106876397AReduce in quantitySimple processSemiconductor/solid-state device detailsSolid-state devicesElectricityMultiple layer

The invention discloses a three-dimensional storage and a formation method therefor. The three-dimensional storage comprises a substrate, a plurality of separated stacking layer structures, an isolation layer, a connecting structure and a plurality of inserting plugs, wherein the substrate comprises a device region and a connecting region which are arranged adjacently; the multiple separated stacking layer structures are positioned on the device region and the connecting region of the substrate; the stacking layer structures comprise multiple layers of stacked grids; the isolation layer is positioned on the device region, between adjacent stacking structures, of the substrate; the connecting structure is positioned on the connecting region of the substrate; the connecting structure is connected with the adjacent stacking structures; the connecting structure comprises multiple layers of stacked electric connecting layers; the two ends of each electric connecting layer are connected with the grids on the same layer in the adjacent stacking structures; the multiple inserting plugs are positioned on the surfaces of the grids in each layer; and each inserting plug is electrically connected with the grids in contact, the grids on the same layer with the grids in contact, and the electric connecting layers on the same layer with the grids in contact. By virtue of the formation method, the number of the inserting plugs can be reduced, the process can be simplified, the size of the storage can be reduced, and the space utilization rate of the chip can be improved.

Owner:YANGTZE MEMORY TECH CO LTD

MEMS (Micro Electro Mechanical Systems) pressure sensor and formation method thereof

ActiveCN104634487AAchieve electrical connectionAffect the manufacturing processDecorative surface effectsFluid pressure measurement by electric/magnetic elementsElectrical resistance and conductanceMems pressure sensor

The invention relates to an MEMS (Micro Electro Mechanical Systems) pressure sensor and a formation method thereof. The formation method comprises the following steps of providing a first substrate comprising a first surface and a second surface which are opposite, wherein the first substrate comprises at least one conducting layer, and the conducting layer is located on one side of the first surface of the first substrate; providing a second substrate comprising a third surface and a fourth surface which are opposite, wherein the second substrate comprises a second base, a piezoresistive element and a pressure sensing area, and the piezoresistive element is located in the pressure sensing area and on one side of the third surface of the second substrate; mutually fixing the first surface of the first substrate and the third surface of the second substrate; forming a cavity between the first substrate and the pressure sensing area of the second substrate; removing the second base, and forming a fifth surface opposite to the third surface of the second substrate; forming a first conductive plug penetrating to the surface of the at least one conducting layer from one side of the fifth surface of the second substrate. The performance and the reliability of the MEMS pressure sensor are improved, and the size is reduced, and the processing cost is reduced.

Owner:MEMSEN ELECTRONICS

Through silicon via stack-based three-stack memory structure and manufacturing method thereof

PendingCN109300903AReduce areaAchieve electrical connectionSolid-state devicesSemiconductor devicesCMOSStorage cell

The invention relates to a through silicon via stack-based three-stack memory structure. According to the through silicon via stack-based three-stack memory structure, a CMOS circuit comprises a firstsilicon substrate and a first insulating layer on the first silicon substrate, a plurality of first external pads being arranged in the first insulating layer; a memory cell array includes a second silicon substrate and a second insulating layer on the second silicon substrate, a plurality of second external pads being arranged in the second insulating layer; the CMOS circuit further comprises through silicon vias which pass through the first insulating layer and the first silicon substrate and are electrically connected with the first external pads; and the first silicon substrate and the second insulating layer contact with each other, the through silicon vias are bonded to the second external pads, and therefore, electrical connection between the CMOS circuit and the memory cell arraycan be realized. According to the through silicon via stack-based three-stack memory structure provided by the embodiments of the invention, the through silicon vias are formed on the CMOS circuit; the first ends of the through silicon vias are connected with the first external pads on the CMOS circuit, and the second ends of the through silicon vias are bonded to the second external pads of the memory cell array, so that the electrical connection between the CMOS circuit and the memory cell array is realized, and therefore, storage density can be improved, and wiring density can be decreased.

Owner:YANGTZE MEMORY TECH CO LTD

Ultrasound probe

ActiveCN104337547AAchieve electrical connectionUltrasonic/sonic/infrasonic diagnosticsMechanical vibrations separationUltrasound probePhysics

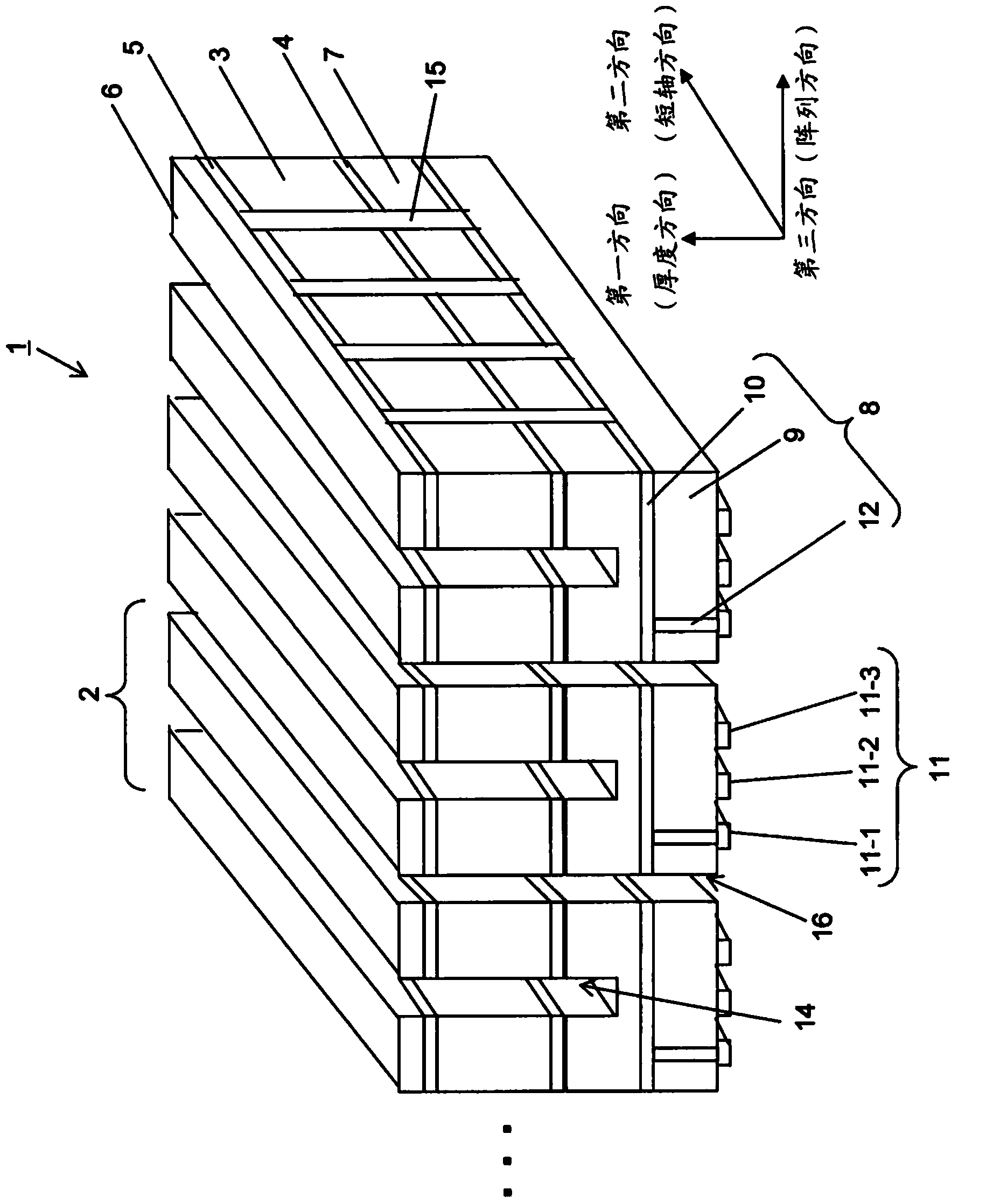

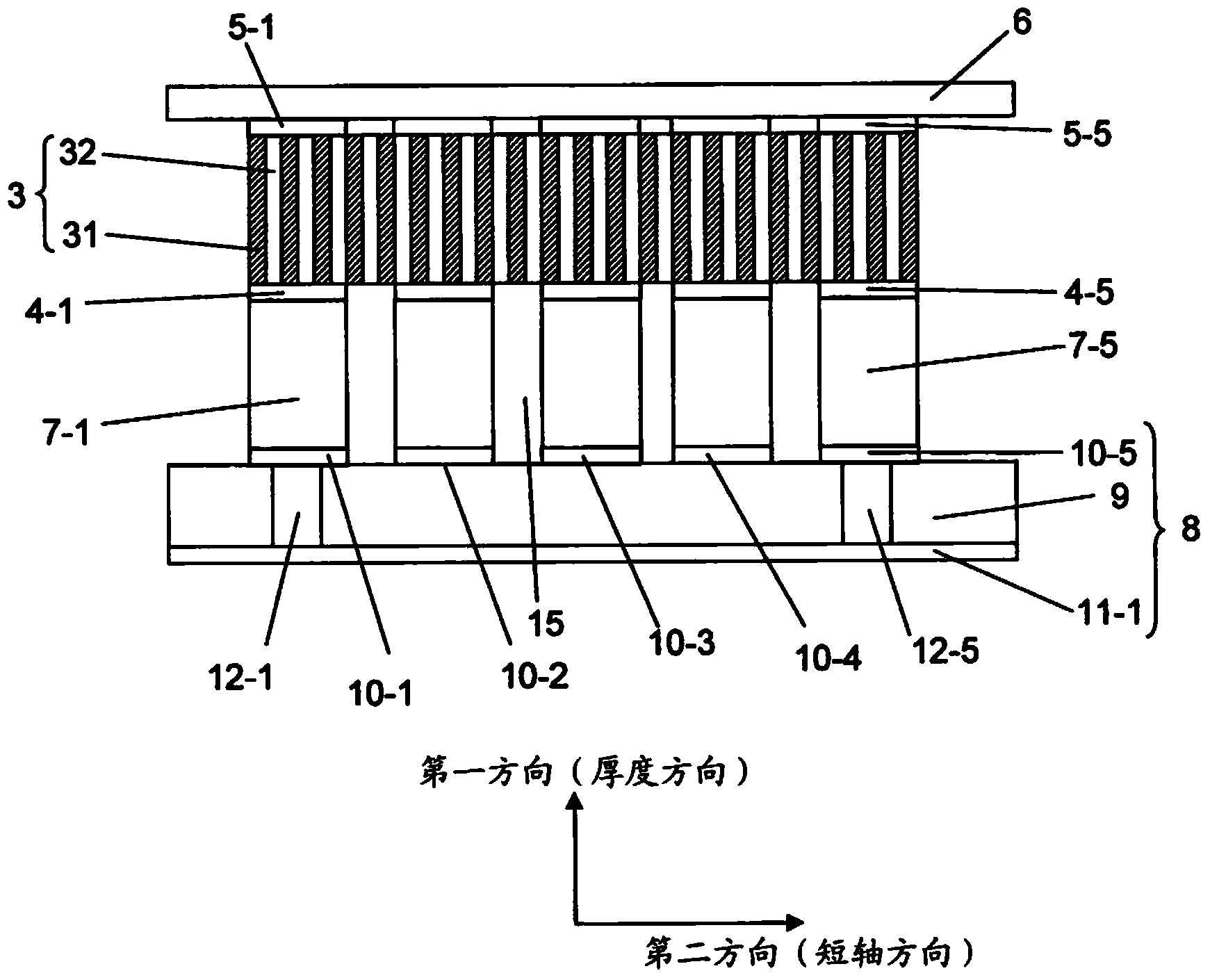

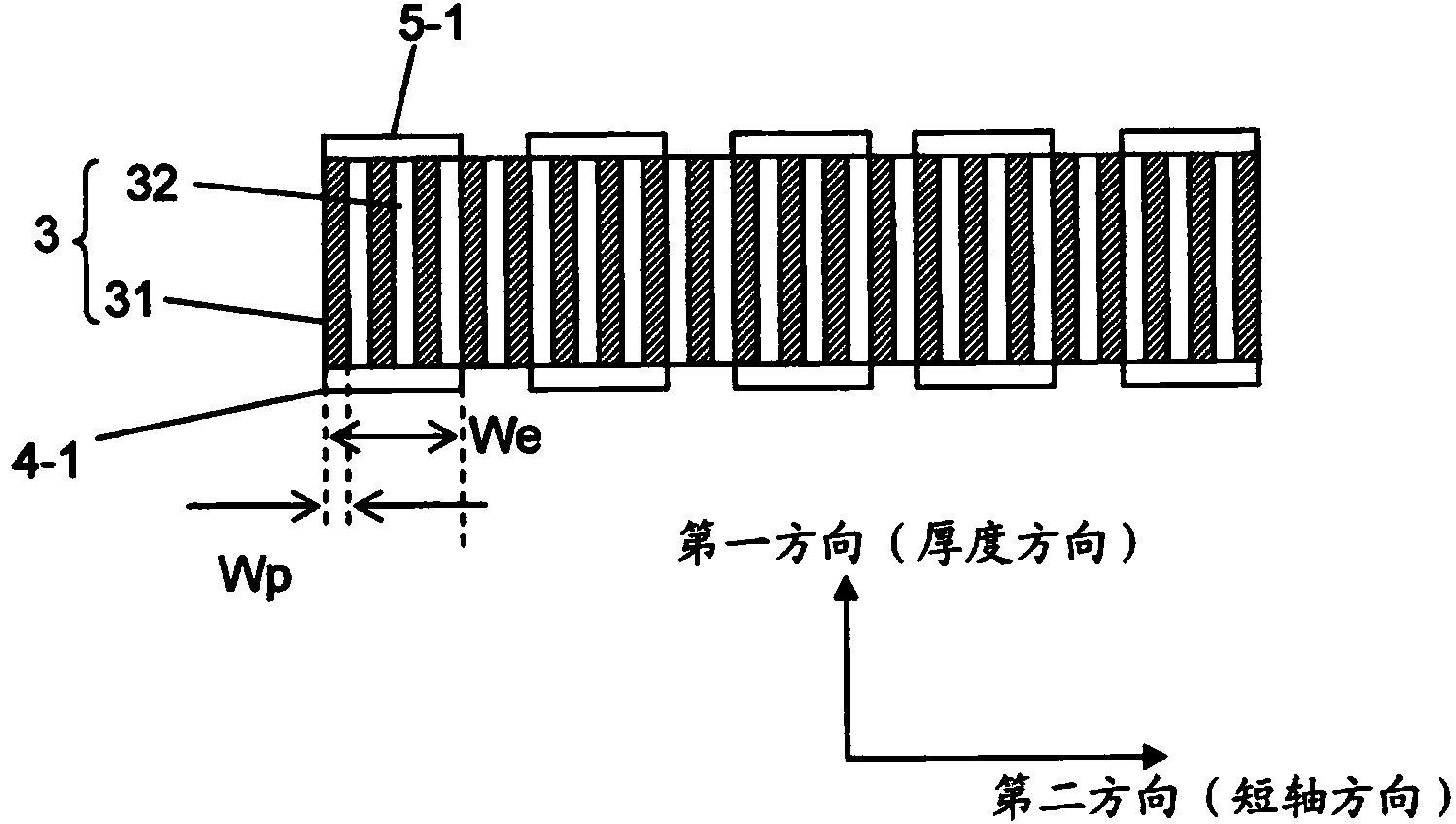

An ultrasound probe includes a laminated body having: a piezoelectric body having a thickness in a first direction; a first electrode and a second electrode that face each other so as to sandwich the piezoelectric body in the first direction; an intermediate layer that is electrically connected with the second electrode and that is provided on an opposite side to the piezoelectric body with respect to the second electrode; and a third electrode that extends in a second direction that is orthogonal to the first direction. A plurality of the first electrodes and second electrodes are arranged at predetermined intervals in the second direction. A plurality of the laminated bodies are arranged in a third direction. A first groove that penetrates through the first electrode, the piezoelectric body, and the second electrode and a part of the intermediate layer is formed in the laminated body.

Owner:KONICA MINOLTA INC

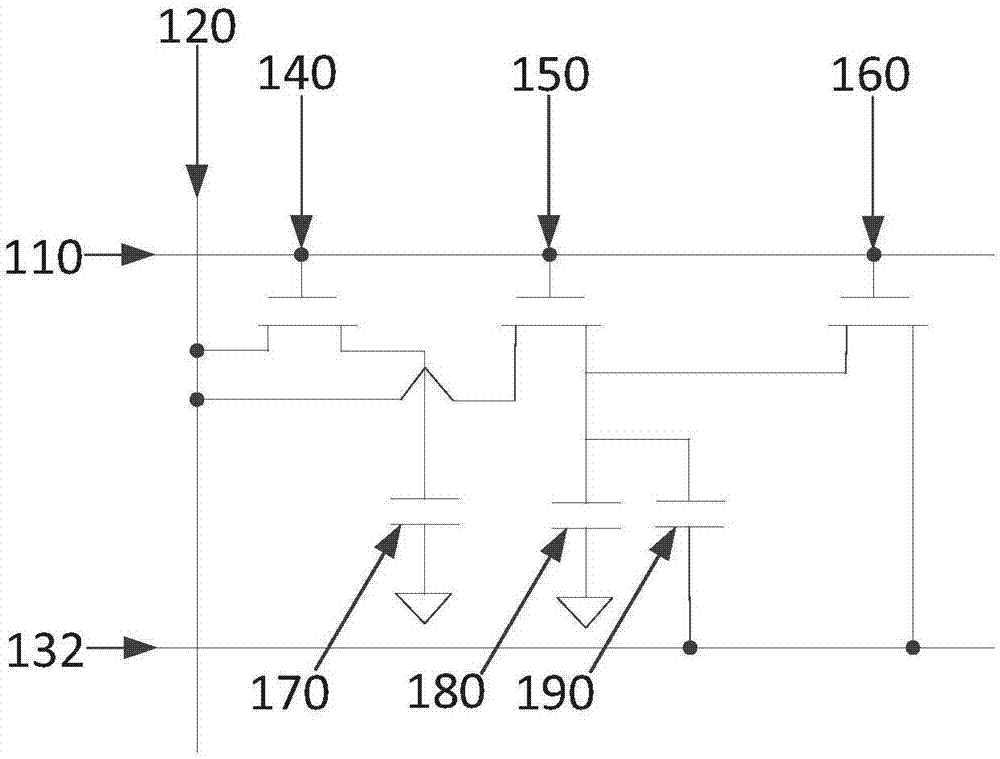

Display panel, array substrate and dark attunement method thereof

ActiveCN107479271AAchieve electrical connectionRealization of dimmingNon-linear opticsOptoelectronicsTransistor

The invention provides a display panel, an array substrate and a dark attunement method thereof. The dark attunement method comprises the steps that when a pixel electrode anomaly exists, a pixel electrode and a data line are disconnected; a drain electrode of a thin film transistor and an overlap area of a shading electrode are fused; the shading electrode is directly loaded to the pixel electrode. Accordingly, dark attunement is achieved conveniently.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

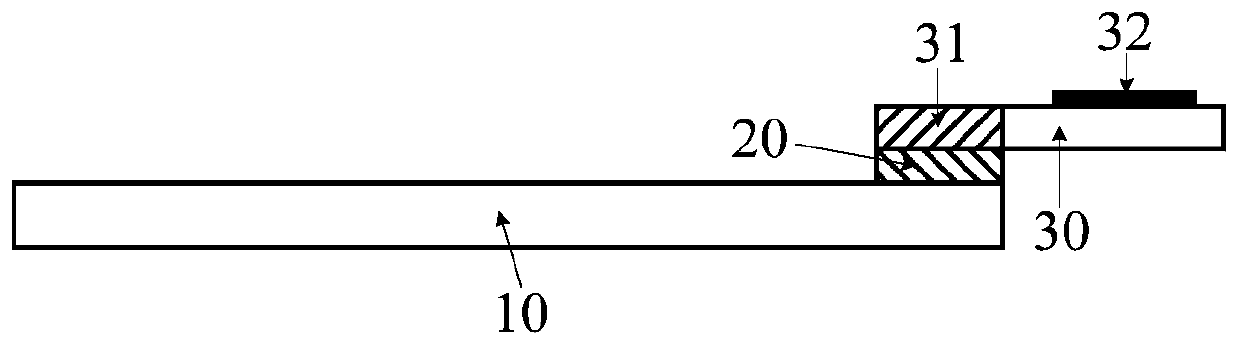

Sensing chip, fingerprint recognition module, manufacturing method of fingerprint recognition module and mobile terminal

PendingCN105868736AImprove aestheticsSo as not to damagePrint image acquisitionFlexible circuitsEngineering

The invention discloses a sensing chip, a fingerprint recognition module, a manufacturing method of the fingerprint recognition module and a mobile terminal. The sensing chip is suitable for being attached to a flexible printed circuit board and comprises an attaching part and a spraying part, wherein the lower surface of the attaching part is suitable for being attached to the flexible printed circuit board, the spraying part is connected with the attaching part and located on the attaching part, and the periphery of the spraying part exceeds the periphery of the attaching part. According to the sensing chip of the fingerprint recognition module, the sensing chip is set to comprise the attaching part and the spraying part, the attaching part is attached to the flexible printed circuit board so that the sensing chip can be electrically connected with the flexible printed circuit board, the spraying part is sprayed so that the attractiveness of the appearance of the fingerprint recognition module can be improved. Meanwhile, the periphery of the spraying part exceeds the periphery of the attaching part so that the sensing chip can be protected against damage in the machining process of the sensing chip, and the working reliability of the sensing chip is improved.

Owner:GUANGDONG OPPO MOBILE TELECOMM CORP LTD

MEMS (micro-electro mechanical system) pressure sensor and forming method thereof

ActiveCN104655334AAchieve electrical connectionAffect the manufacturing processDecorative surface effectsForce measurementElectricityMems pressure sensor

The invention discloses an MEMS (micro-electro mechanical system) pressure sensor and a forming method thereof. The forming method comprises steps as follows: a first substrate comprising a first surface and a second surface is provided and comprises at least one conductive layer which is located on one side of the first surface of the first substrate; a second substrate comprising a third surface and a fourth surface is provided and comprises a second base, a pressure-sensitive electrode and a pressure sensing area, and the pressure-sensitive electrode is located in the pressure sensing area and is located on one side of the third surface of the second substrate; the first surface of the first substrate is fixed with the third surface of the second substrate, and a hollow cavity is formed between the first substrate and the pressure sensing area of the second substrate; the second base is removed, and a fifth surface opposite to the third surface of the second substrate is formed; a first conductive plug penetrating to the at least one conductive layer is formed on one side of the fifth surface of the second substrate, so that the at least one conductive layer and the pressure-sensitive electrode are electrically connected. According to the MEMS pressure sensor and the forming method thereof, the performance and the reliability of the MEMS pressure sensor are improved, the size is reduced, and the processing cost is reduced.

Owner:MEMSEN ELECTRONICS

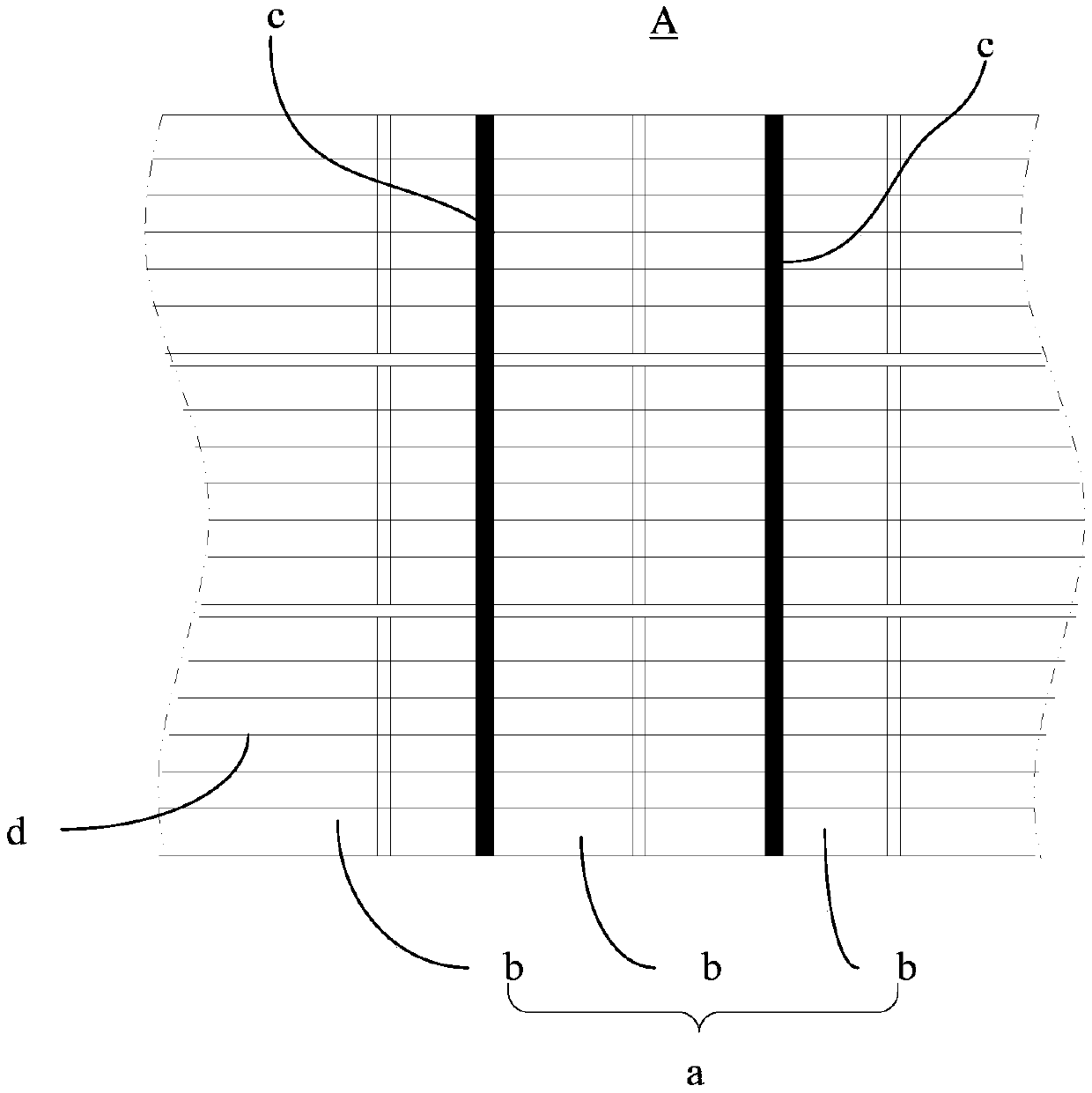

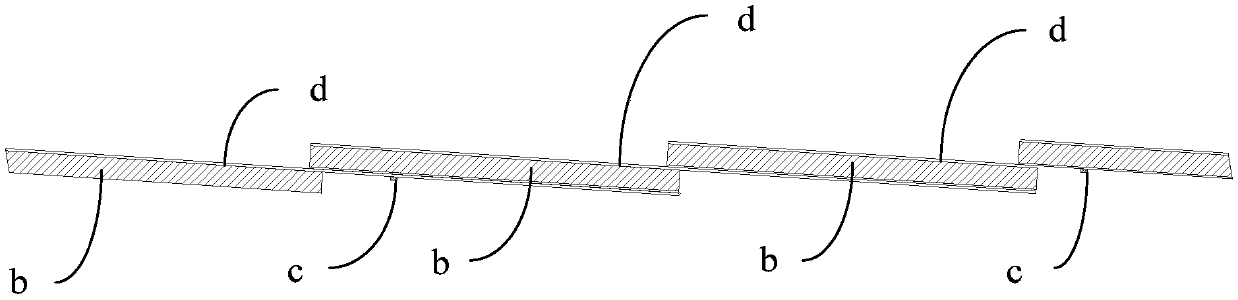

Alternating current LED neon lamp belt based on FPCs

InactiveCN106122823ADoes not affect normal workHigh practical valueElectric circuit arrangementsProtective devices for lightingEngineeringAlternating current

The invention discloses an alternating current LED neon lamp belt based on FPCs. The alternating current LED neon lamp belt comprises a power source, a neon lamp belt main body, installation grooves and a tail end assembly, wherein the power source is internally provided with a control circuit, the neon lamp belt main body is connected with the power source through an input end connecting assembly, the installation grooves are used for installing the neon lamp belt main body, and the tail end assembly is located at the tail end of the neon lamp belt main body and used for blocking the neon lamp belt main body. The neon lamp belt main body comprises at least two neon lamp belt bodies which are subjected to extrusion molding through the FPCs, and the adjacent lamp belt bodies are movably connected through a middle end connecting assembly. According to the alternating current LED neon lamp belt based on the FPCs, the input end connecting assembly is arranged between the power source and the neon lamp belt bodies, and the middle end connecting assemblies are arranged between the neon lamp belt bodies, so that plug-pull movable connection between the power source and the neon lamp belt bodies as well as between the neon lamp belt bodies is achieved; and thus, the problem that the size dimension of a traditional neon lamp belt cannot be changed is completely solved, the environment adaptive capacity of the LED neon lamp belt is greatly improved, and the practical value of the LED neon lamp belt is improved.

Owner:BLUEVIEW ELEC OPTIC TECH CO LTD

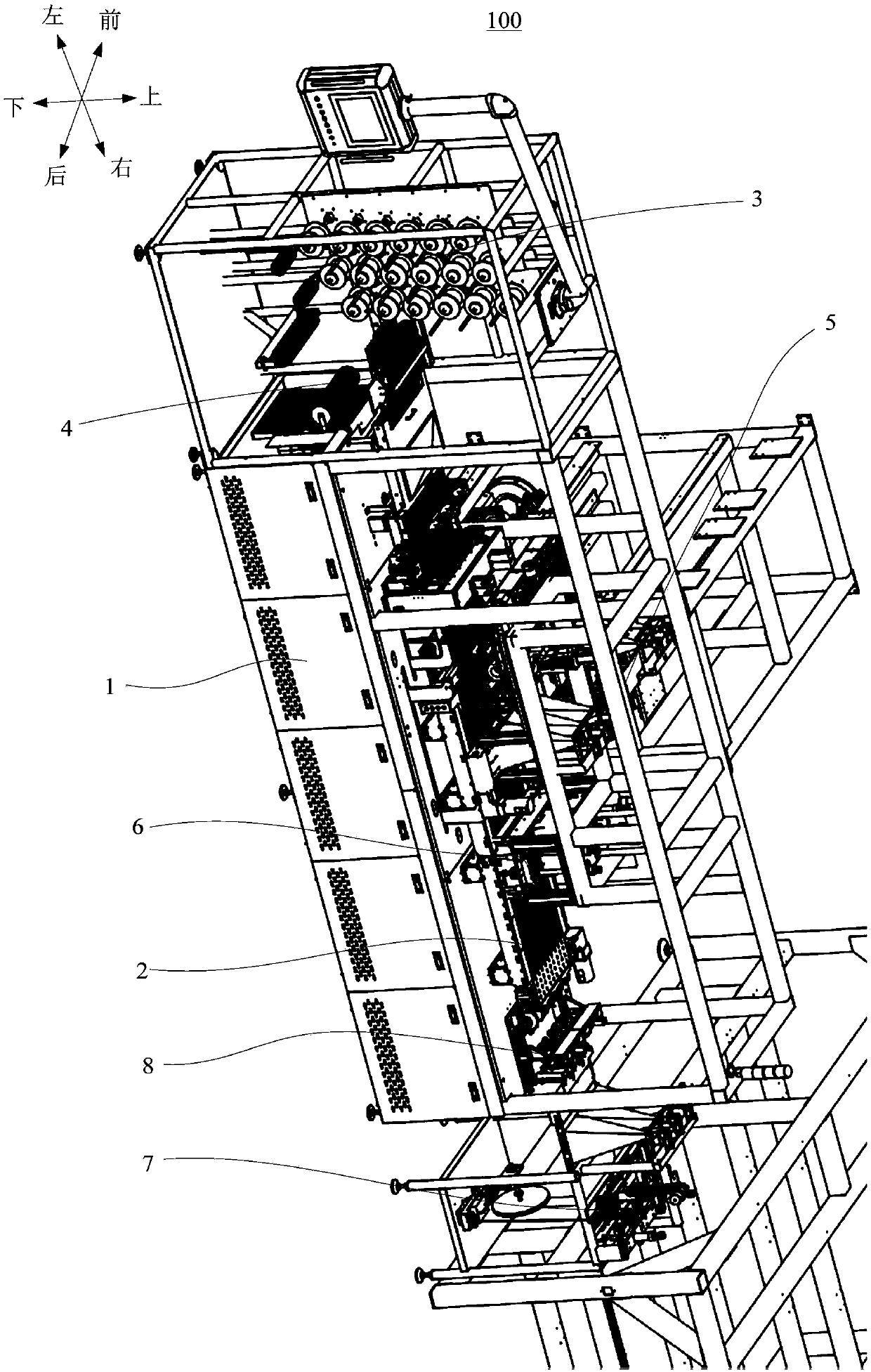

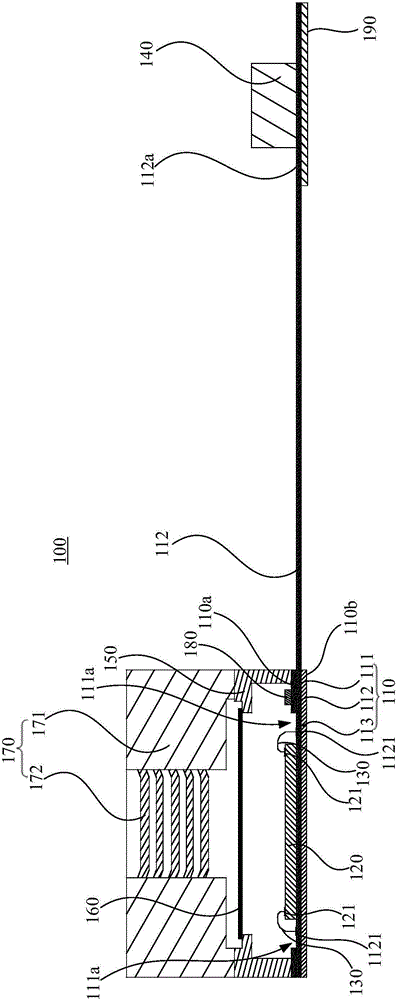

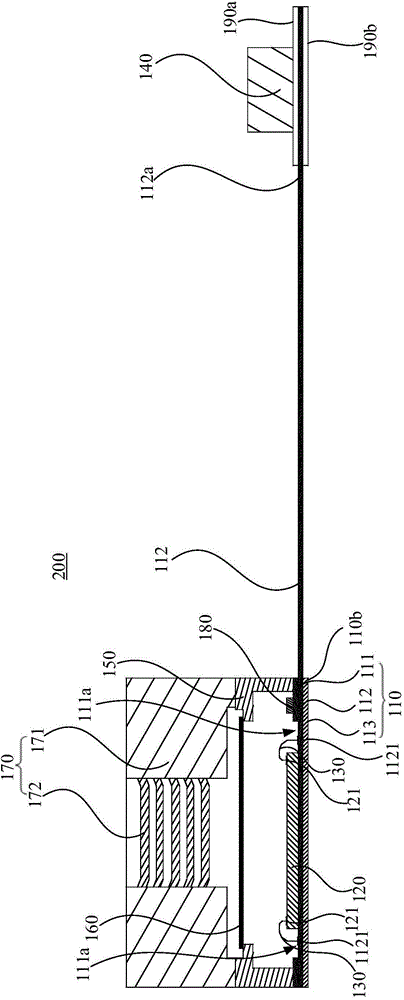

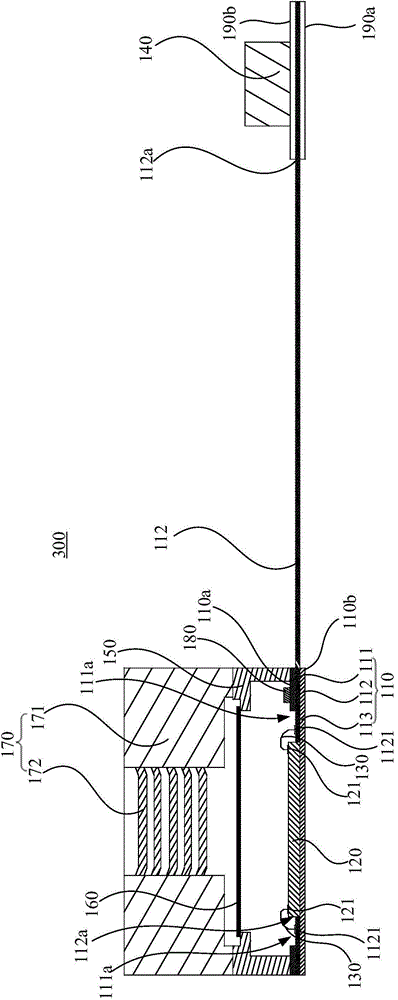

Solar cell welding machine

PendingCN109623218ARealize automatic weldingClosely arrangedFinal product manufactureWelding/cutting auxillary devicesCell interconnectionWelding

The invention discloses a solar cell welding machine. The solar cell welding machine comprises a machine base, a conveying assembly, a first welding strip feeding device, a second welding strip feeding device, a cell feeding and discharging device, an interconnection welding device and a confluence welding device; the machine base is provided with a cell paving station, a waiting station, an interconnection welding station and a confluence welding station; the conveying assembly conveys a plurality of solar cells to the interconnection welding station via the cell paving station successively;the first welding strip feeding device conveys a first welding strip to the cell paving station; the second welding strip feeding device conveys a plurality of second welding strips to the waiting station and the cell paving station; the cell feeding and discharging device conveys solar cells to the cell paving station; the interconnection welding device welds and forms a plurality of interconnected solar cell strings; and the confluence welding device welds and forms a cell interconnection plate. Simultaneous welding of the multiple solar cell strings and automatic welding of the solar cell interconnection plate are achieved, the production efficiency is improved, and the conversion efficiency of a photovoltaic module is improved.

Owner:WUHAN SUNIC INTELLIGENT EQUIP MFG CO LTD

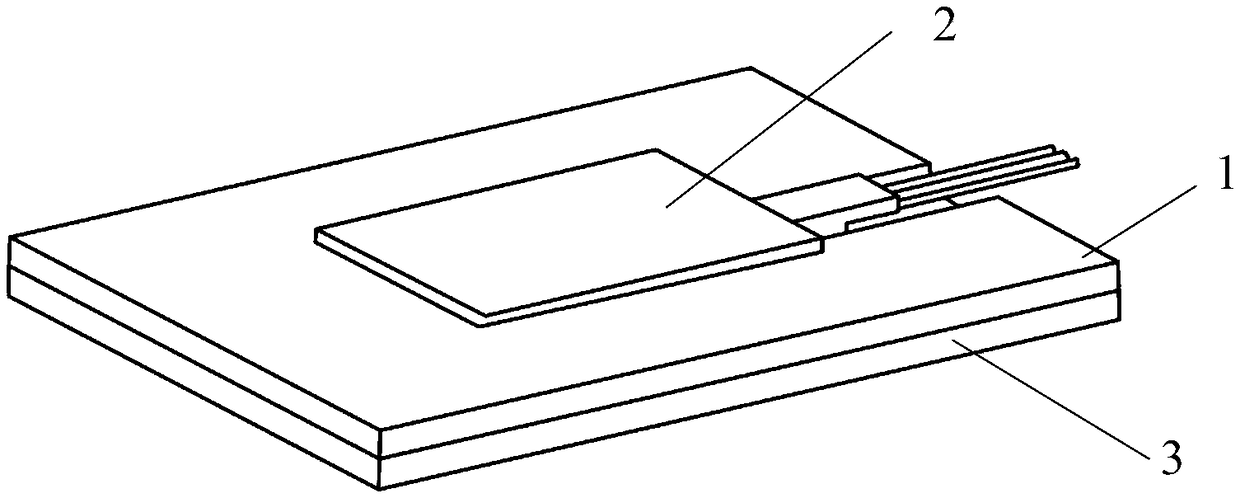

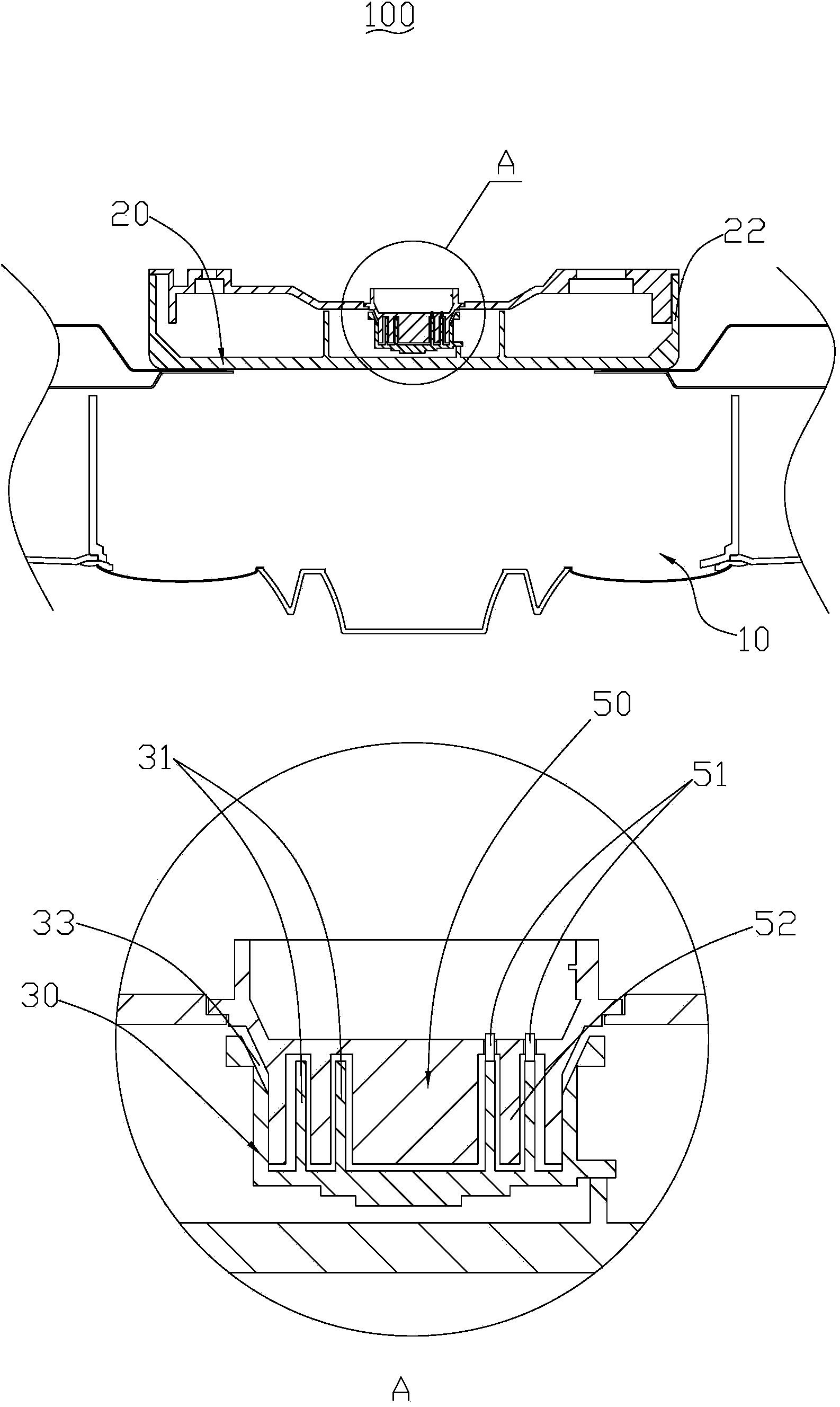

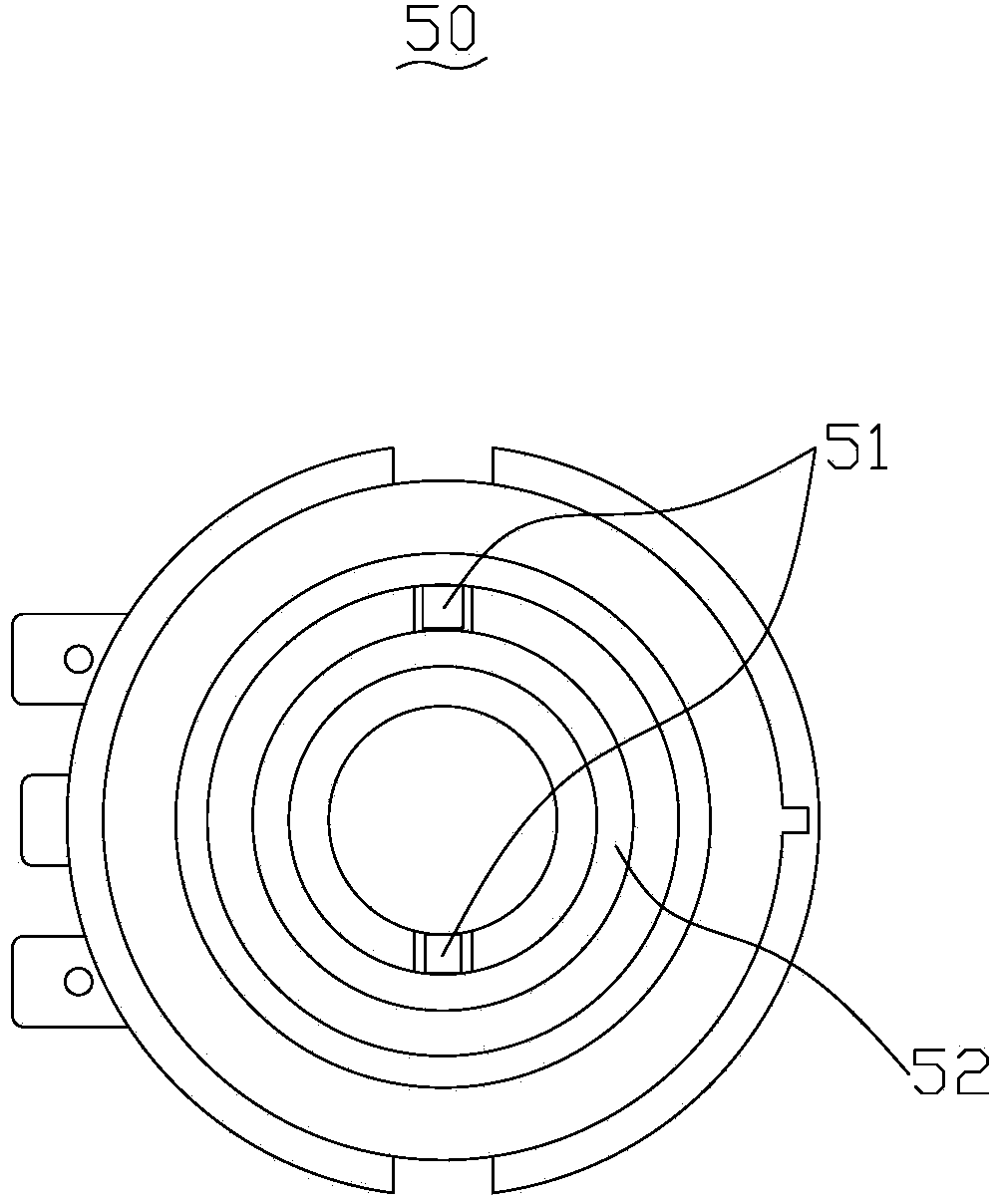

Camera module

InactiveCN104580857ALower the altitudeSufficient space for wiringTelevision system detailsColor television detailsFlexible circuitsCamera module

A camera module comprises a substrate, an image sensing chip and a plurality of conductive leads, wherein the substrate comprises a first PCB (printed circuit board), a double-sided FPC (flexible printed circuit board) and a second PCB which are laminated sequentially to form a circuit board with a multi-layer structure, and sufficient wiring space is guaranteed accordingly; a plurality of first welding pads are arranged on an exposed upper surface of the double-sided FPCB; a plurality of second welding pads are arranged on the upper surface of the image sensing chip; one end of each conductive lead is connected with one first welding pad, and the other end is connected with one corresponding second welding pad, so that the image sensing chip is electrically connected with the substrate; further, a first through hole is formed in the first PCB, and the image sensing chip is arranged in the through hole. Therefore, the total height after the image sensing chip is assembled with the substrate is smaller than the height sum of the image sensing chip and the flexible substrate, the height of the camera module can be reduced effectively, and the development requirement for light, thin, short and small tendency day by day can be met.

Owner:NANCHANG O FILM OPTICAL ELECTRONICS TECH CO LTD +3

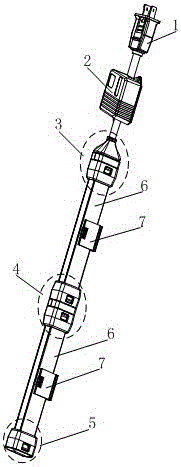

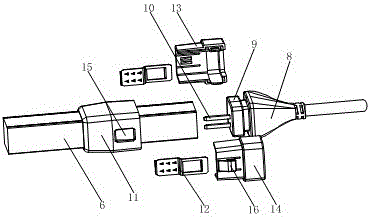

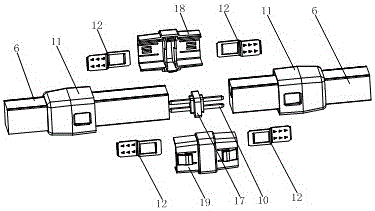

Liquid-cooled cable connecting assembly and connector

PendingCN107887730ASimple structureEasy to operateVehicle connectorsCoupling contact membersElectrical conductorEngineering

The invention discloses a liquid-cooled cable connecting assembly and a connector. The liquid-cooled cable connecting assembly comprises liquid-cooled cable connectors. Each liquid-cooled cable connector comprises a cable tail terminal, a pin terminal and a cable, wherein the cable tail terminal is provided with a first accommodating cavity with one end opened and a first liquid flowing channel communicated with the first accommodating cavity; the pin terminal is provided with a second accommodating cavity with one end opened and a second liquid flowing channel communicated with the second accommodating cavity; the cable comprises an insulating pipe and a conductor located inside the insulating pipe, two ends of the insulating pipe are respectively in sealed connection with the opened endsof the first accommodating cavity and the second accommodating cavity, two ends of the conductor extend to be inserted in the first accommodating cavity and the second accommodating cavity and are contacted with the cable tail terminal and the pin terminal respectively, and liquid flowing gaps are formed among the conductor and the first accommodating cavity, the second accommodating cavity and the inner wall of the insulating pipe. The liquid-cooled cable connecting assembly is simple in structure and convenient in operation, conduction of a coolant can be realized while electric connectionis ensured, and temperature rise of a contact piece at a heat source place can thus be controlled.

Owner:SHENZHEN WOER NEW ENERGY ELECTRICAL TECH CO LTD +2

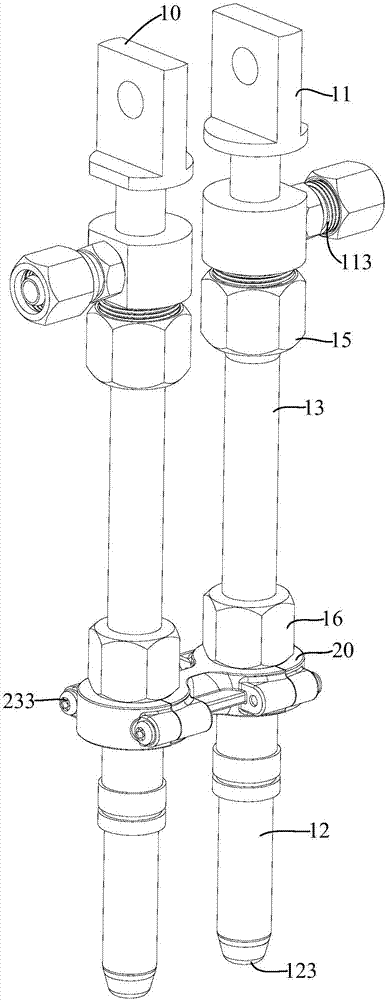

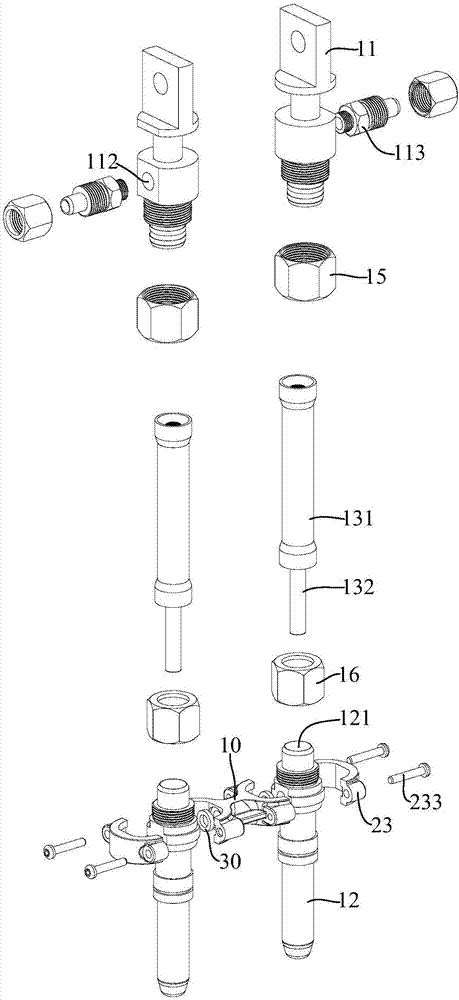

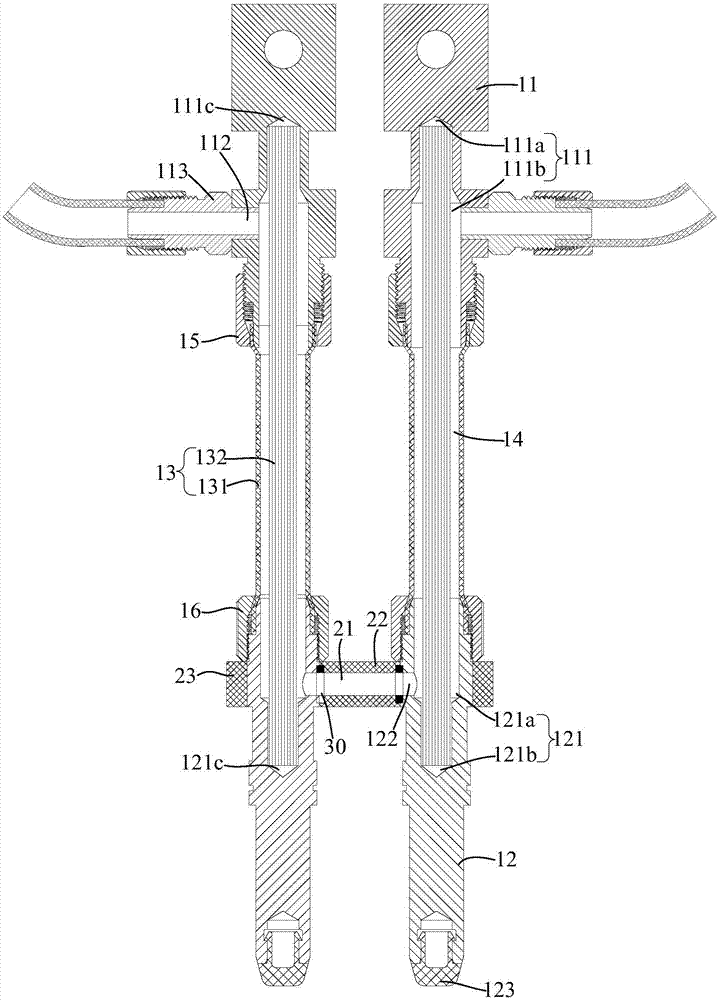

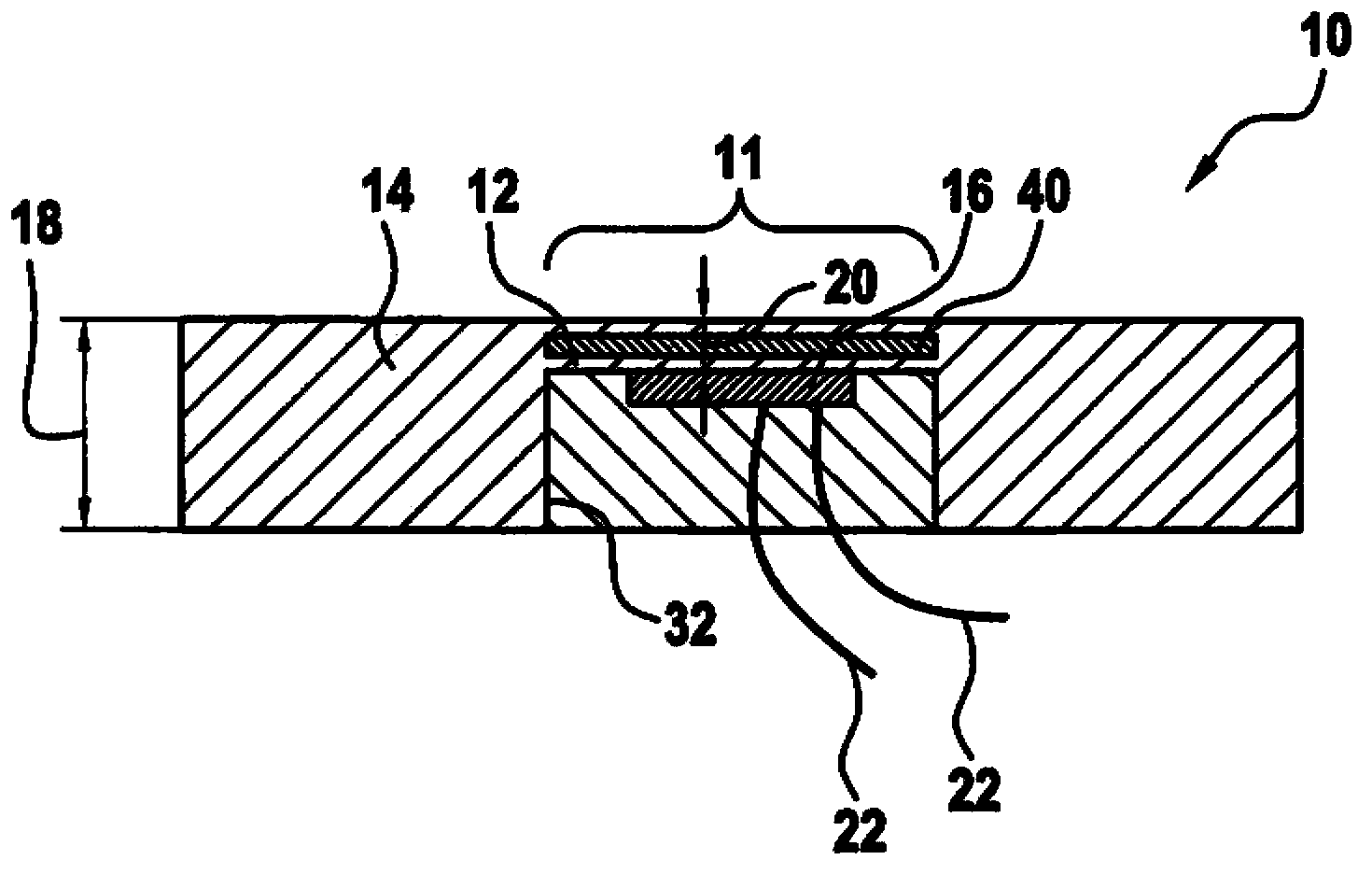

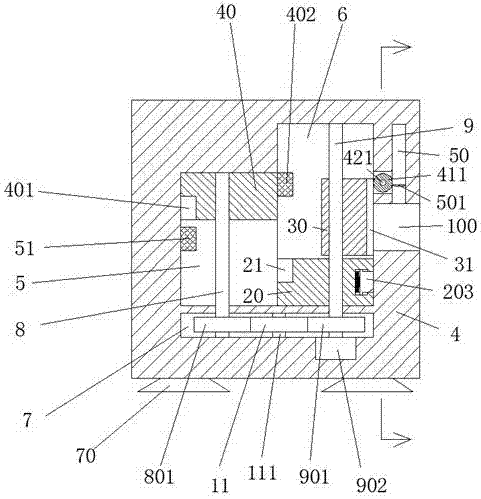

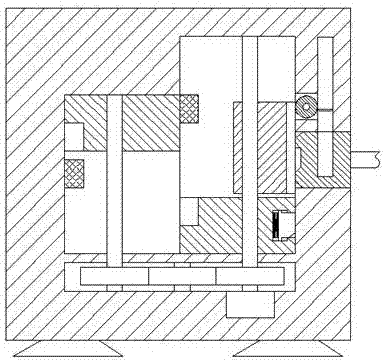

Carrier component with integrated sensor unit

InactiveCN103424181ASimple structureVersatileSubsonic/sonic/ultrasonic wave measurementUsing electrical meansFiberPiezoelectric actuators

This invention relates to a sensor assembly (10) compirsing at least one sensor unit (11).The sensor assembly (10) has a sensor unit (11), which is arranged in a support element (14) and a vibratable membrane (12) connected with a piezoelectric actuator (16). The membrane is positively integrated as a separate component or in the form of a fiber mat in the support element. A damping material (24) is applied on a vibratable portion (26) of the membrane. The membrane is designed as a separate component and the support element is made of different material. An independent claim is included for a method for producing a sensor assembly.

Owner:ROBERT BOSCH GMBH

Cell phone component

InactiveCN106992371AAchieve electrical connectionMake a power connectionCoupling contact membersTelephony connectorsElectricityPetroleum engineering

The invention discloses a cell phone component, comprising a housing sleeve and a power transmission end in electrical cooperation and connection with the housing sleeve. The housing sleeve comprises a left sliding cabin in the housing sleeve and a right sliding cabin in connection and communication with the left sliding cabin. The housing sleeve under the left sliding cabin and the right sliding cabin is provided with a toothed cabin. The central part at the right end part of the right sliding cabin is provided with a penetration groove in communication with the external part of the housing sleeve. The upper end part of the penetration groove is provided with a locking groove that extends upwards. Between the locking groove above the penetration groove and the right sliding cabin, a through hole communicates. A left sliding block is arranged in the left sliding cabin and can move upwards and downwards. The component of the invention has a simple structure, can be manufactured at a low cost, and can provide safe and stable power, effectively avoiding the occurrence of electrical shocks and ensuring the life safety of people. In addition, the power transmission operation is also convenient, meeting the use requirement for power transmission at present.

Owner:詹胜超

Semiconductor structure and formation method thereof

ActiveCN106558584ASimple forming processReduce process stepsSolid-state devicesSemiconductor devicesSemiconductor structureWork function

The invention provides a semiconductor structure and a formation method thereof. The semiconductor structure comprises a substrate; a first gate structure which is arranged on the surface of the substrate of the first regional part, wherein the first gate structure comprises a first work function layer; a second gate structure which is arranged on the surface of the substrate of the second regional part, wherein the second gate structure comprises a second work function layer, and the work function type of the second work function layer is different from the work function type of the first work function layer; an insulating layer which is arranged on the surface of the substrate of the third regional part, wherein the insulating layer covers the surface of the side wall of the first gate structure and the surface of the side wall of the second gate structure; an upper dielectric layer which is arranged on the top surface of the first gate structure, the top surface of the second gate structure and the top surface of the insulating layer; an opening which is arranged in the upper dielectric layer, wherein the top part of a first metal gate, the top part of a second metal gate and the top part of the insulating layer are exposed out of the bottom part of the opening; and a conductive layer which fully fills the opening, wherein the conductive layer is electrically connected with the first metal gate and the second metal gate. The electrical performance of the semiconductor structure can be improved by the semiconductor structure and the formation method thereof.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

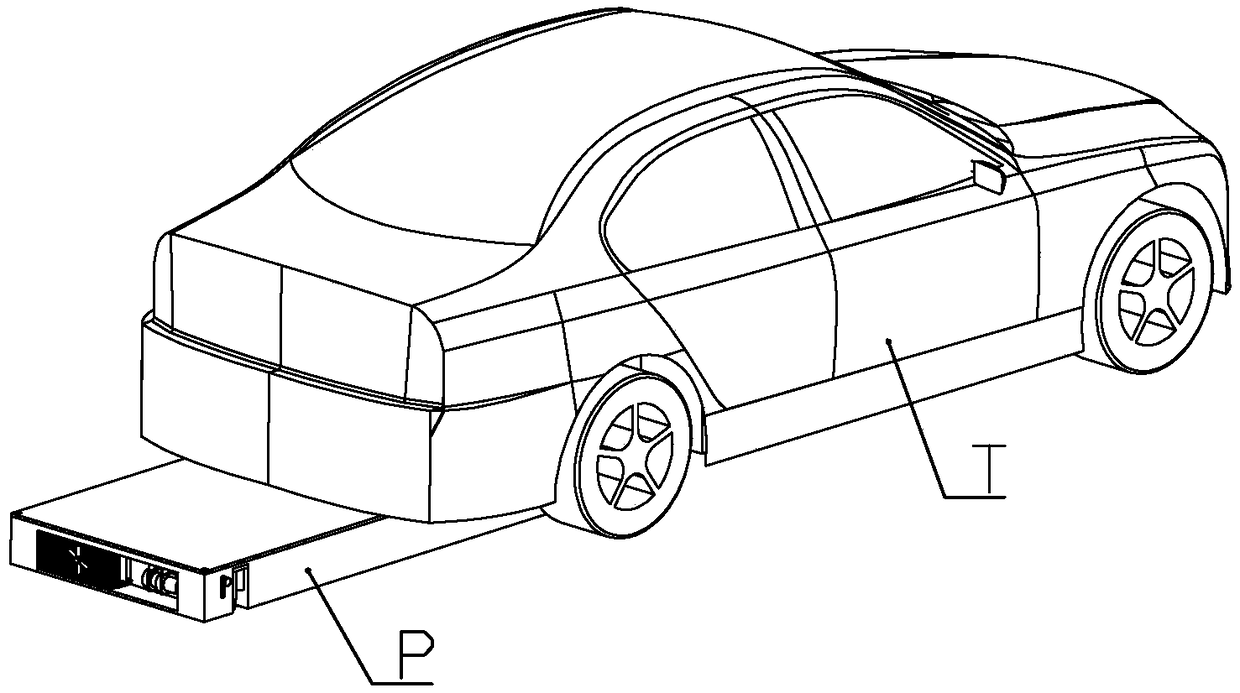

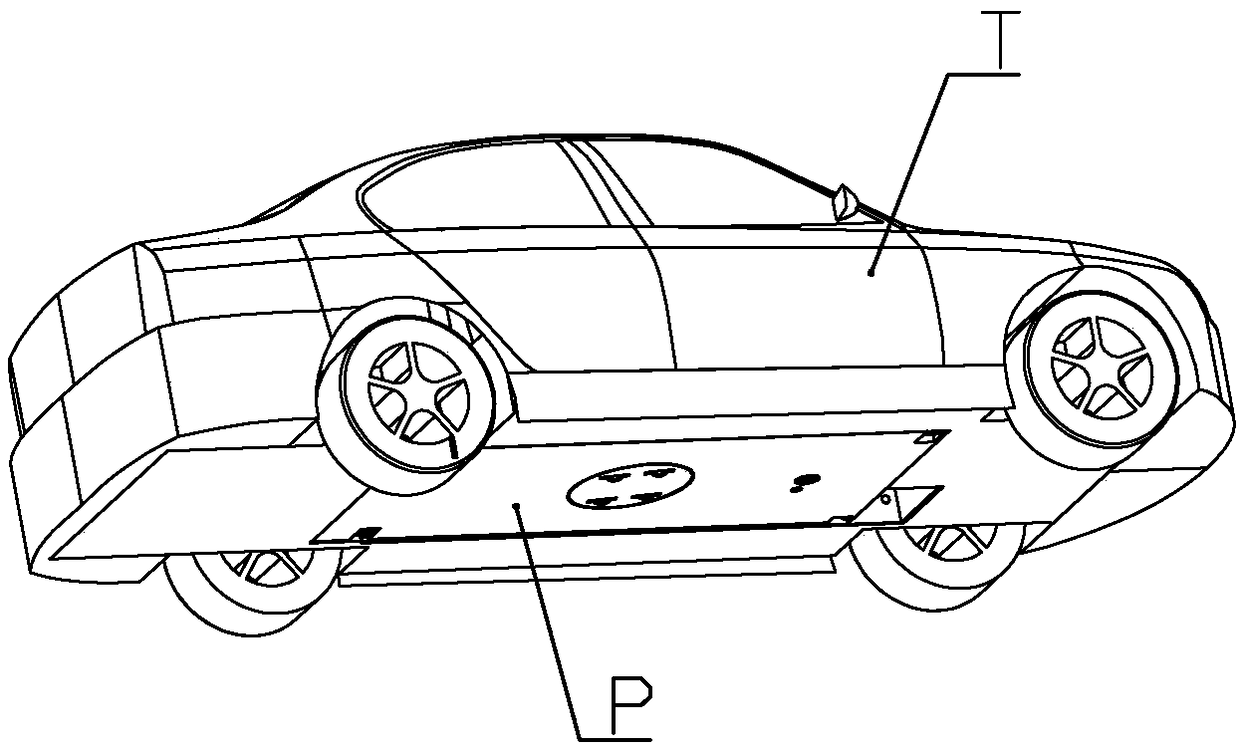

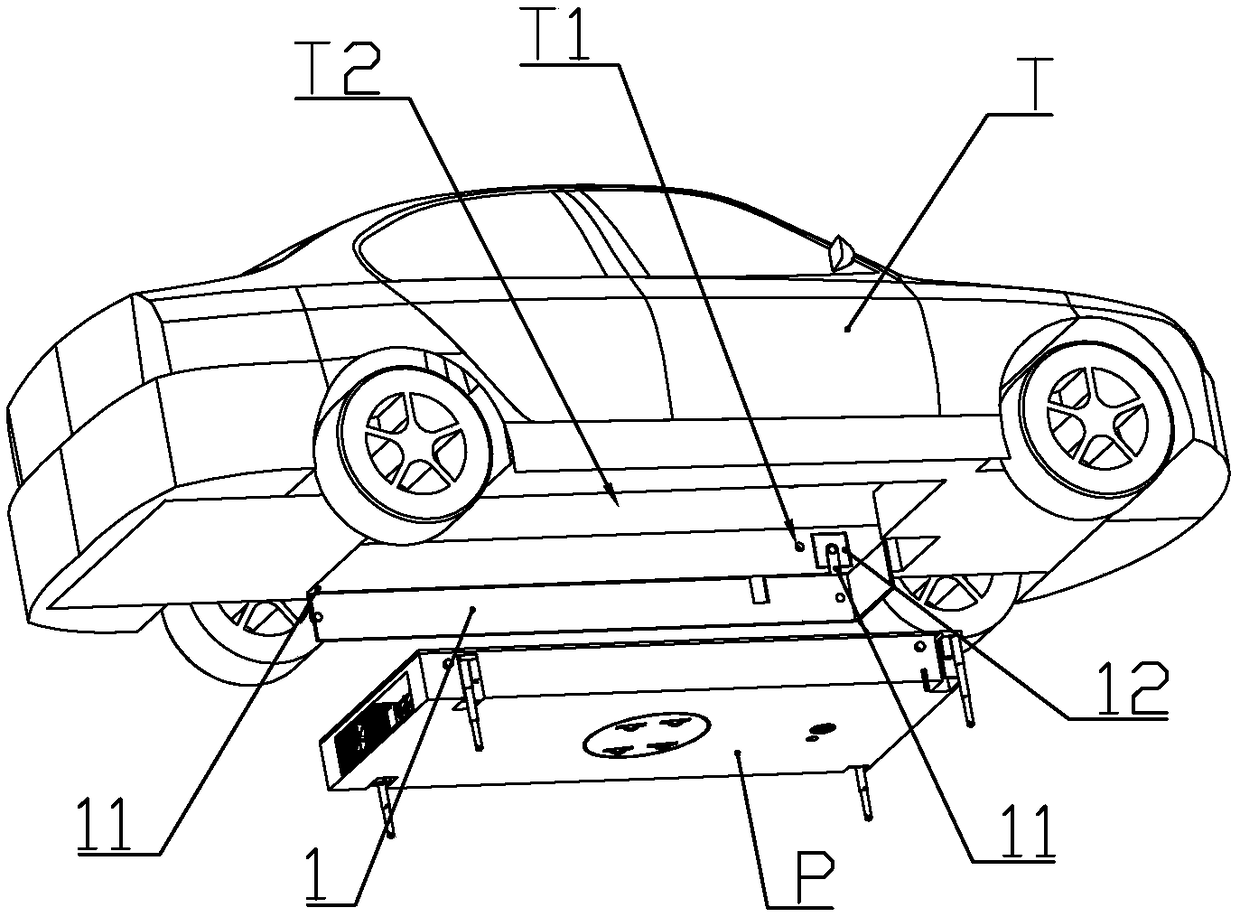

Battery component of new-energy electric automobile

InactiveCN108715129AEasy to moveSave spaceCharging stationsCell temperature controlRemote controlNew energy

The invention discloses a battery component of a new-energy electric automobile. The battery component is detachably installed at the lower end of an automobile body of the electric automobile; a battery installing groove for containing the battery component is formed in the lower end of the automobile body, and a positioning baffle is installed in the battery installing groove along the left sideof the automobile body in the length direction, and makes the battery component aligned with the battery installing groove when the battery component is installed in the battery installing groove. Byarranging a movable trolley at the lower end of the battery component, the battery component can move under remote control when separating from the automobile body; in addition, vertically-arranged electric pushing rods are installed on the two sides of the battery component, and in this way, when the battery component is installed on the automobile body, the battery component can be lifted intothe battery installing groove in the bottom of the automobile body only by moving the battery component to the position under the battery installing groove via the movable trolley and then controllingthe electric pushing rods to lengthen.

Owner:JIANGSU CERA THERMAL TECH

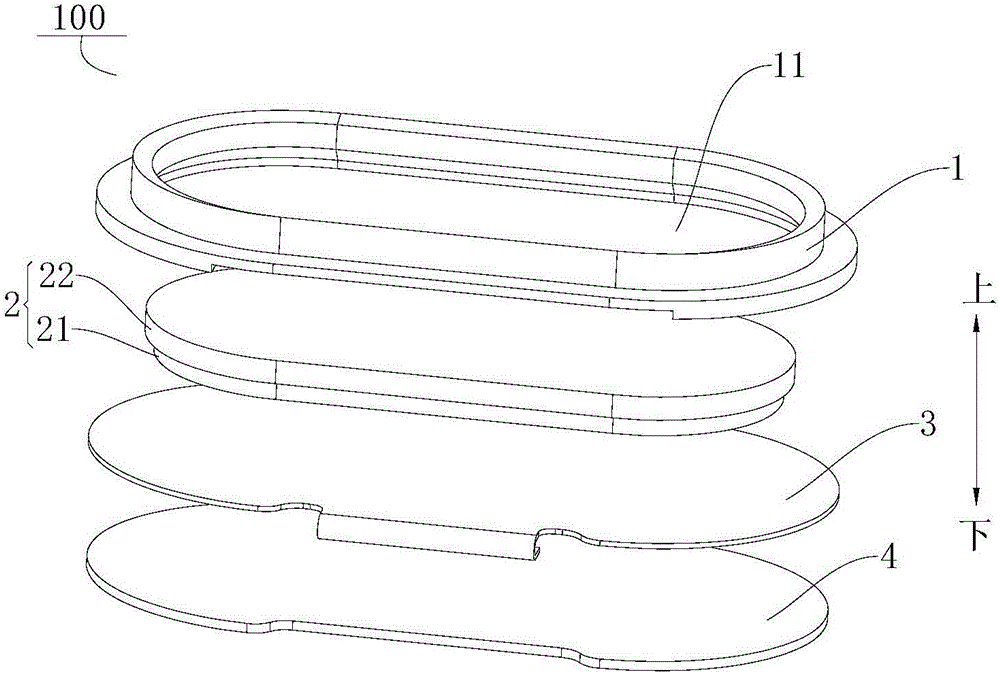

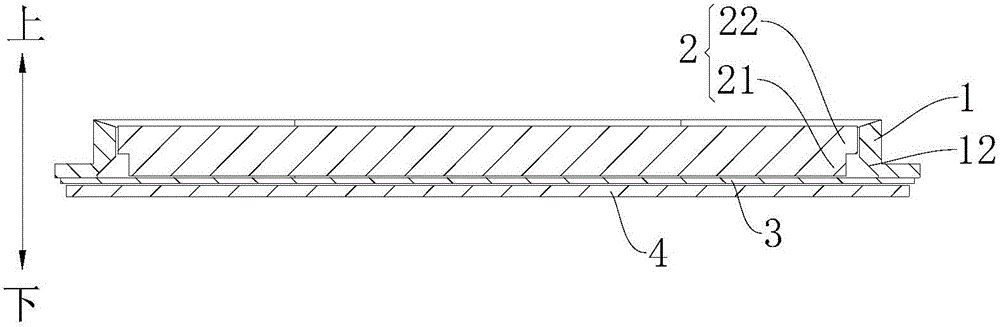

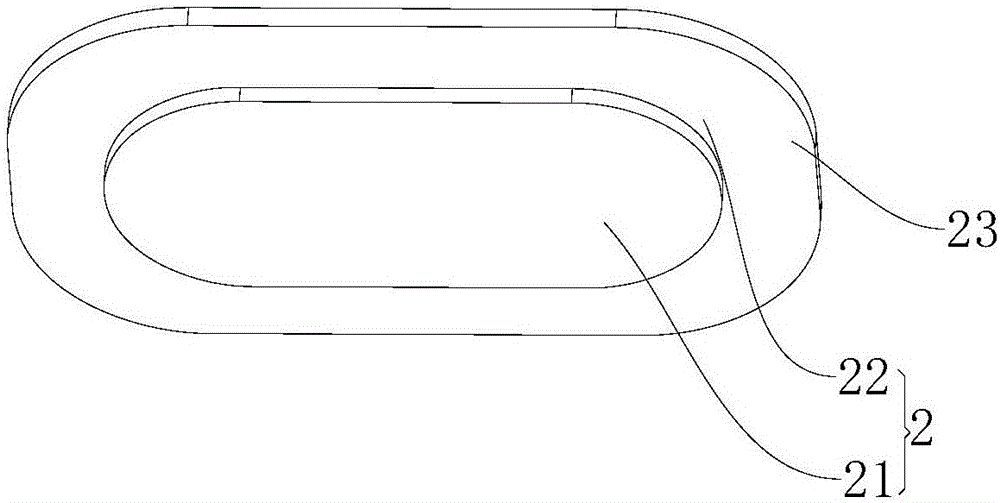

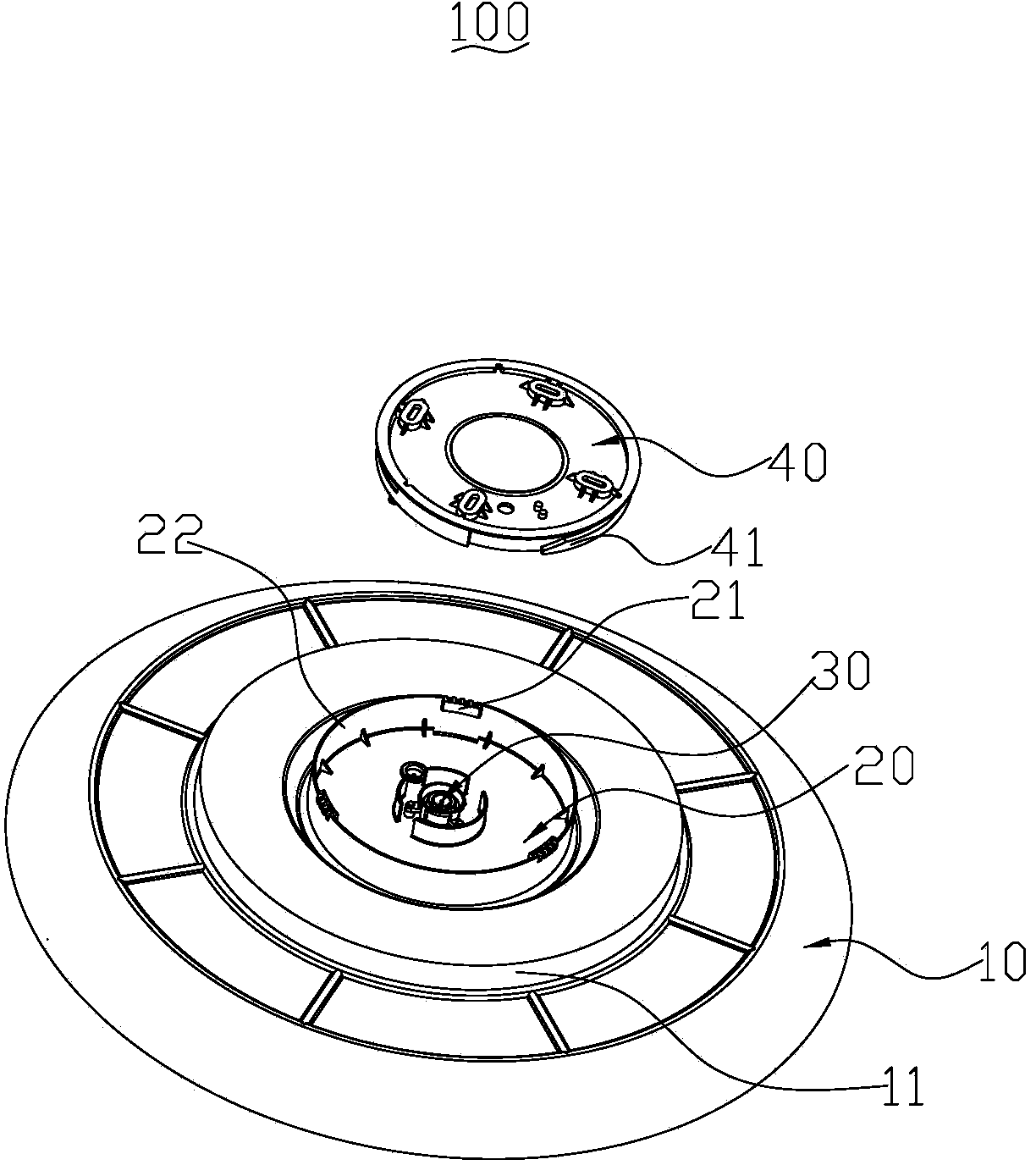

Quickly mounted ceiling lamp

InactiveCN104359057AAchieve electrical connectionEasy to installLighting support devicesPoint-like light sourceElectricityBiochemical engineering

The invention discloses a quickly mounted ceiling lamp which comprises a lamp body, an upper cover, a lower cover and spiral buckle structures, wherein the lamp body is fixed on the lower cover; the spiral buckle structures are respectively arranged on the upper cover and the lower cover; the upper cover and the lower cover can be buckled or separated through the spiral buckle structures; the quickly mounted ceiling lamp is characterized in that an electricity lead-in base is also arranged in the center of the lower cover; two electrode joints are arranged in the electricity lead-in base; an upper electricity lead-in seat corresponding to the electricity lead-in base is arranged on the upper cover; two electrode contacts are arranged in the upper electricity lead-in seat; during assembling, the upper electricity lead-in seat is plugged into the electricity lead-in base in a rotatable manner; in a spirally buckling process of the spiral buckle structures, the two electrode contacts are always electrically connected with the two electrode joints. When the quickly mounted ceiling lamp is mounted, electric connection and mounting can be realized without detaching a lampshade; the quickly mounted ceiling lamp has the advantage of being stable and convenient in mounting.

Owner:LEEDARSON IOT TECH INC

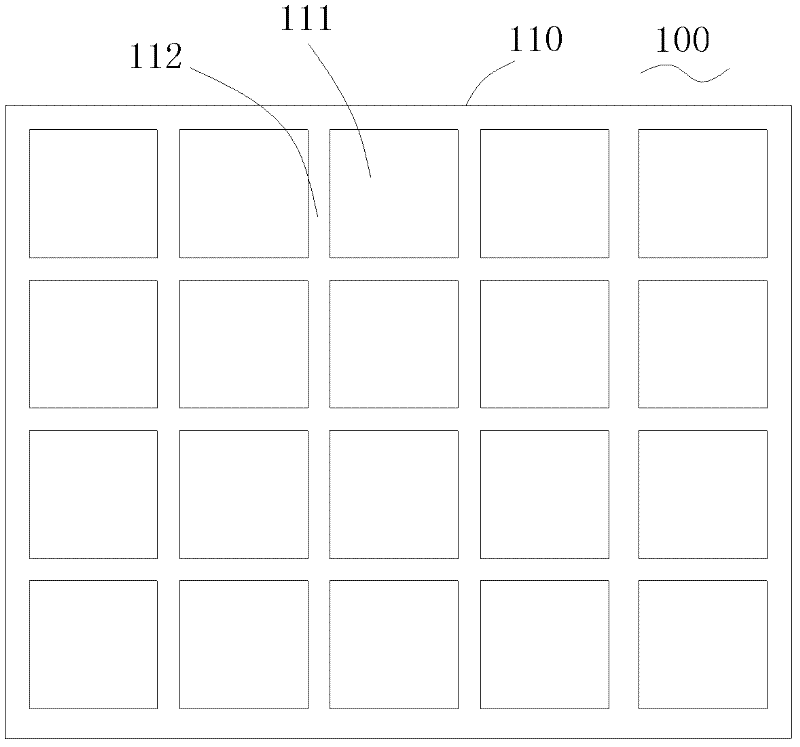

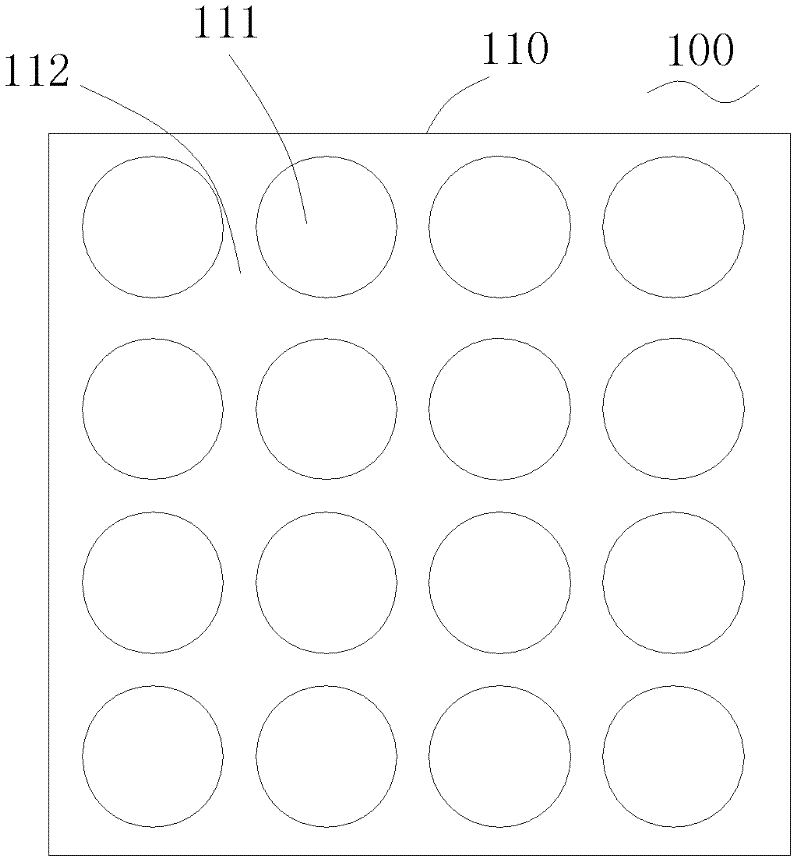

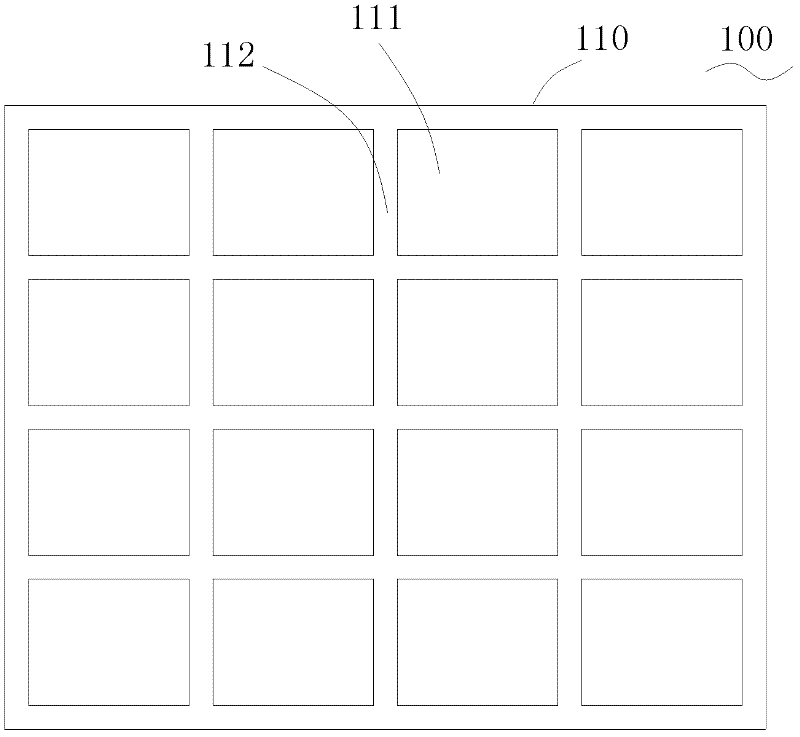

Connector for measurement of electric resistance, connector device for measurement of electric resistance and production process thereof, and measuring apparatus and measuring method of electric resis

InactiveCN1764844AHigh precision expectation measurementAchieve electrical connectionResistance/reactance/impedenceElectronic circuit testingElectrical resistance and conductanceMeasurement device

Disclosed herein are a connector for measuring resistance, a connector device for measuring resistance and a manufacturing method thereof, and a measuring device and method for circuit boards, by which even when the area of the circuit board to be inspected Even when there are multiple electrodes to be inspected that are small in size, the necessary electrical connections must also be made, and the desired resistance measurement must be performed with high precision. According to the present invention, a connector for measuring resistance includes an insulating substrate and is arranged on the front surface of the insulating substrate according to a pattern corresponding to a pattern of a plurality of electrodes to be inspected in a circuit board to be inspected whose resistance is to be measured. multiple connected electrode sets. Each of the above-mentioned connecting electrode groups is composed of at least 3 electrodes of an electrode for current supply and an electrode for voltage measurement arranged separately from each other, at least one of these electrodes is an electrode for current supply, and at least one of is the electrode used for voltage measurement.

Owner:JSR CORPORATIOON