Integrally-packaged power semiconductor device

A technology of power semiconductors and devices, which is applied in the direction of semiconductor devices, semiconductor/solid-state device components, electric solid-state devices, etc., can solve the problems of difficult chip flipping and installation, and the inability to obtain exposed chip bases, etc., to achieve the effect of improving product performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1-1

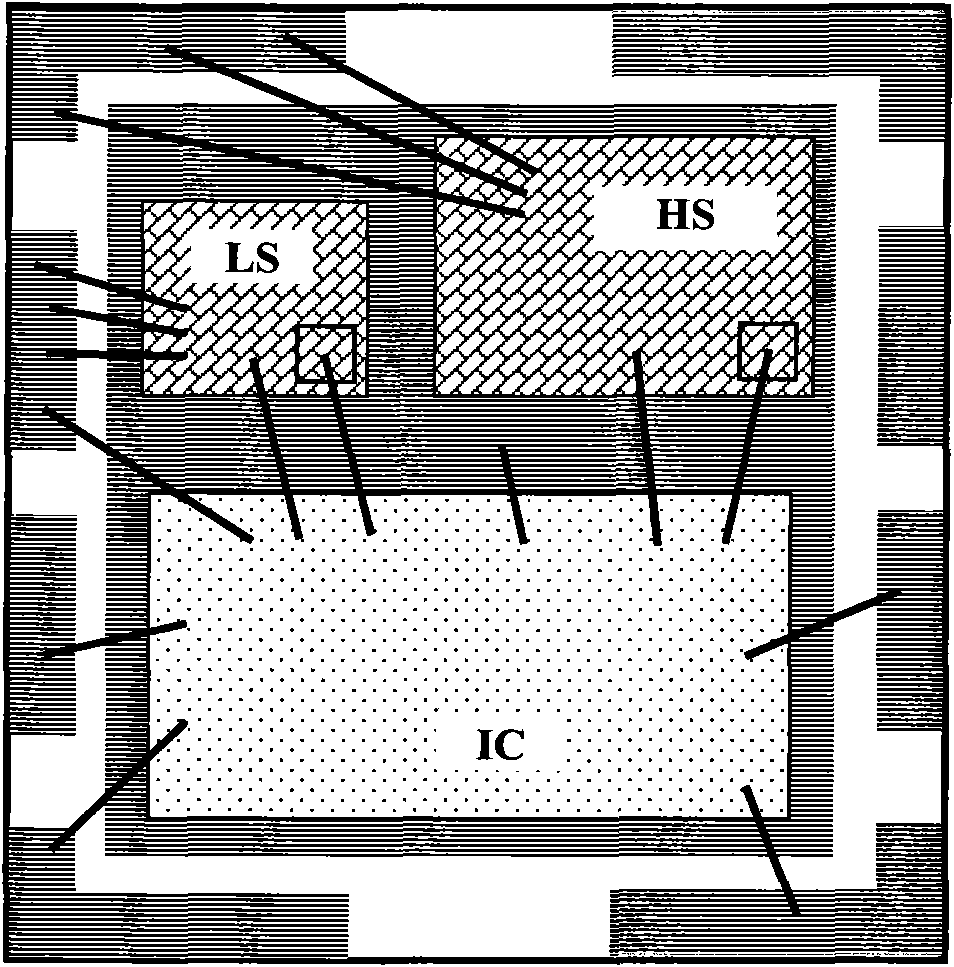

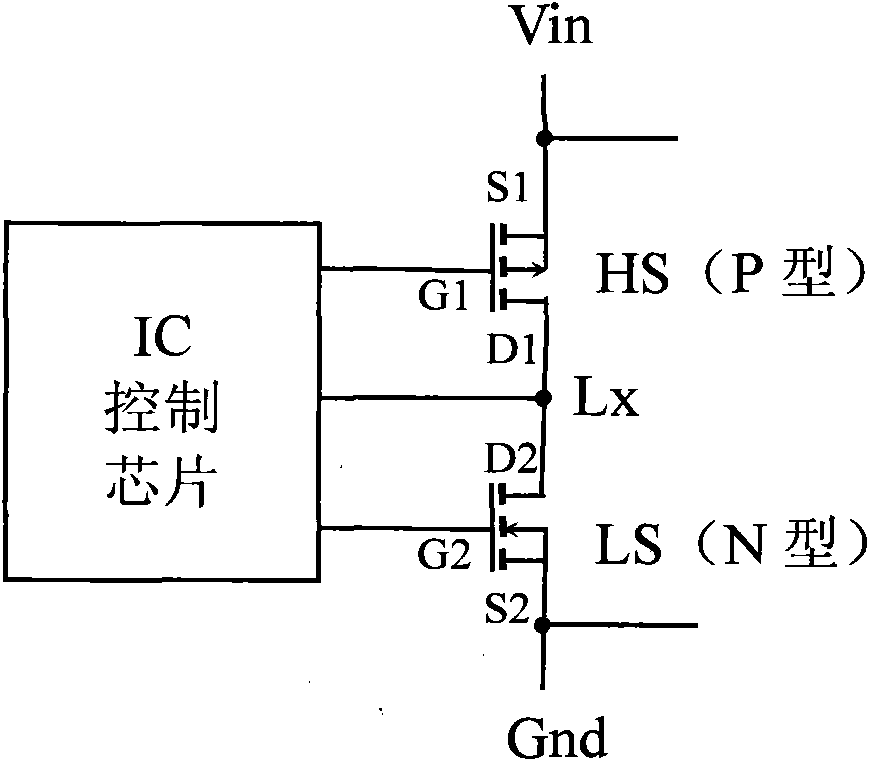

[0081] Please refer to figure 2 , Figure 4 , Figure 6 Shown is an implementation structure of the power semiconductor device of the present invention, wherein Figure 4 is a schematic diagram of the overall structure of the power semiconductor device, Figure 6 yes Figure 4 Sectional view of position A-A in the center. correspond figure 2 It can be seen from the schematic circuit diagram that the P-type high-end MOSFET chip 30 , the N-type low-end MOSFET chip 20 and the control chip 40 are jointly packaged in the power semiconductor device.

[0082] The power semiconductor device includes a lead frame, on which a chip base 100 is arranged, and several pins separated from the chip base 100 and not electrically connected.

[0083] The high-end and low-end MOSFET chips are respectively provided with a bottom drain, a top source, and a top gate; correspondingly, the plurality of pins include a high-end source pin 72, a low-end gate pin 71, a switch pin 74 and several c...

Embodiment 1-2

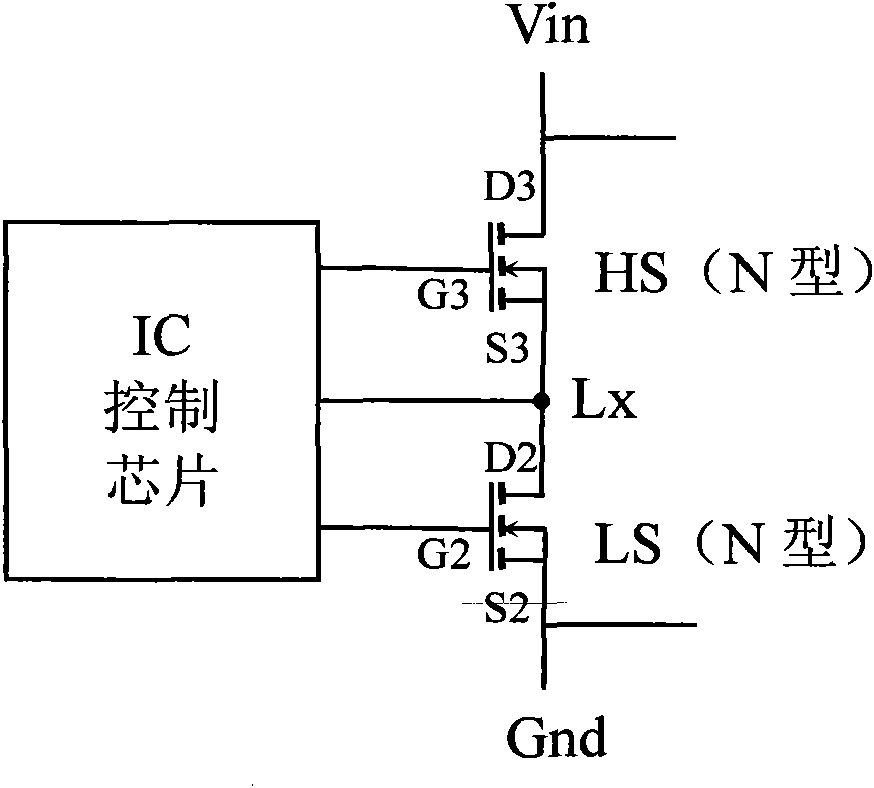

[0095] Please refer to image 3 , Figure 5 , Figure 6 , Figure 7 shown, where Figure 5 is a schematic diagram of the overall structure of the power semiconductor device, Figure 6 yes Figure 5 The cross-sectional view of the A-A position in the middle, Figure 7 yes Figure 5 Sectional view of position C-C in middle. correspond image 3 It can be seen from the schematic circuit diagram that the control chip 40 and N-type high-end and low-end MOSFET chips are jointly packaged in the power semiconductor device.

[0096] The chip base 100 described in this embodiment and the lead frame structure of several pins separated therefrom are the same as in the above-mentioned embodiment; The same applies to the examples. A brief description is as follows:

[0097] Cooperate see Figure 5 , Figure 6 and Figure 8 As shown, the low-side MOSFET chip 20 is turned over and bonded on the chip base 100, its top source 22 is electrically connected to the chip base 100, and i...

Embodiment 2-1

[0105] Please refer to figure 2 , Figure 9 , Figure 11 shown, where Figure 9 is a schematic diagram of the overall structure of the power semiconductor device, Figure 11 yes Figure 9 Sectional view of the B-B position in the middle. correspond figure 2 It can be seen from the schematic circuit diagram that the P-type high-end MOSFET chip 30 , the N-type low-end MOSFET chip 20 and the control chip 40 are jointly packaged in the power semiconductor device.

[0106] Similar to Embodiment 1-1, in this embodiment, a control chip 40 is provided at one end of the chip base 100 of the lead frame, and an inverted low-end MOSFET chip 20, a first metal connecting plate 51, The high-side MOSFET chip 30 and the second metal connecting plate 52 . Wherein, the first metal connecting plate 51 is electrically connected to the bottom drains 23 and 33 of the high-side and low-side MOSFET chips on its top surface and bottom surface, respectively, and is connected to the switch pin 7...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More