Semiconductor structure and forming method thereof

A technology of semiconductor and gate structure, applied in the field of semiconductor structure and its formation, can solve the problems of semiconductor device performance obstruction, reduce carrier mobility in the channel region of PMOS transistor, etc., and achieve reduced tensile stress, good performance, and increased effect of distance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] As mentioned in the background, the tensile stress provided by the conductive layer to the PMOS fin field effect transistor will reduce the mobility of carriers in its channel region and reduce the performance of the semiconductor device.

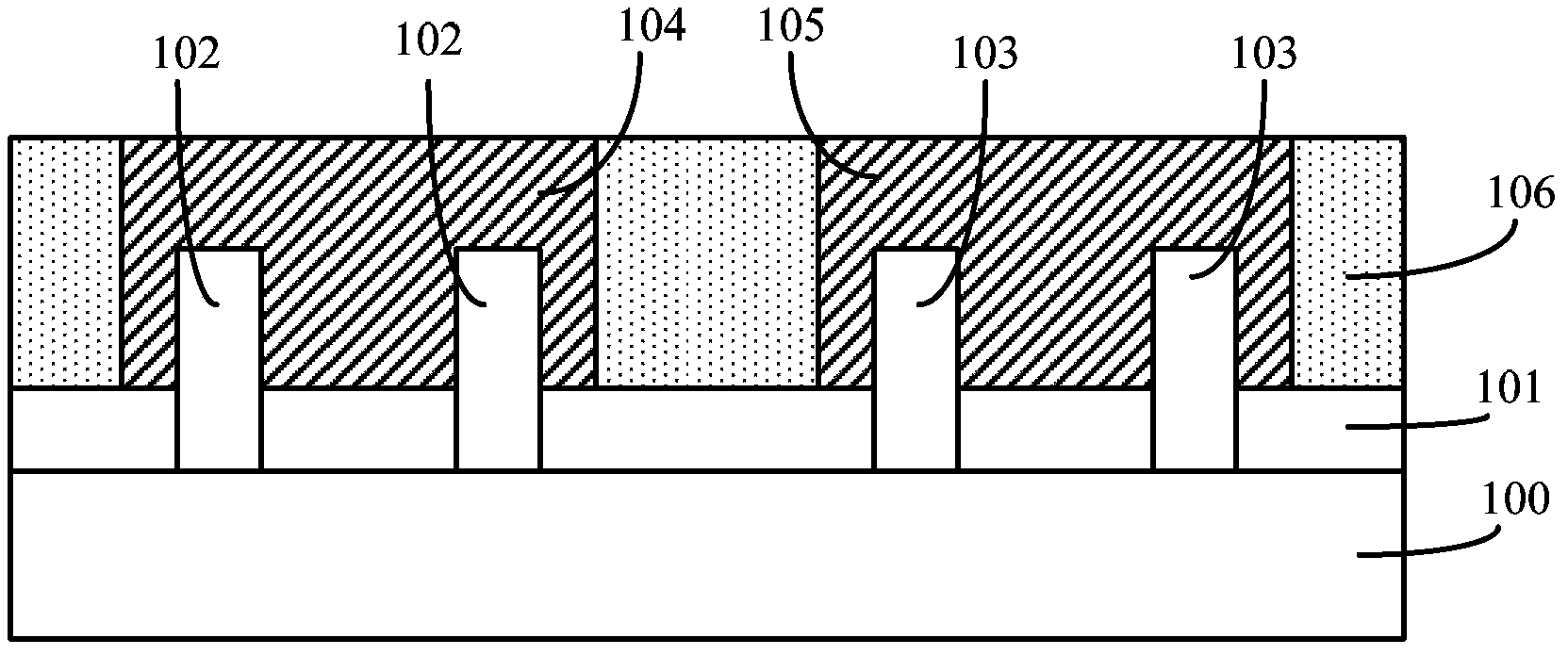

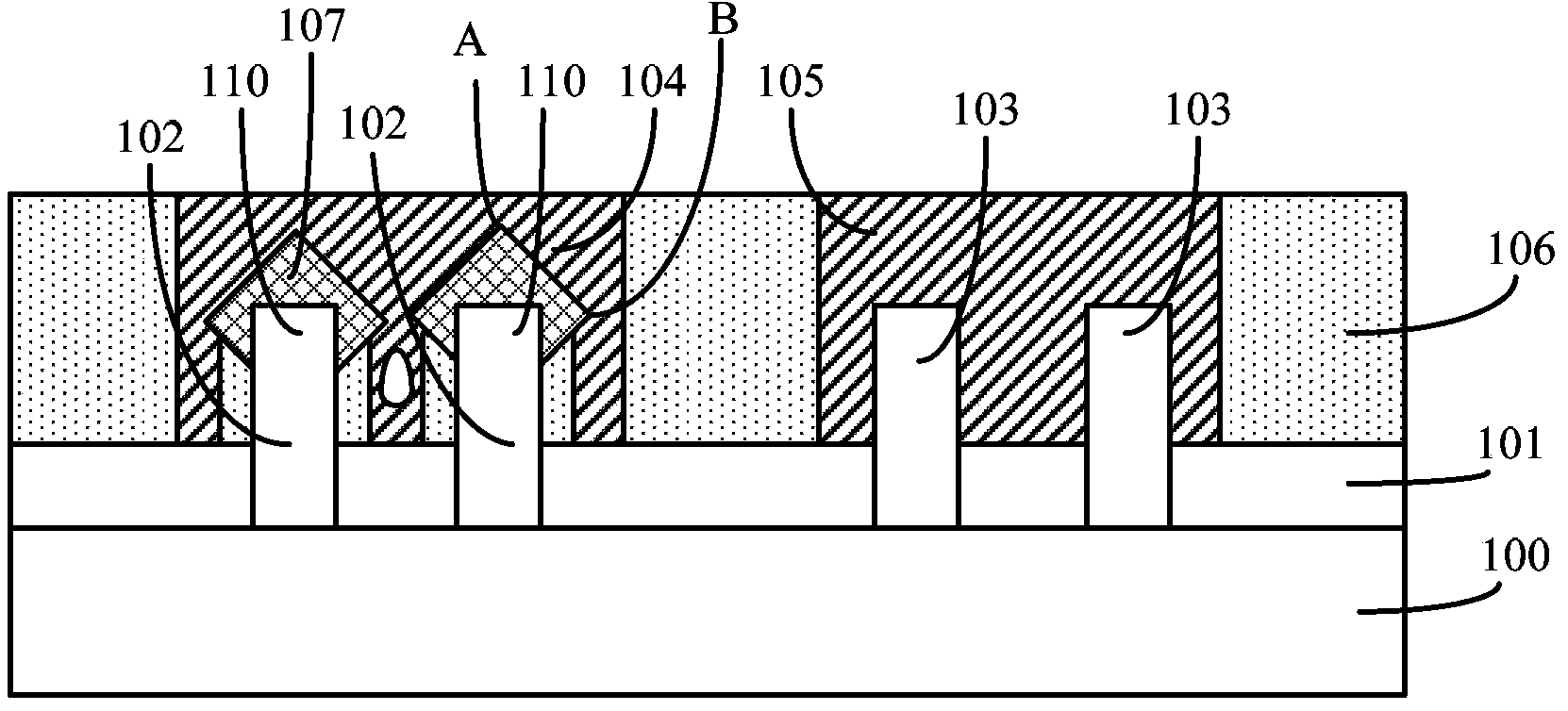

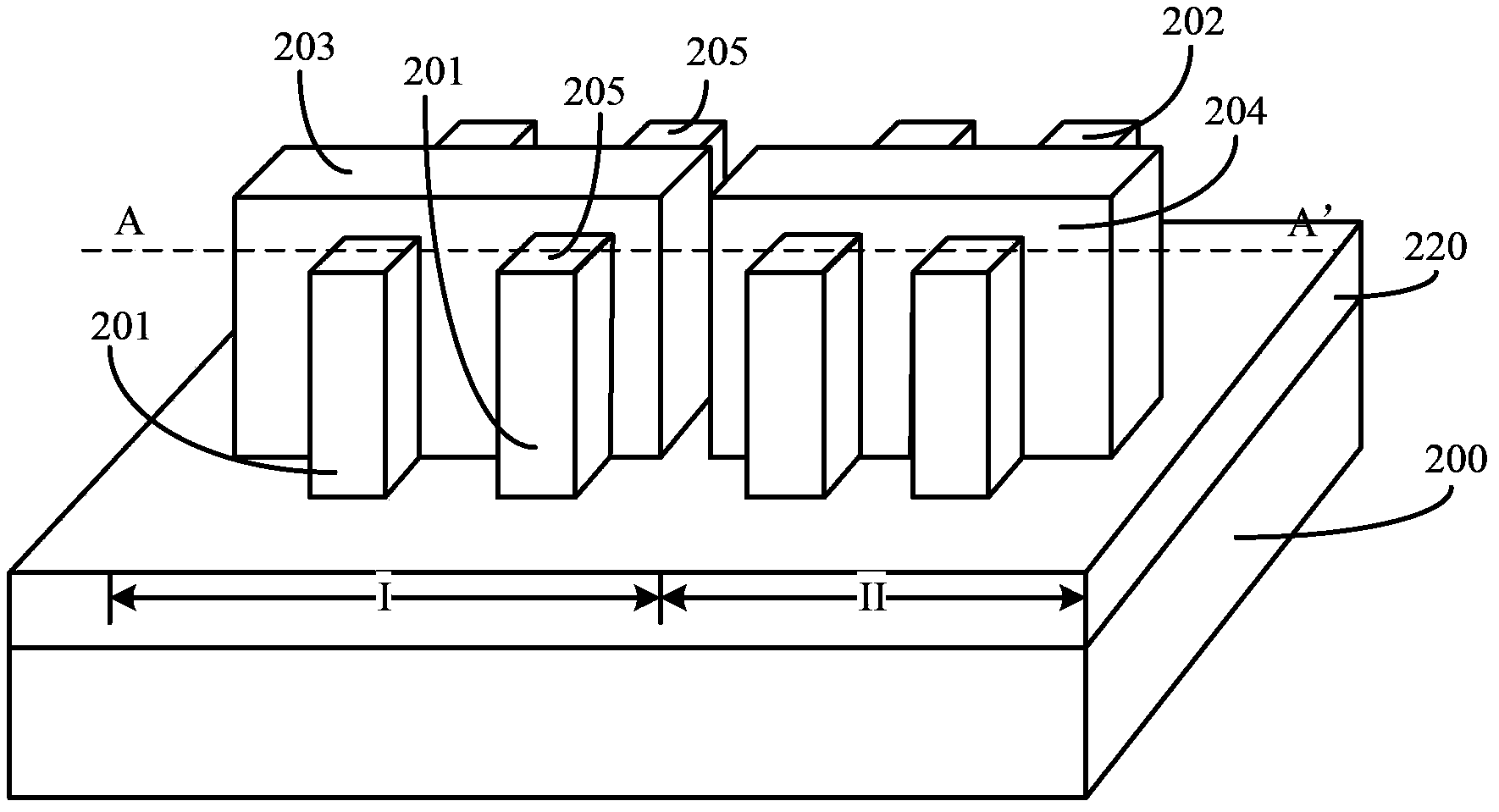

[0034] After research by the inventors of the present invention, a PMOS fin field effect transistor with raised source and drain regions (raised source / drain) is proposed. Such as figure 2 Shown is a schematic diagram of the cross-sectional structure of a fin field effect transistor with raised source and drain regions. figure 1On the basis of the above, it also includes: the source region and the drain region 110 located in the first fin portion 102; the semiconductor layer 107 located on the top and part of the sidewall surface of the source region and the drain region 110 of the first fin portion 102, the semiconductor layer The portion 107 located on the top surface of the first fin portion 102 has a raised corner A, and the fi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More