A 4h-sic metal-semiconductor field-effect transistor with multiple recessed buffer layers

A field-effect transistor and metal-semiconductor technology, which is applied in the field of 4H-SiC metal-semiconductor field-effect transistors, can solve problems such as the large influence of saturation leakage current, and achieve improved breakdown voltage, increased gate transconductance, and increased transconductance Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

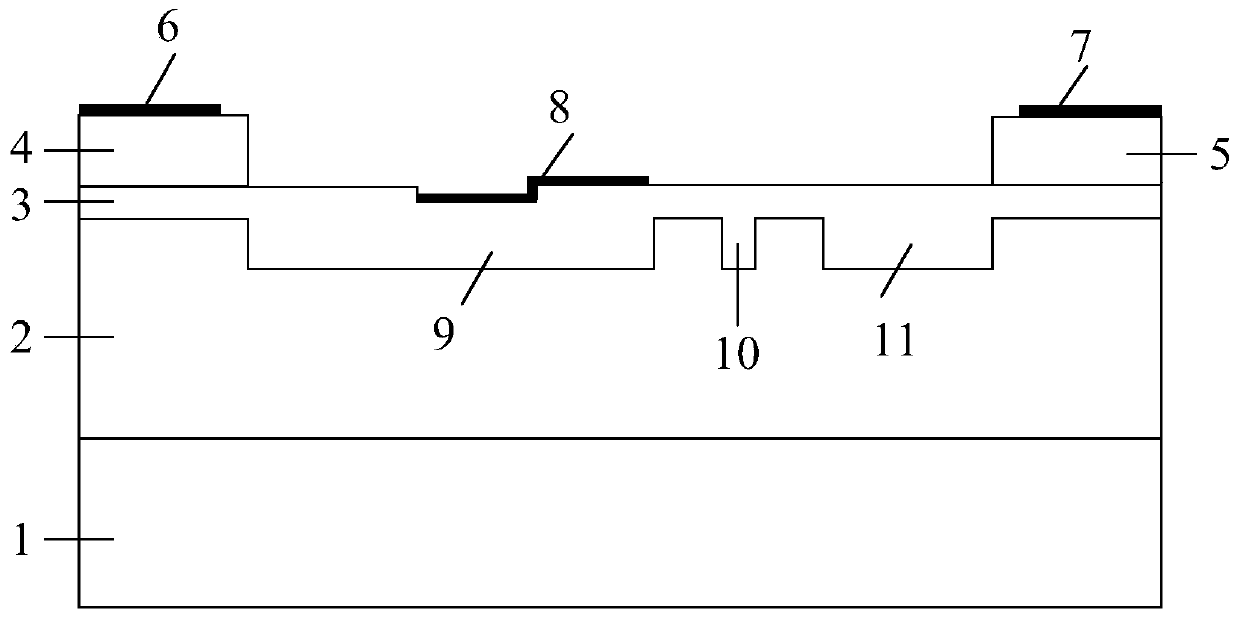

[0025] A 4H-SiC metal-semiconductor field-effect transistor with multiple recessed buffer layers, comprising a 4H-SiC semi-insulating substrate (1), a P-type buffer layer (2), and an N-type channel layer (3) from bottom to top, The two sides of the N-type channel layer (3) are respectively a source cap layer (4) and a drain cap layer (5), and the surfaces of the source cap layer (4) and the drain cap layer (5) are respectively source electrodes ( 6) and the drain electrode (7), the gate electrode (8) is formed on the side of the N-type channel layer (3) and close to the source cap layer, and the upper end surface of the buffer layer is provided below the gate electrode and the gate source The first buffer layer recessed area (9), the second buffer layer recessed area (10) is provided on the side near the gate under the gate drain, and the third buffer layer is provided on the side near the drain cap layer below the gate drain Depressed area (11).

Embodiment 2

[0027] In this embodiment, the depth of the P-type buffer layer (2) is 0.65 μm, and the first buffer layer recessed area (9), the second buffer layer recessed area (10), and the third buffer layer recessed area (11) The depths are all 0.15 μm.

[0028] The remaining technical solutions of this embodiment are consistent with Embodiment 1.

Embodiment 3

[0030] In this embodiment, the depth of the P-type buffer layer (2) is 0.6 μm, and the first buffer layer recessed area (9), the second buffer layer recessed area (10), and the third buffer layer recessed area (11) The depths are all 0.1 μm.

[0031] The remaining technical solutions of this embodiment are consistent with Embodiment 1.

PUM

| Property | Measurement | Unit |

|---|---|---|

| depth | aaaaa | aaaaa |

| depth | aaaaa | aaaaa |

| depth | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More