Method for keeping consistent phase of frequency division clock and frequency division circuit

A frequency division clock and frequency division circuit technology, applied in electrical components, counting chain pulse counters, pulse counters, etc., to achieve the effect of easy implementation, ensuring phase consistency, and ensuring correctness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] In order to understand the characteristics and technical contents of the embodiments of the present invention in more detail, the implementation of the embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings. The attached drawings are only for reference and description, and are not intended to limit the embodiments of the present invention.

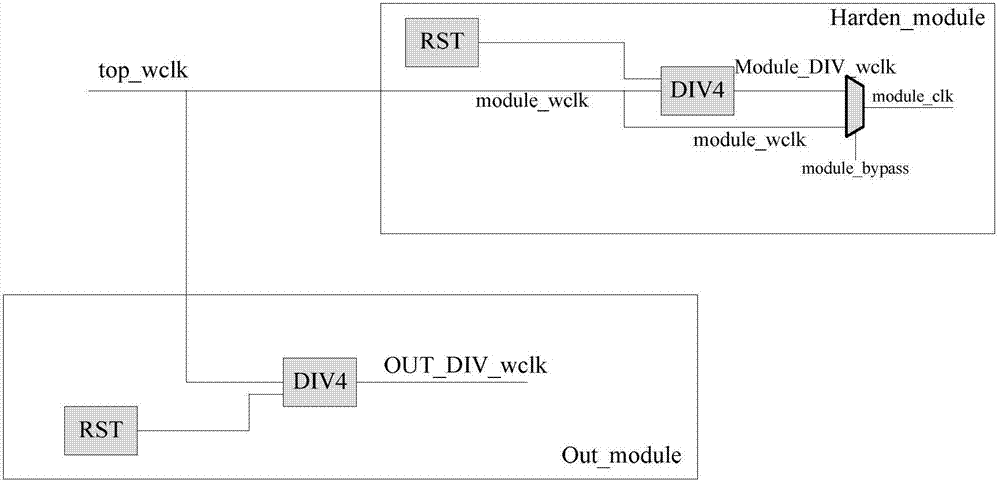

[0033] With the continuous increase of the SOC design scale, many individually hardened (harden) modules appear in the chip design, called hardened modules. Some of the clock relationships of these hardened modules are relatively complex and diverse. The case of distributed clock frequency division. like figure 1 As shown, the Harden_module module is cured separately and is a cured module. The clock required by this module is also relatively complicated, and the top_wclk clock needs to be input from the top layer of the chip, and the module_div_wclk clock is generated by...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More