Display device, array substrate and manufacturing method

A technology of an array substrate and a manufacturing method, applied in the field of liquid crystal displays, can solve problems such as reliability decline and semiconductor layer damage, and achieve the effects of improving reliability and avoiding damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

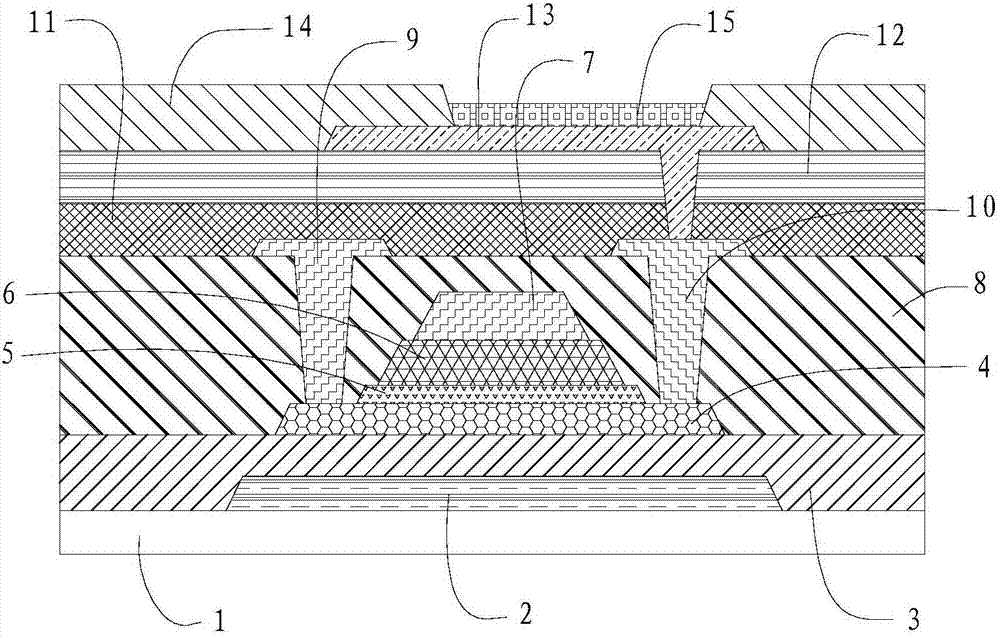

[0029] see figure 1 , figure 1 It is a schematic diagram of the mechanism after the formation of the pixel definition layer 14 and the arrangement of the organic light emitting diodes 15 in an array substrate manufacturing method of the present invention. from figure 1 It can be seen that an array substrate in this embodiment includes:

[0030] A light-shielding layer 2, a barrier layer 3, and a semiconductor layer 4 are sequentially formed on the base substrate 1 from bottom to top;

[0031] a first gate insulating layer 5, formed on one side of the semiconductor layer 4, and formed by a first method;

[0032] The second gate insulating layer 6 is formed on the side of the first gate insulating layer 5 facing away from the semiconductor layer 4, and is formed by a second method;

[0033] Wherein, the first method can protect the reliability of the semiconductor layer 4 .

[0034] In this embodiment, the array substrate of the present invention further includes a gate 7 f...

Embodiment 2

[0041] This embodiment provides a display device, which includes the array substrate 20 described in Embodiment 1, on which a corresponding driving circuit 30 is disposed. Since the array substrate 20 has been described in detail in the first embodiment, it will not be repeated here.

[0042] In a display device of the present invention, the array substrate 20 is deposited to form the first gate insulating layer 5 by atomic deposition, and the second gate insulating layer 6 is deposited by chemical vapor deposition to avoid damage to the semiconductor layer 4, Improving the reliability of thin film transistors and reducing the influence of atomic deposition on production efficiency due to low deposition rate can achieve a good balance between production efficiency and TFT reliability.

Embodiment 3

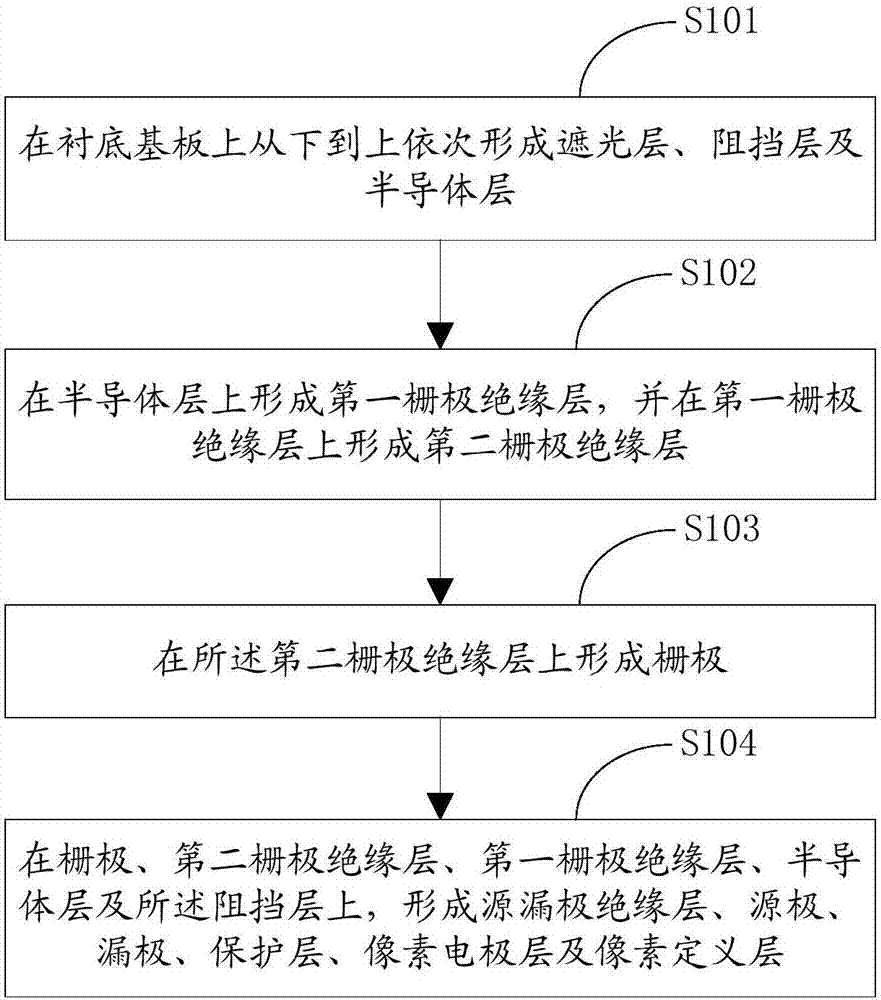

[0044] see image 3 , image 3 It is a flow chart of the overall implementation steps of a method for fabricating an array substrate in this embodiment. from image 3 It can be seen that a method for manufacturing an array substrate in this embodiment includes the following steps:

[0045] Step S101 : Forming a light-shielding layer 2 , a barrier layer 3 and a semiconductor layer 4 sequentially from bottom to top on the base substrate 1 . like Figure 4 as shown, Figure 4 It is a schematic diagram of the structure when the light shielding layer 2 , the blocking layer 3 and the semiconductor layer 4 are sequentially formed on the base substrate 1 in a method for fabricating an array substrate in this embodiment.

[0046] Step S102 : forming a first gate insulating layer 5 on the semiconductor layer 4 , and forming a second gate insulating layer 6 on the first gate insulating layer 5 .

[0047] In this step, the first gate insulating layer 5 is formed on one side of the s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More