Shifting registration unit and driving method thereof, and display panel

A technology of shift register units and transistors, which is applied in information storage, static memory, static indicators, etc., and can solve problems such as output instability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example 1

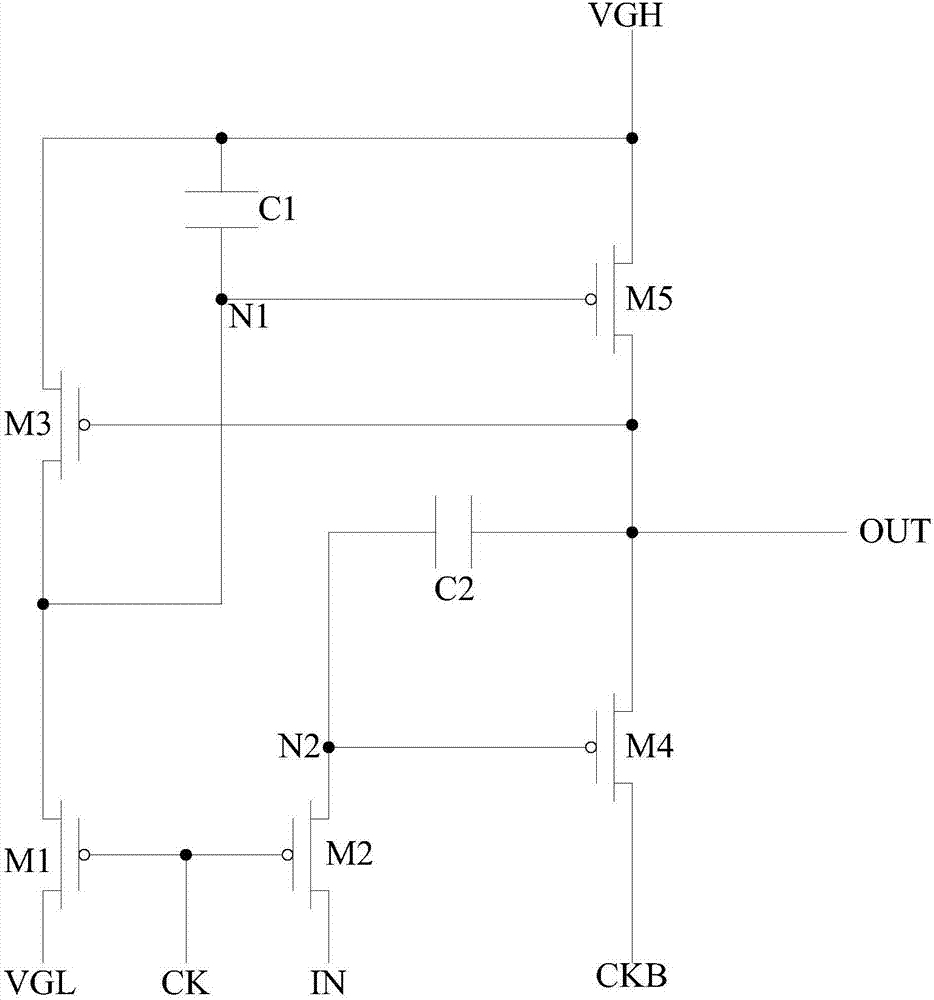

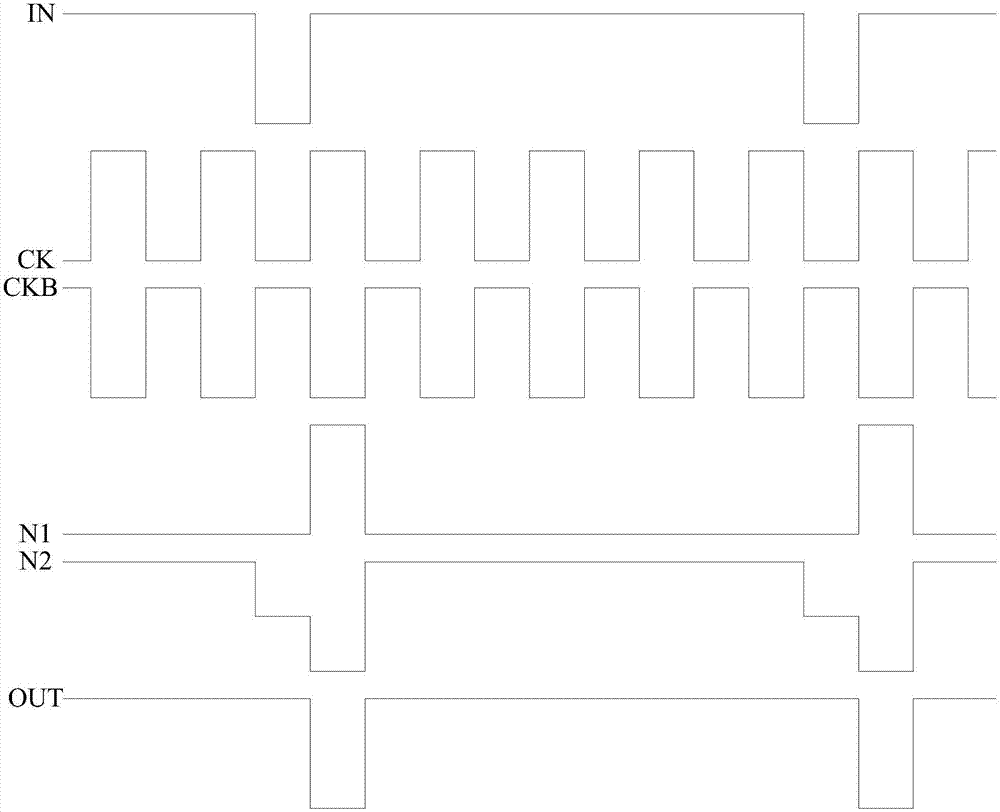

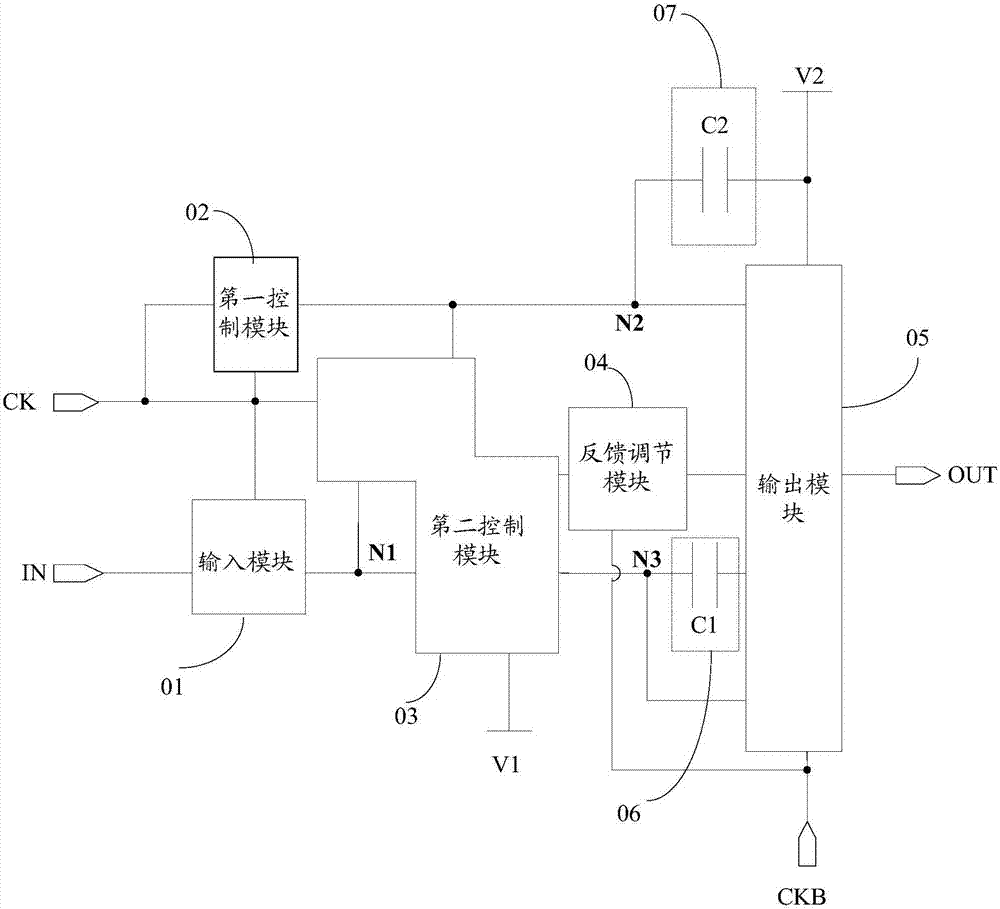

[0087] by Figure 3a and Figure 5a Take the shift register unit shown as an example, all transistors in the shift register unit are P-type transistors, and the corresponding input and output timings are as follows: Figure 7a as shown, Figure 7a An input and output timing diagram corresponding to the shift register unit provided by the embodiment of the present invention; specifically, select as Figure 7a T1, T2, T3, T4 and T5 five stages in the input timing diagram shown.

[0088] In the T1 stage, IN=1, CK=0, and CKB=1.

[0089] Because CK=0, the first transistor T1 and the second transistor T2 are turned on; because CKB=1, the fifth transistor T5 is turned off; because the first signal terminal V1 is at low level, the fourth transistor T4 is turned on. The turned-on first transistor T1 transmits the high-level signal of the input signal terminal IN to the first node N1, so the first node N1 is high-level, and the third transistor T3 is turned off; the high-level signa...

example 2

[0105] by Figure 4a and Figure 6a Take the shift register unit shown as an example, all transistors in the shift register unit are P-type transistors, and the corresponding input and output timings are as follows: Figure 7a as shown, Figure 7a An input and output timing diagram corresponding to the shift register unit provided by the embodiment of the present invention; specifically, select as Figure 7a T1, T2, T3, T4 and T5 five stages in the input timing diagram shown.

[0106] specifically, Figure 4a The shift register unit shown with the Figure 3a Compared with the shift register unit shown, there is an arrangement of the sixth transistor, Figure 6a The shift register unit shown with the Figure 5aCompared with the shown shift register unit, the setting of the sixth transistor is added, so the specific working principle is basically the same.

[0107] In the T1 stage, IN=1, CK=0, and CKB=1.

[0108] Because CK=0, the first transistor T1 and the second trans...

example 3

[0124] by Figure 3b and Figure 5b Take the shift register unit shown as an example, all transistors in the shift register unit are N-type transistors, and the corresponding input and output timing is as follows Figure 7b as shown, Figure 7b An input and output timing diagram corresponding to the shift register unit provided by the embodiment of the present invention; specifically, select as Figure 7b T1, T2, T3, T4 and T5 five stages in the input timing diagram shown.

[0125] In the T1 stage, IN=0, CK=1, and CKB=0.

[0126] Because CK=1, the first transistor T1 and the second transistor T2 are turned on; because CKB=0, the fifth transistor T5 is turned off; because the first signal terminal V1 is at a high level, the fourth transistor T4 is turned on. The turned-on first transistor T1 transmits the low-level signal of the input signal terminal IN to the first node N1, so the first node N1 is low-level, and the third transistor T3 is turned off; the low-level signal o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More