Clock synchronization method and device

A clock synchronization and clock technology, which is applied to synchronization devices, synchronization error correction, time division multiplexing systems, etc. level, the effect of improving clock synchronization performance, and improving test performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

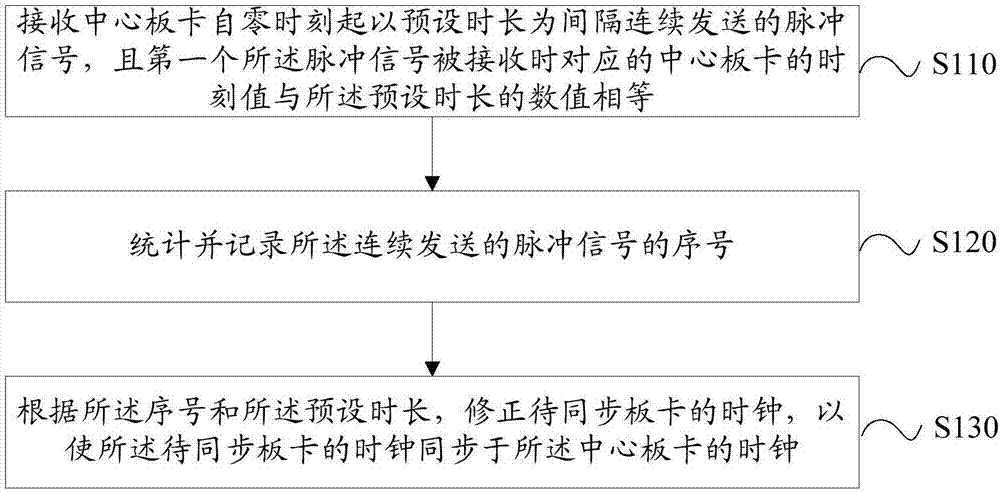

[0043] figure 1 It is a flowchart of a clock synchronization method in the first embodiment of the present invention. This embodiment is applicable to the situation where the internal clock needs to be synchronized and time corrected. The method can be executed by a clock synchronization device, where the device can be Software and / or hardware implementation. reference figure 1 The clock synchronization method provided in this embodiment may specifically include the following steps:

[0044] S110. Receive pulse signals continuously sent by the center board at intervals of a preset duration from time zero, and the time value of the corresponding center board when the first pulse signal is received is equal to the value of the preset duration .

[0045] Specifically, the preset duration is less than 5.2s, and the preset duration is a positive integer. For example, when the preset duration T=5s, the pulse signal sent by the center board is continuously sent at an interval of 5s fr...

Embodiment 2

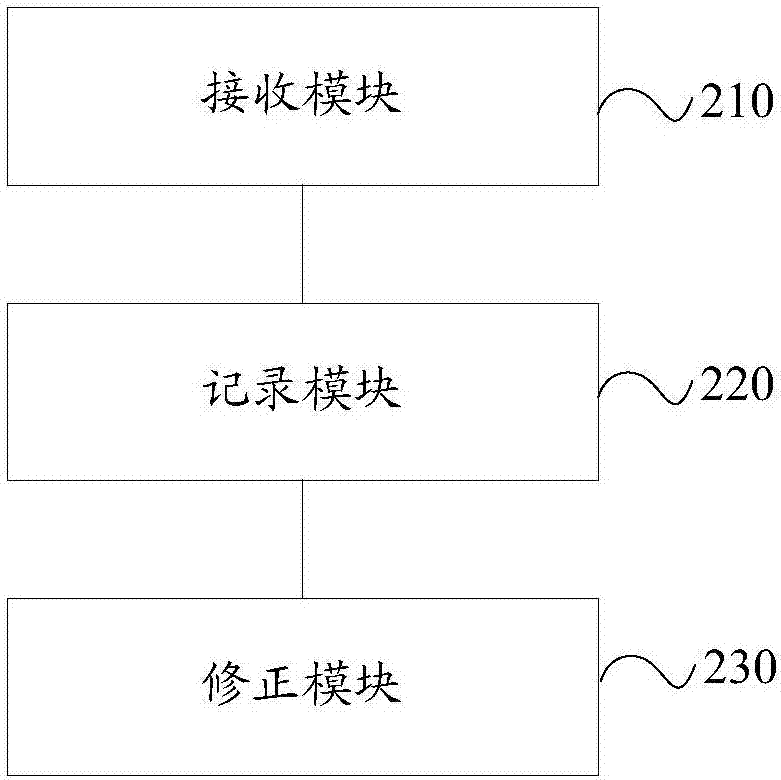

[0058] figure 2 It is a structural diagram of a clock synchronization device in the second embodiment of the present invention. This embodiment can be applied to a situation where the internal clock needs to be synchronized time correction. reference figure 2 The clock synchronization device provided in this embodiment may specifically be as follows:

[0059] The receiving module 210 is configured to receive pulse signals continuously sent by the center board at a preset time interval from time zero, and the time value of the corresponding center board when the first pulse signal is received is the same as the preset time The values of the duration are equal;

[0060] The recording module 220 is used to count and record the serial numbers of the continuously sent pulse signals;

[0061] The correction module 230 is configured to correct the clock of the board to be synchronized according to the serial number and the preset time length, so that the clock of the board to be sync...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com