Continued fraction storage-based integrated circuit test data compression method

A technology for testing data and integrated circuits, applied in the direction of measuring electricity, measuring devices, measuring electrical variables, etc., can solve the problem of increased hardware overhead of counters, achieve the effect of reducing hardware overhead and expanding run length

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] The specific embodiment of the present invention will be further described below in conjunction with accompanying drawing:

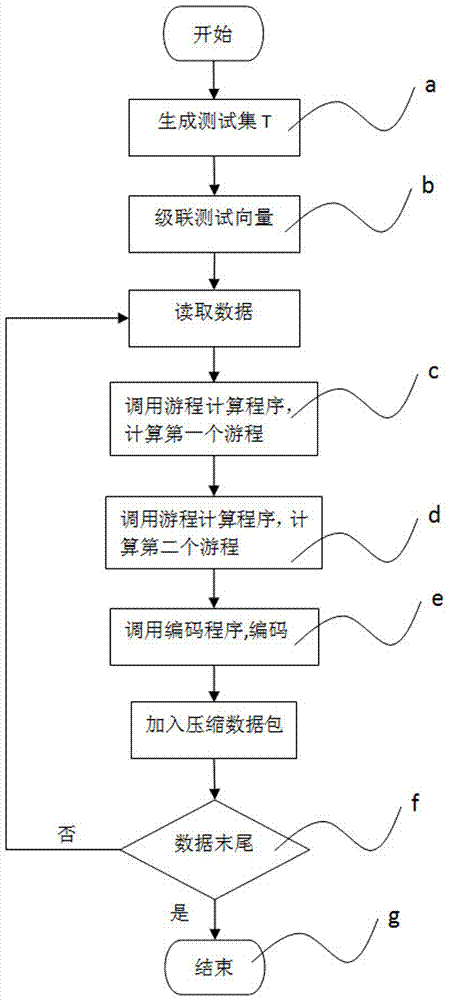

[0041] like figure 1 It can be seen that the integrated circuit test data compression method based on continued fraction storage of the present invention comprises the following steps:

[0042] A, adopt automatic test pattern generation tool ATPG, generate the complete test set T of definite, described complete test set T is made up of the test vector of finite fixed width, record the width of this test vector;

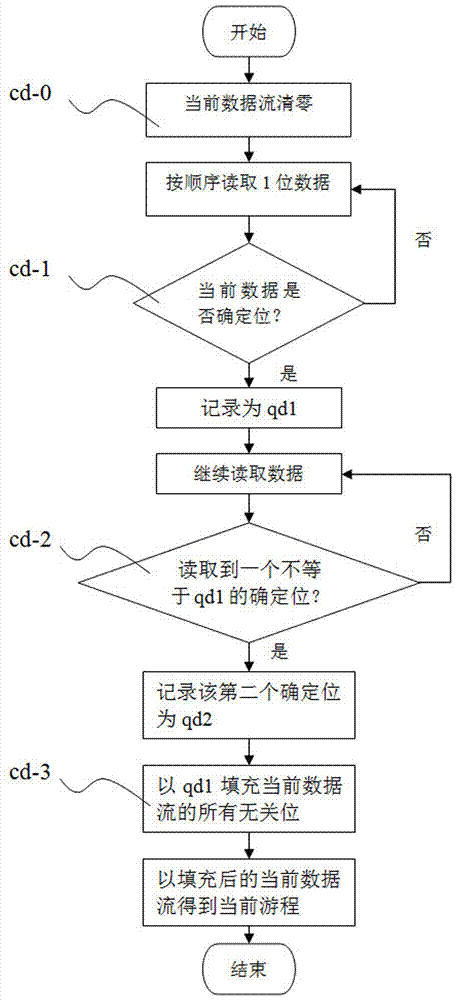

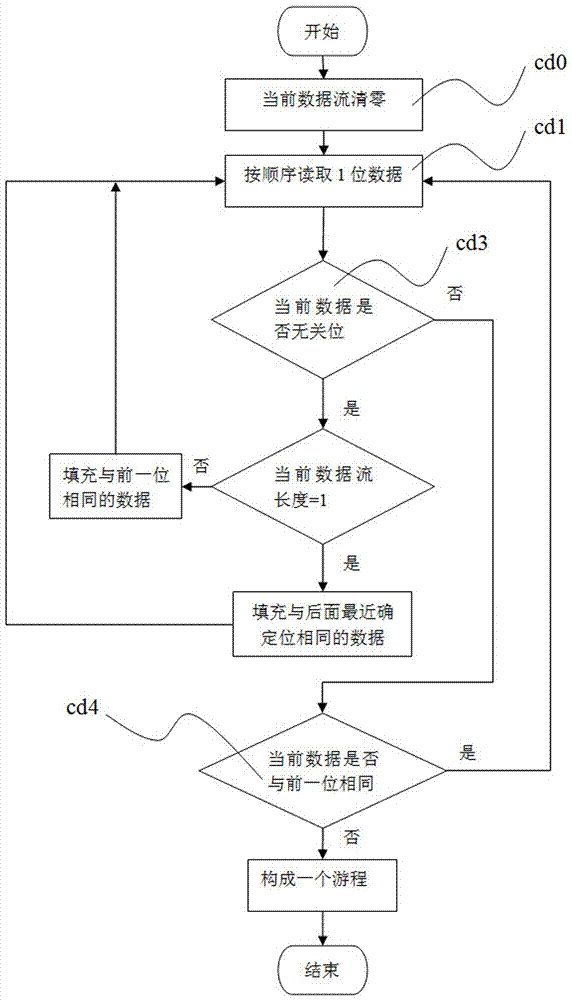

[0043] Common knowledge: A single test vector includes a finite number of definite bits and a finite number of irrelevant bits. The position of the definite bit in the current test vector is not fixed, and the definite bit is embodied as a binary number 0 or 1; the position of the unrelated bit in the current test vector is not fixed. Fixed, after the irrelevant bits are filled with 0 or 1, it has no effect on the test results of the int...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More