CPU for realizing randomization of dynamic instruction sets

A dynamic instruction and randomization technology, applied in the CPU field, can solve the problems of high performance loss and achieve the effect of reducing operating loss and improving the defense effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] The specific embodiments of the present invention will be further described below in conjunction with the accompanying drawings.

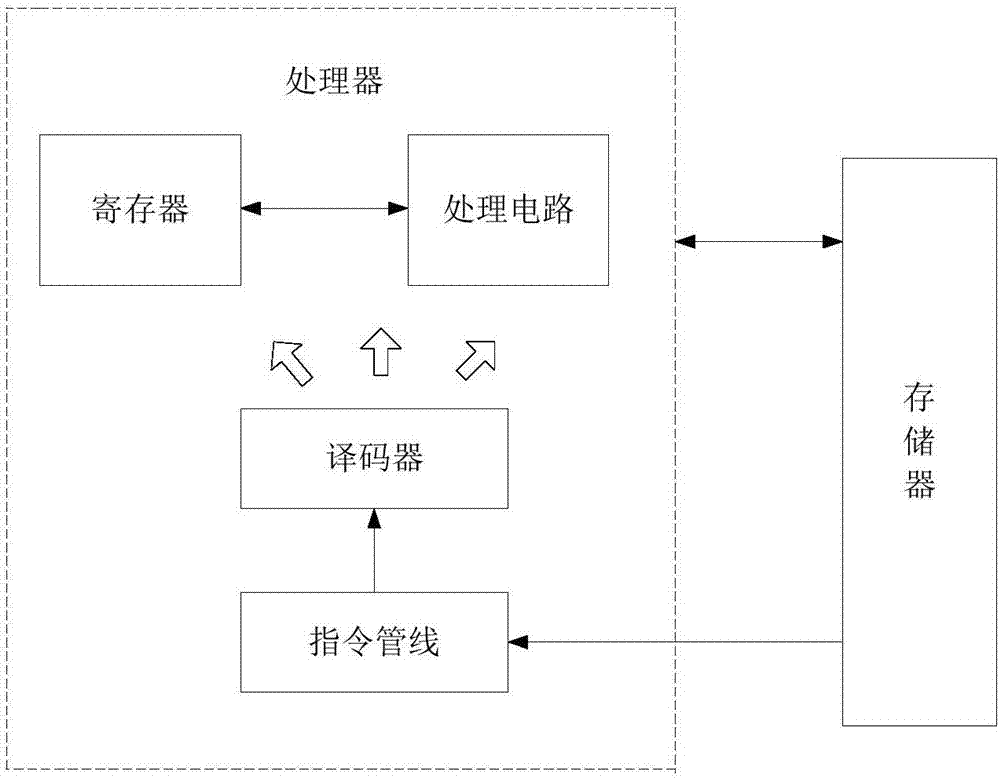

[0026] Current CPU systems such as figure 1 As shown, it includes a processor and a memory. The processor includes registers, processing circuits, data pipelines and decoders. The instruction pipeline reads instructions from the memory and sends the read instructions to the instruction decoder for decoding. The instruction decoder generates control signals in response to the program instructions decoded by the instruction decoder, and the generated control signals control the access of processing circuits and registers.

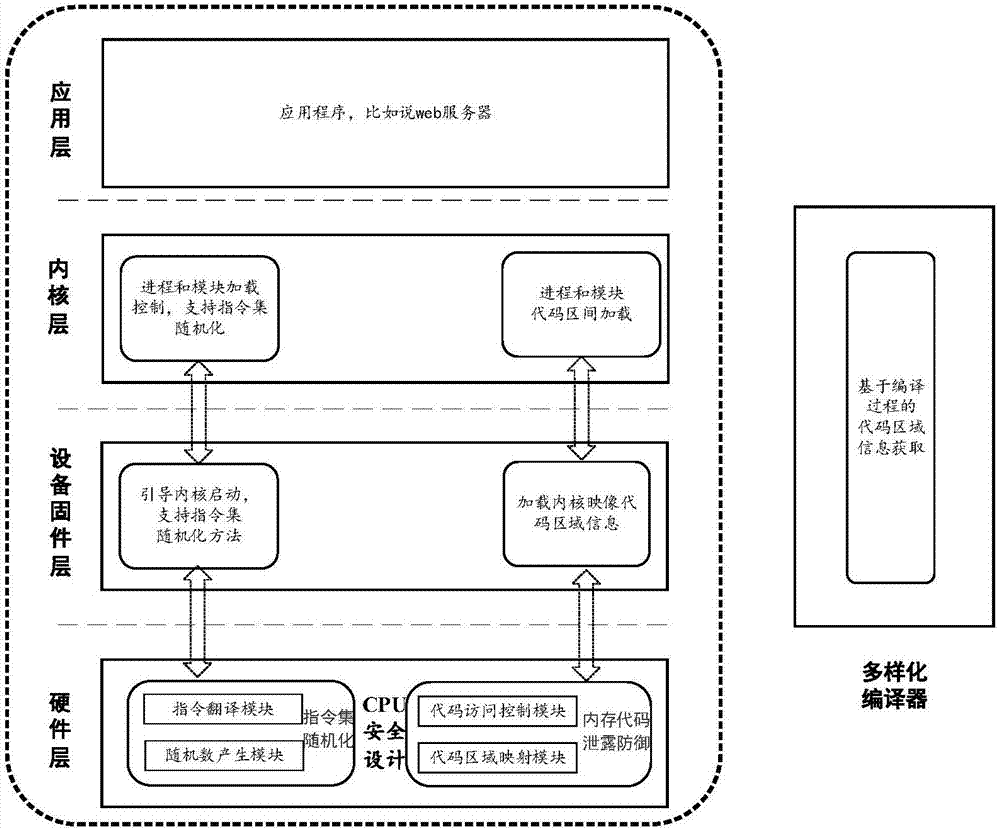

[0027]The present invention is aimed at CPUs based on RISC architecture. This embodiment uses the OpenRISC project as an example for illustration. The instruction randomization CPU of the present invention is also applicable to CPUs with other RISC instruction architectures. The OpenRISC project provides an open-source RIS...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More