A FPGA-based tcp/ip header verification device and method

A header and verification module technology, applied in the field of FPGA-based TCP/IP header verification device, to achieve the effect of ensuring correctness, easy implementation, and solving misjudgment

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

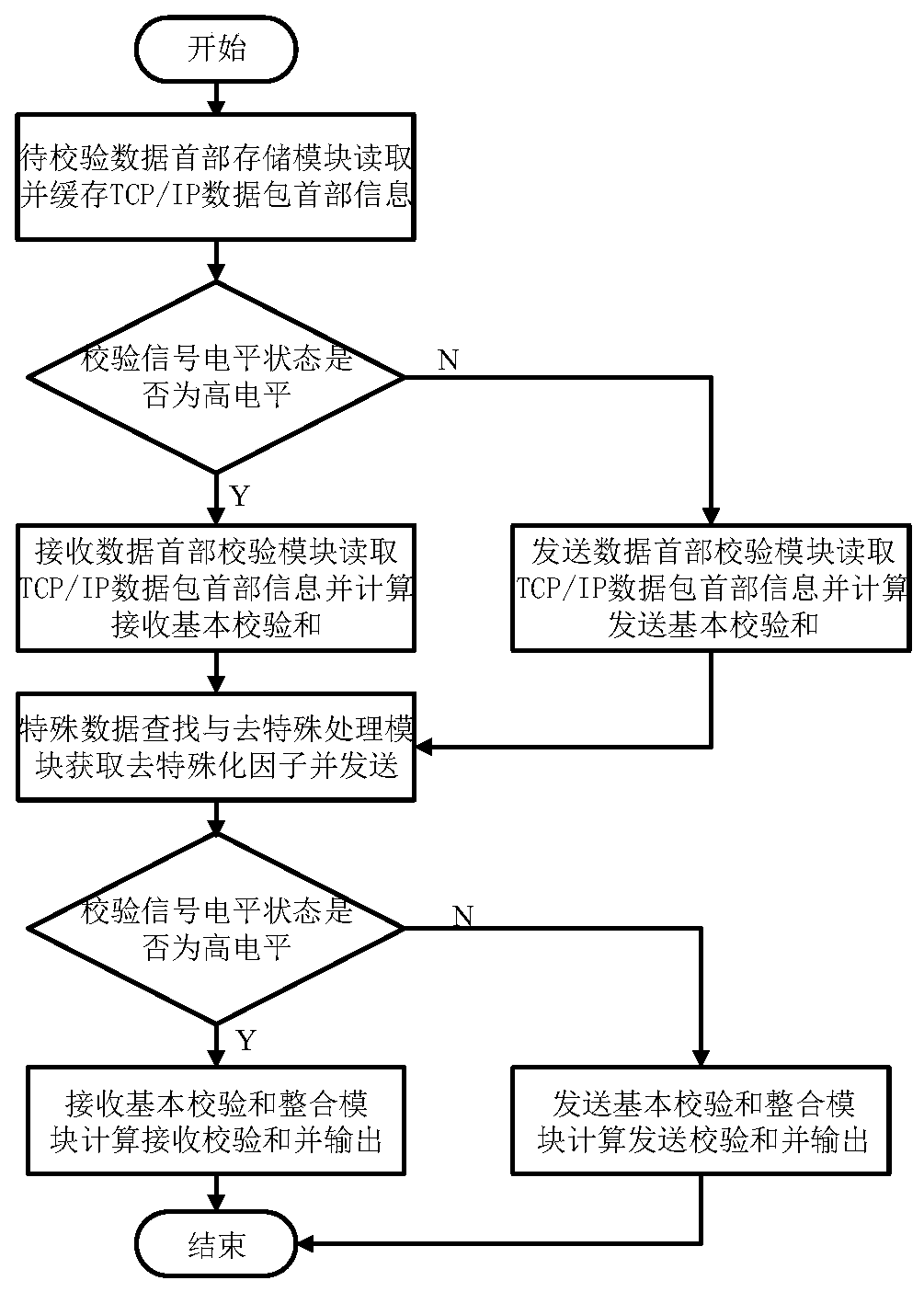

[0046] The present invention will be described in further detail below in conjunction with the accompanying drawings and embodiments.

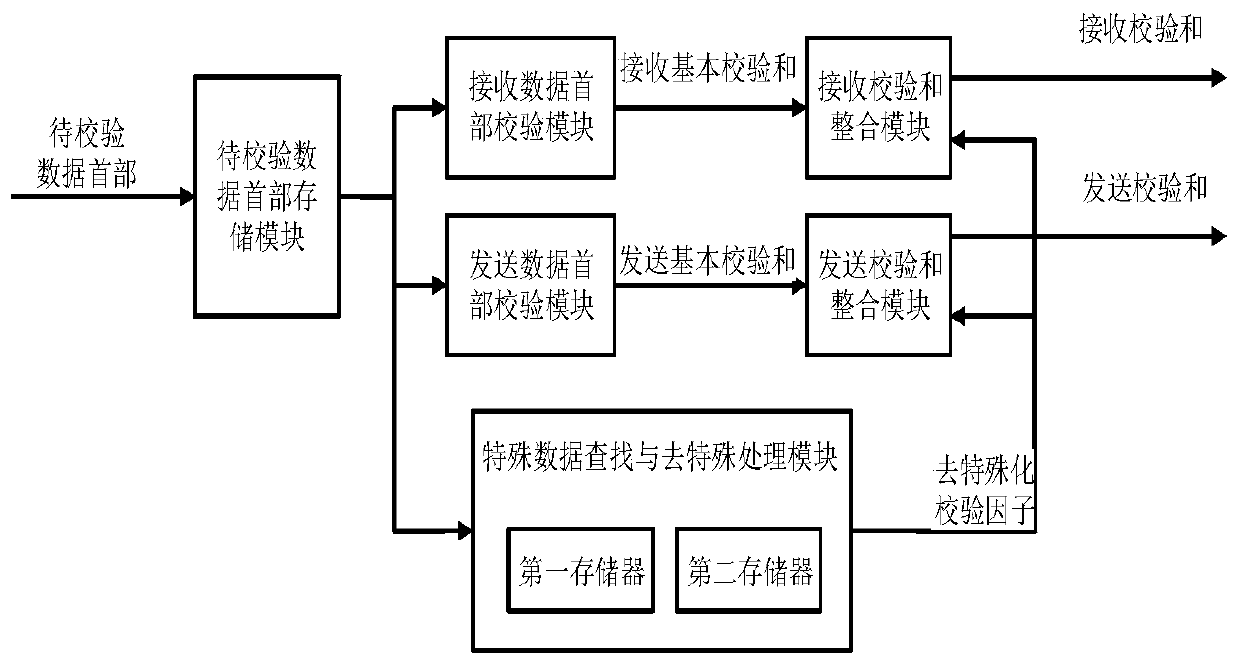

[0047] refer to figure 1 , a FPGA-based TCP / IP header check device, comprising a data header storage module to be checked, a received data header check module, and a sent data header check module implemented in the FPGA, wherein:

[0048] The header storage module of the data to be verified is used to store the header information of the received TCP / IP data packet;

[0049] The received data header verification module is connected with the data header storage module to be verified, and is used for judging the level state of the verification signal, and reads the header information of the TCP / IP data packet when the verification signal is at a high level, and reads the header information of the TCP / IP data packet according to the binary level. The 16-bit double words are added sequentially to obtain the received basic checksum;

[0050] The s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More