Method and system for recovering low-speed data through high-speed serdes interface

A low-speed data and data technology, applied in the field of communication, can solve the problems of small demand for SerDes interface IP, high power consumption, high research and development costs, etc., to reduce design risks and costs, ensure data transmission without errors, shorten Effects of the development cycle

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

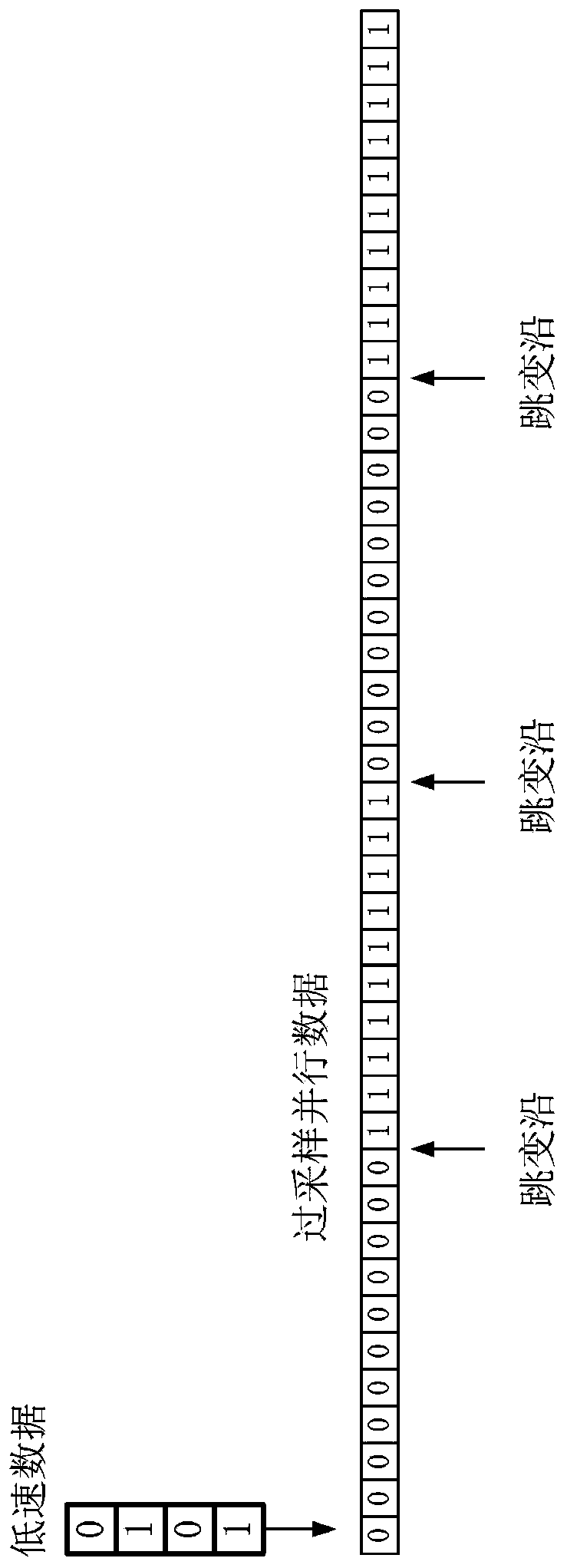

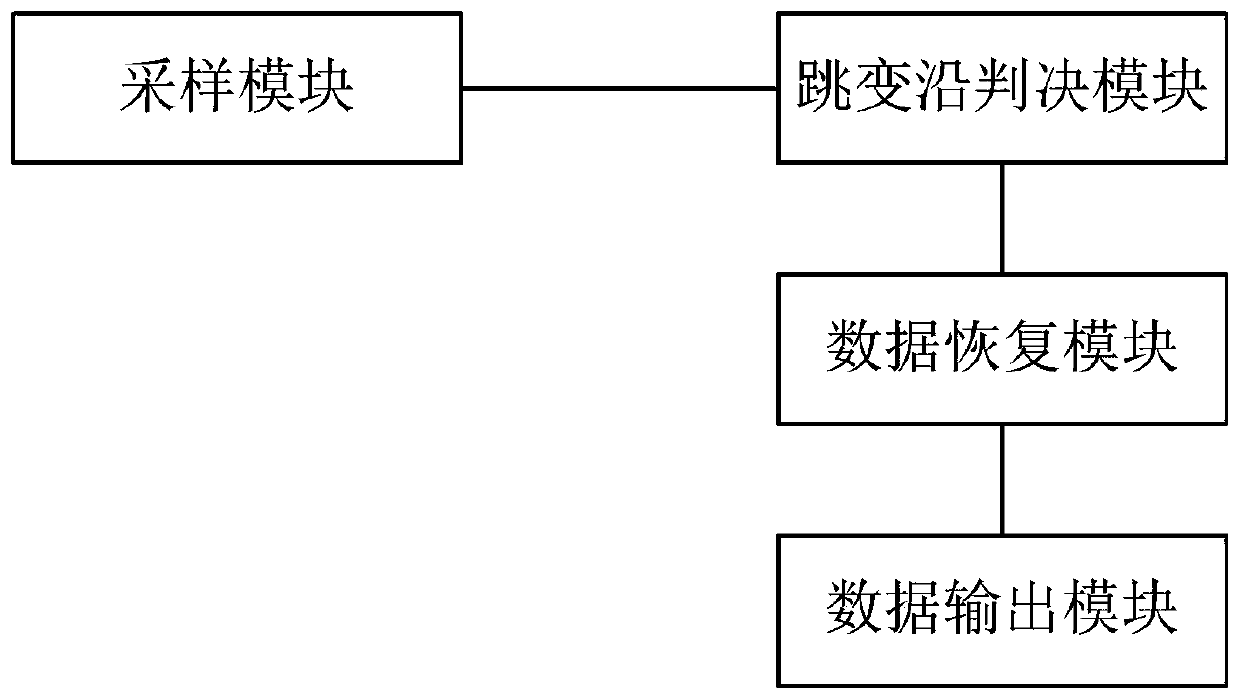

[0035] The principle of the present invention is: use the existing high-speed SerDes interface to oversample the input 100M low-speed data, and after serial-to-parallel conversion, recover the 100M low-speed data into an extended Gigabit rate data stream. The digital logic method is used to judge the signal jump edge of the gigabit rate data stream, and find the best sampling point of the 100M low-speed data in the gigabit rate data stream according to the result of the jump edge judgment. The data signal of the sampling point is used as the restored 100M low-speed data to realize the restoration of the original 100M data from the high-speed SerDes interface.

[0036] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

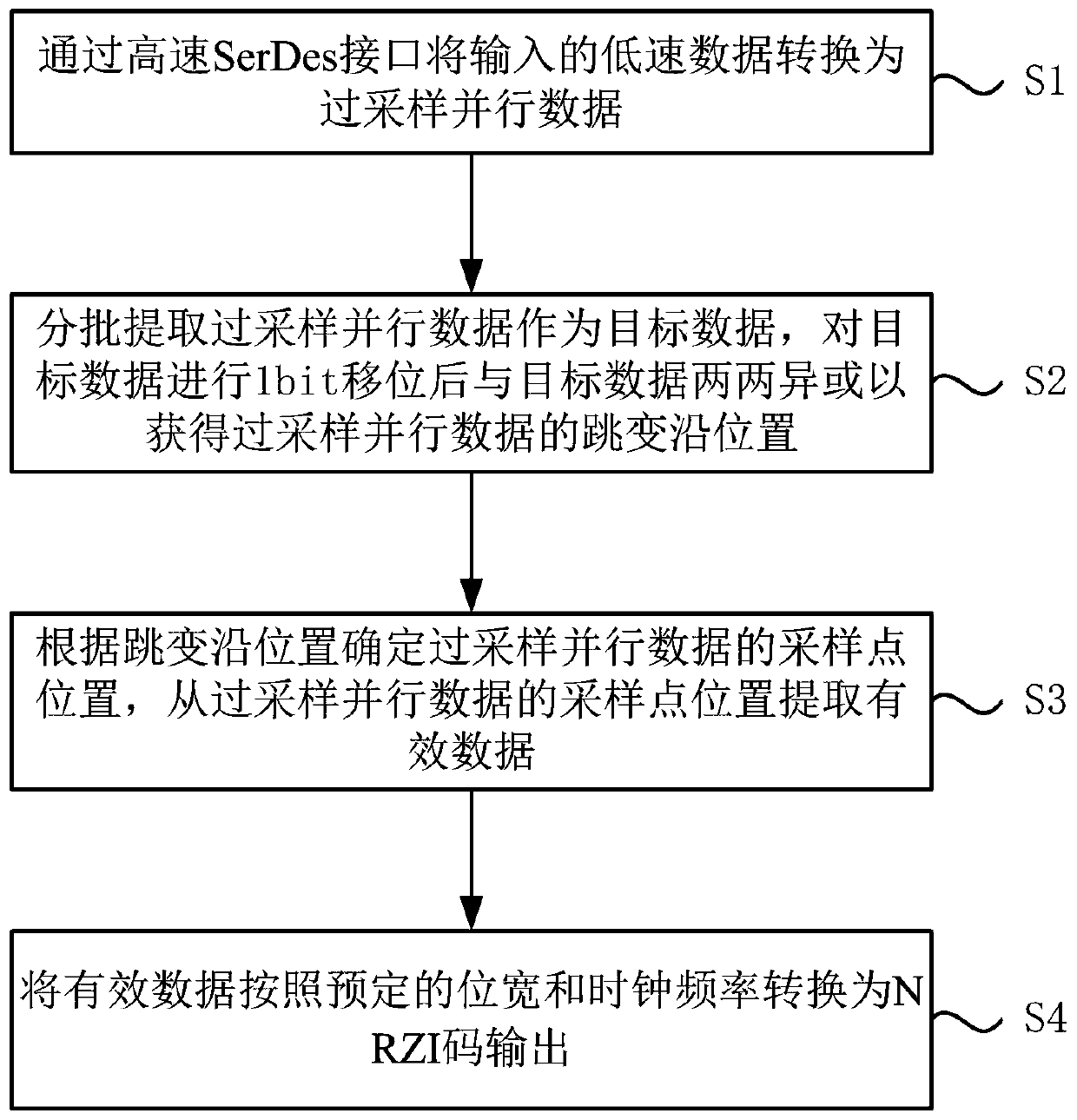

[0037] see figure 1 As shown, the embodiment of the present invention provides a method for recovering low-speed data through a high-speed SerDes interface. The method include...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More