Method for reducing LDPC decoding delay based on error characteristics of flash memory pages

A flash memory page and decoding technology, applied in the direction of response error generation, error detection/correction, redundant code error detection, etc., can solve the problem of large decoding delay gap

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0054] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention. In addition, the technical features involved in the various embodiments of the present invention described below can be combined with each other as long as they do not constitute a conflict with each other.

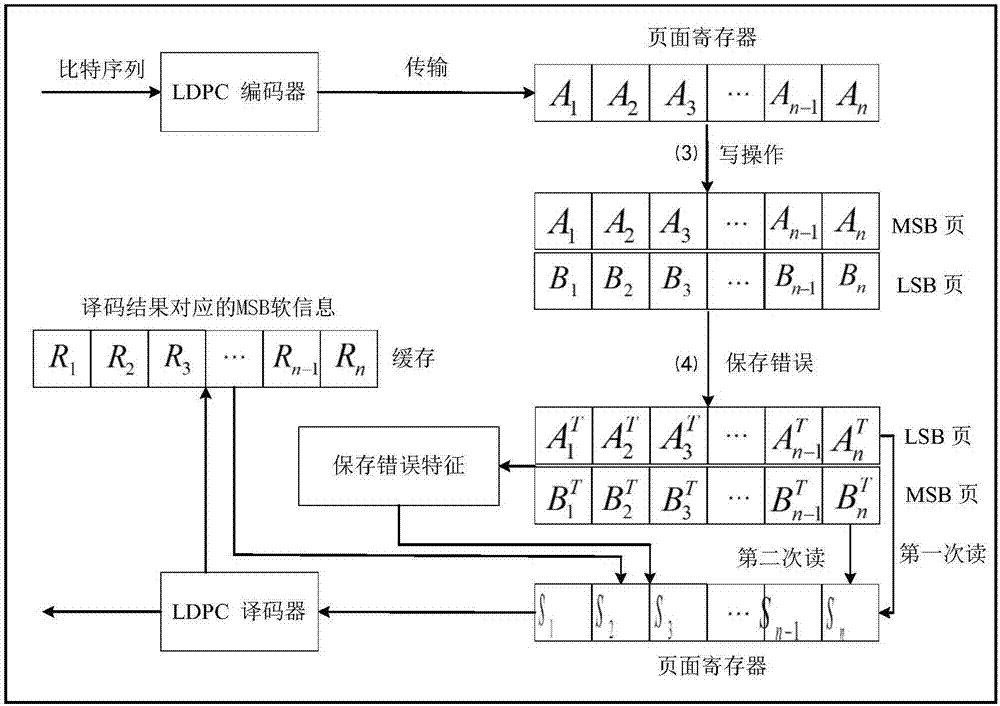

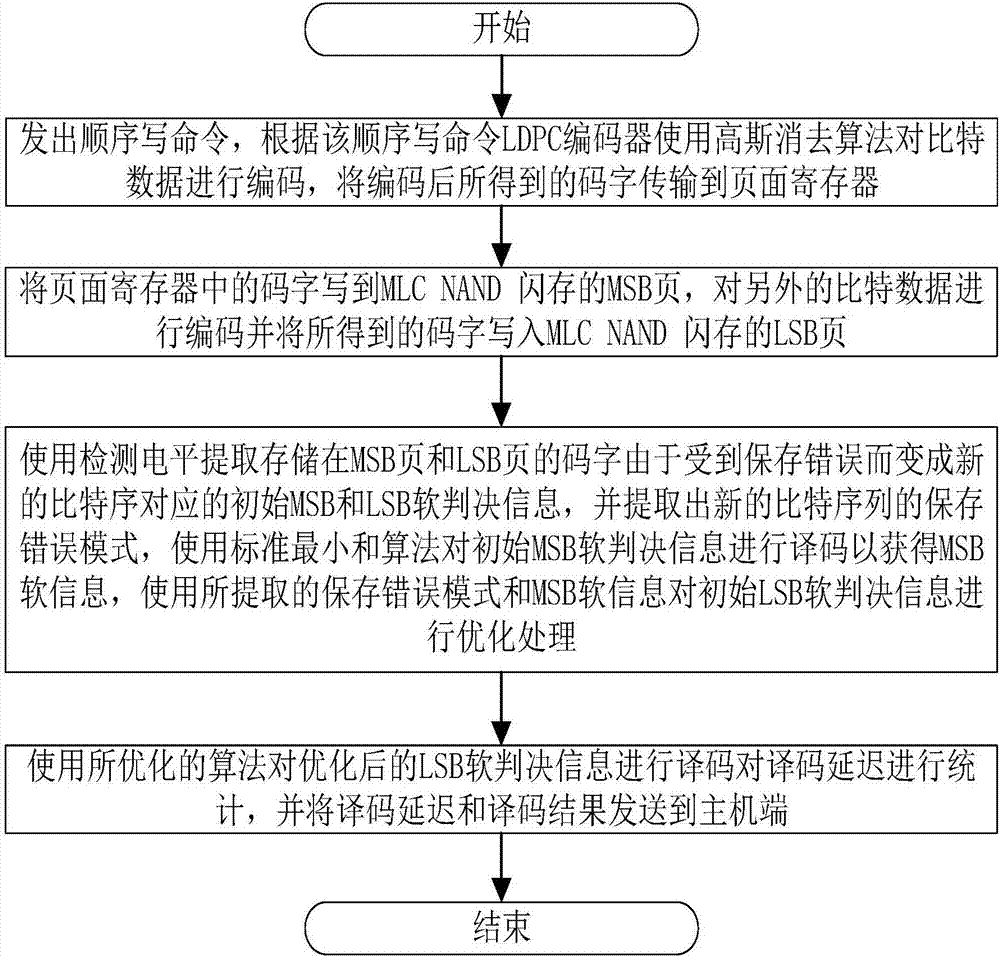

[0055] Design structural drawing of the present invention is as figure 1 As shown, after the bit data is encoded by the LDPC encoder, the obtained codeword is transferred to the page register, first written to the MSB page of the MLC NAND flash memory, and the obtained codeword is written to the LSB page. As the bit data storage time changes, the electrons stored in the MLC NAND flash memory un...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More