CMOS device and fabrication method thereof

A manufacturing method and device technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, transistors, etc., can solve problems such as the inability to realize multi-threshold regulation well, and achieve threshold adjustment with little influence, high control precision, and integrated The effect of simple process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

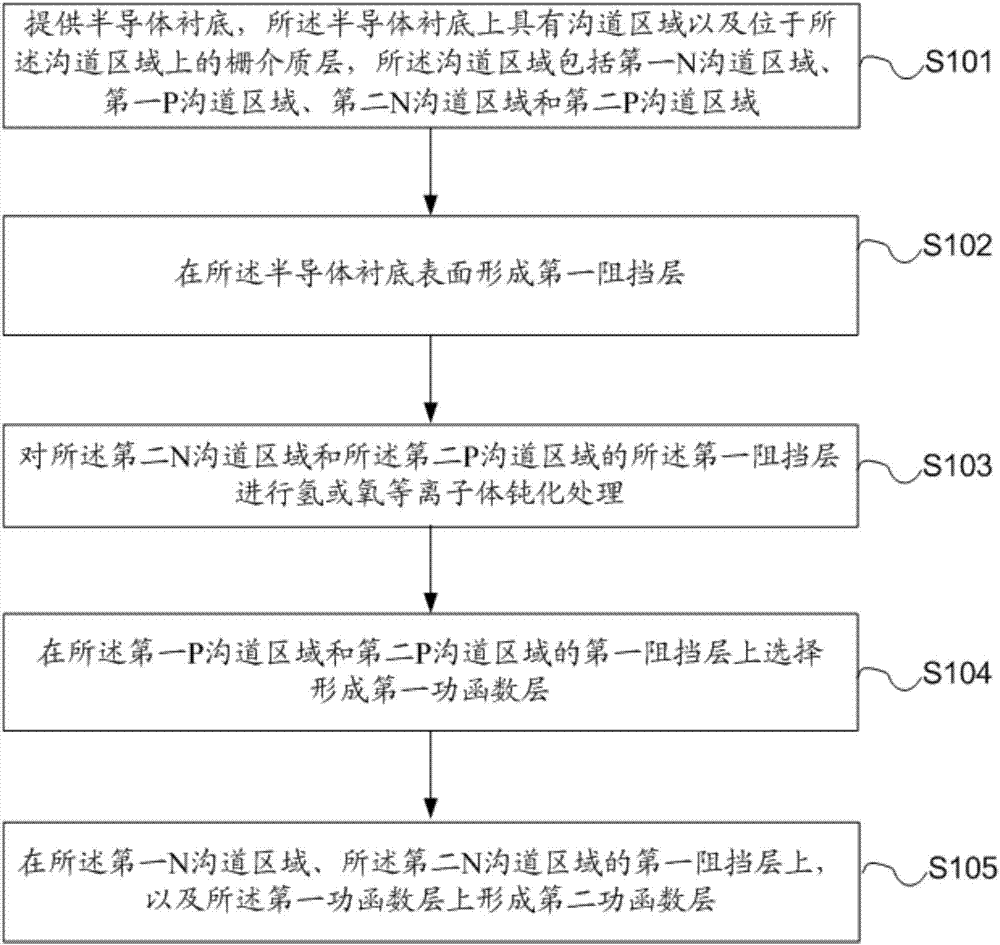

[0029] As mentioned in the background technology section, due to the space limitation and parasitic effects caused by size reduction in the prior art, higher requirements are put forward for the threshold adjustment of CMOS devices, and the traditional threshold adjustment method has not been well realized. Multi-threshold regulation.

[0030] Specifically, the method for adjusting the threshold of a CMOS device in the prior art is: first deposit a barrier layer on the metal gates of the NMOS region and the PMOS region, then adjust the thickness of the barrier layer, then deposit a PMOS work function layer (PMOS WFL), and then change The thickness of the PMOSWFL is used to adjust the PMOS threshold; the NMOS work function layer (NMOS WFL) is then deposited, and the NMOS WFL is combined with the change in the thickness of the previous barrier layer to jointly adjust the NMOS threshold. Since the NMOS threshold adjustment process in the existing method needs to be divided into t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More