Fin field effect transistor and method of forming the same

A fin field effect and transistor technology, which is applied in semiconductor devices, semiconductor/solid state device manufacturing, electrical components, etc., can solve the problems of poor performance of fin field effect transistors, and improve stress, reduce collapse, and performance Improved effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] As mentioned in the background, the performance of FinFETs formed in the prior art is poor.

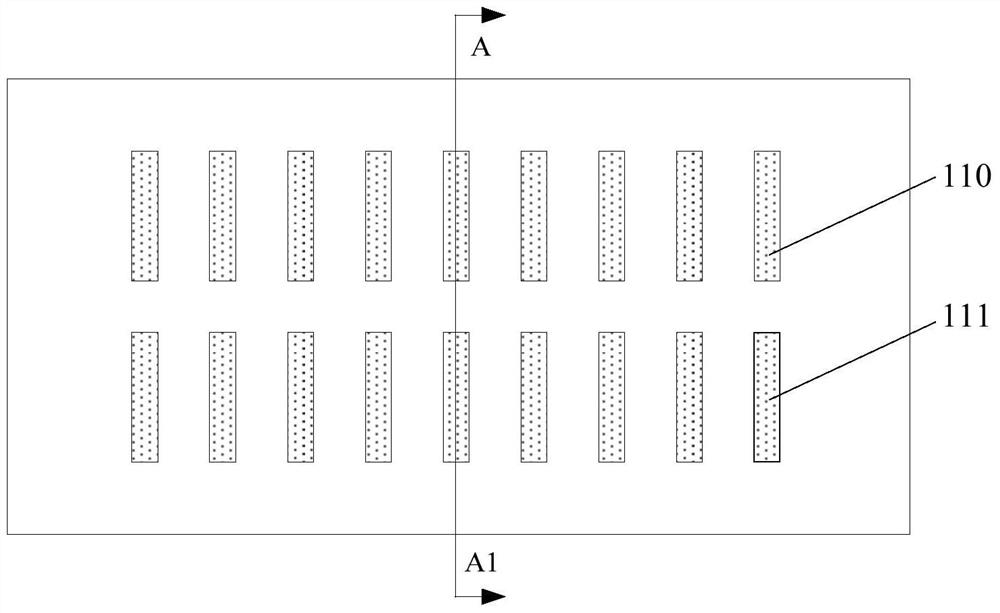

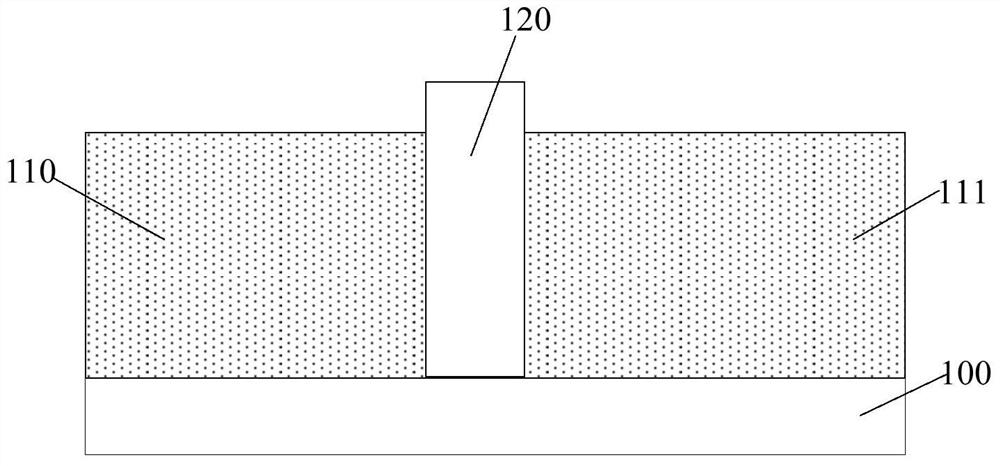

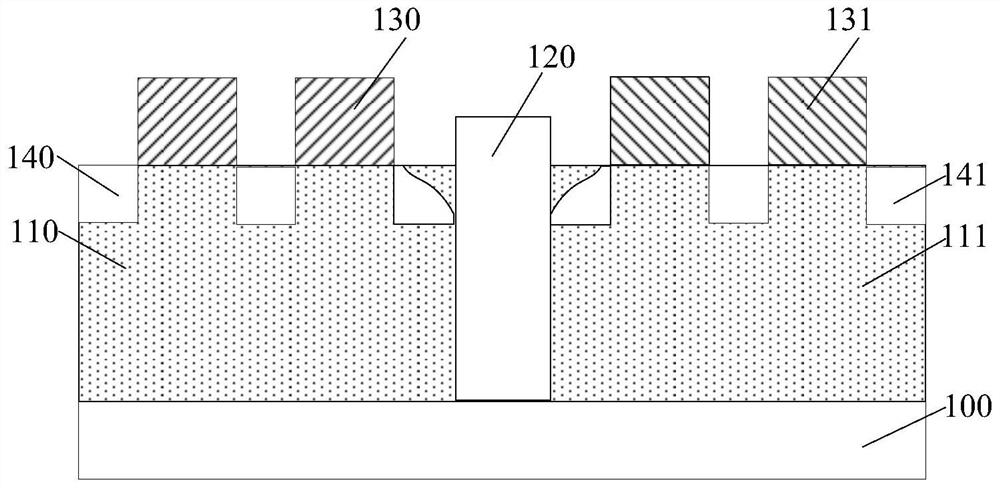

[0030] Figure 1 to Figure 3 It is a structural schematic diagram of the formation process of a fin field effect transistor.

[0031] combined reference figure 1 and figure 2 , figure 2 for along figure 1 The schematic diagram obtained by cutting line A-A1 in the middle provides a semiconductor substrate 100 with initial fins on the semiconductor substrate 100; the initial fins are cut along the normal direction of the surface of the semiconductor substrate 100, and the initial fins are divided into first fins 110 and second fins 111; an isolation structure and an isolation layer 120 are formed on the semiconductor substrate 100, the isolation structure is located between adjacent first fins 110 and between adjacent second fins 111, and isolating The top surface of the structure is lower than the top surfaces of the first fin portion 110 and the second fin portion 111, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More