Chip packaging structure and packaging method

A chip packaging structure and chip packaging technology, applied in the manufacturing of electrical components, electrical solid-state devices, semiconductor/solid-state devices, etc. Enhanced sealing performance and guaranteed miniaturization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0045] This embodiment provides a chip packaging method, comprising the following steps:

[0046] Step S1 , disposing a plurality of first chips 3 on the carrier 1 . Wherein, the first chip 3 is not limited to one kind of chip, and may be various or not all the same kind of chips.

[0047] As an implementation manner of this embodiment, step S1 specifically includes the following steps:

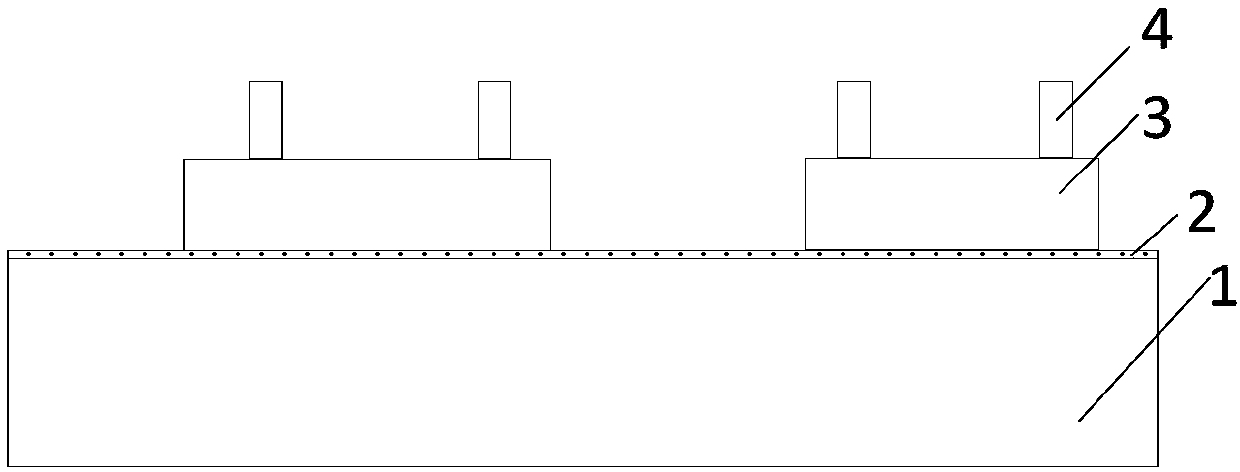

[0048] Step S11, providing a carrier 1, which is generally a silicon slide;

[0049] Step S12, forming an adhesive layer 2 on the carrier 1, specifically, spin-coating a photosensitive temporary bonding glue, such as UV glue, etc. on the carrier 1 by spin coating;

[0050] Step S13 , affixing each first chip 3 on the adhesive layer 2 on the carrier 1 through a patching process, and the first chips 3 are arranged in a matrix.

[0051] Step S2, setting a plurality of first connecting posts 4 on the electrodes of the first chip 3, the first connecting posts 4 are arranged on the side of the f...

Embodiment 2

[0074] This embodiment provides a chip packaging structure, including a first package body 5 and a second package body 11 .

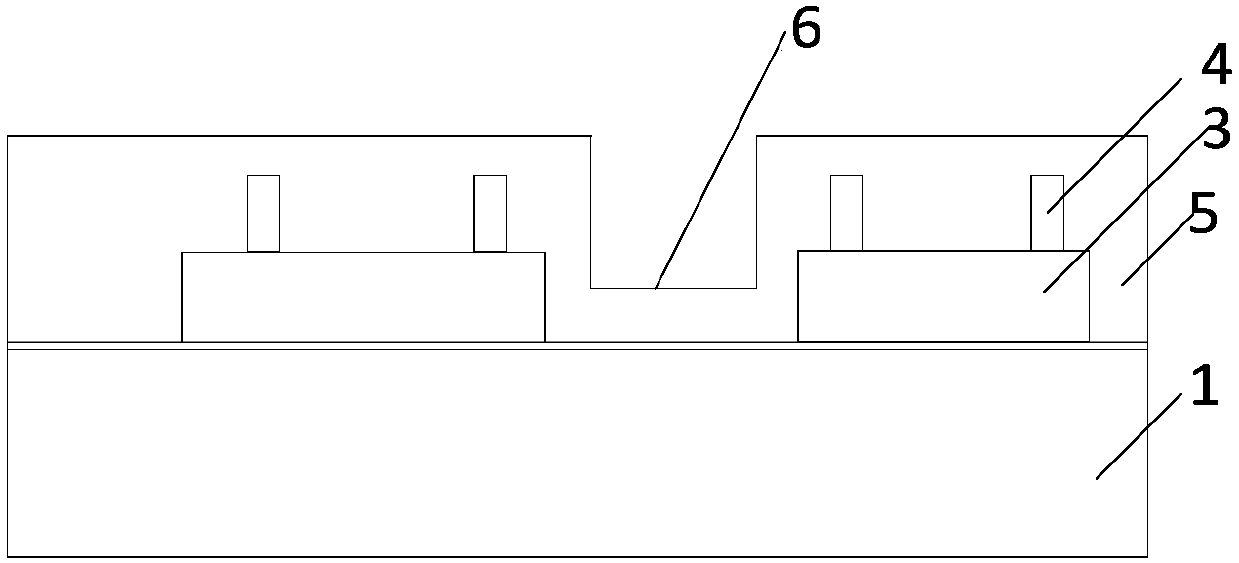

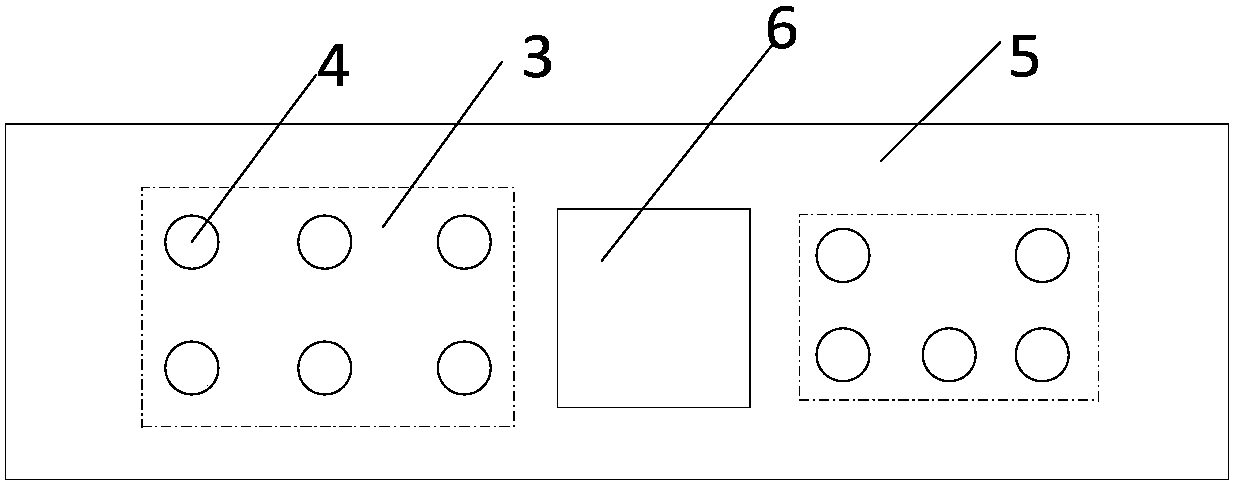

[0075] A plurality of first chips 3 are disposed in the first package 5 , and a groove 6 is provided on the first package 5 between adjacent first chips 3 . Wherein, the first chips 3 are arranged in a matrix, and the first chips 3 are not limited to one kind of chips, but can be various or not all of the same kind of chips, and the groove body 6 is not connected to the adjacent first chips 3 .

[0076] The second package body 11 is directly disposed on the first package body 5 and has a plurality of second chips 8 inside. The second chips 8 are disposed above the slot body 6 and electrically connected to the first chip 3 .

[0077] As an implementation of this embodiment, a wiring layer 7 is also provided on the first package body 5, and a plurality of first connecting posts 4 are provided on the first chip 3, and the wiring layer 7 is connected to the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com