A Comparator Applied to High Speed Pipeline ADC

A pipeline and comparator technology, applied in the direction of analog-to-digital converters, etc., can solve the problem of loud kickback noise, and achieve the effect of reducing kickback noise and eliminating kickback noise

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0012] The technical solution of the present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments, and the described specific embodiments are only for explaining the present invention, and are not intended to limit the present invention.

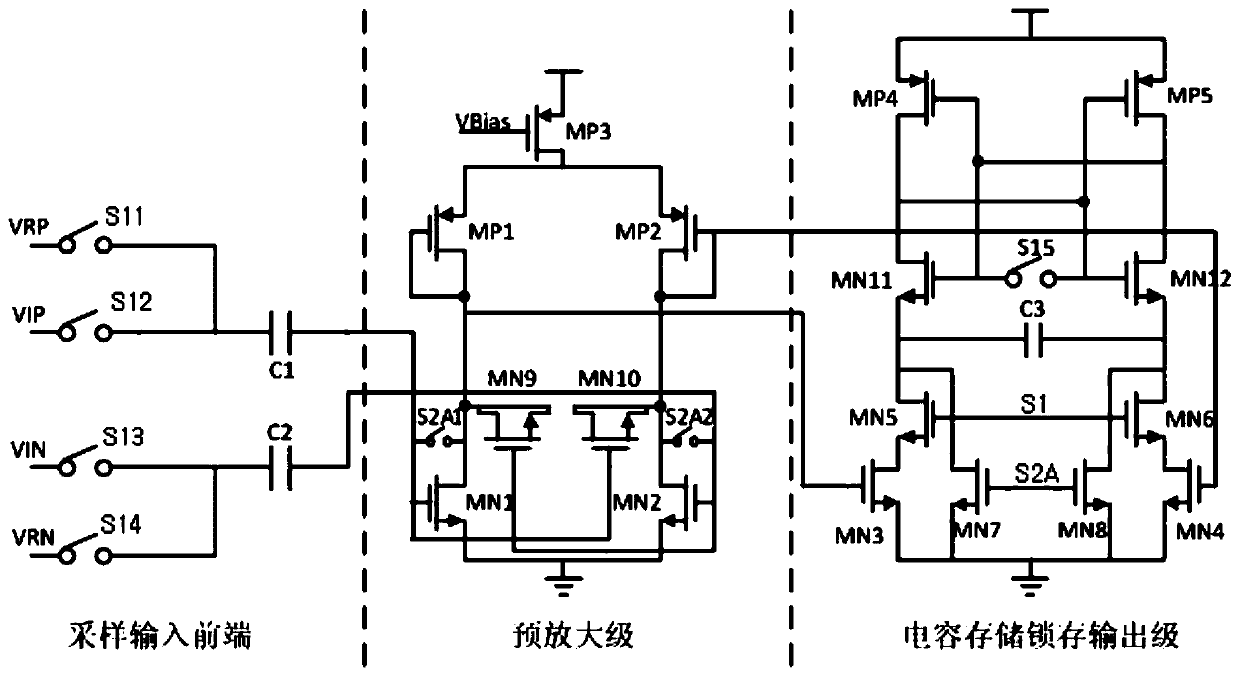

[0013] A kind of comparator applied to high-speed pipeline ADC provided by the present invention, its circuit structure is as follows figure 1 As shown, the comparator includes a switched capacitor sampling front-end circuit, a pre-amplification stage circuit and a capacitor storage latch output stage circuit.

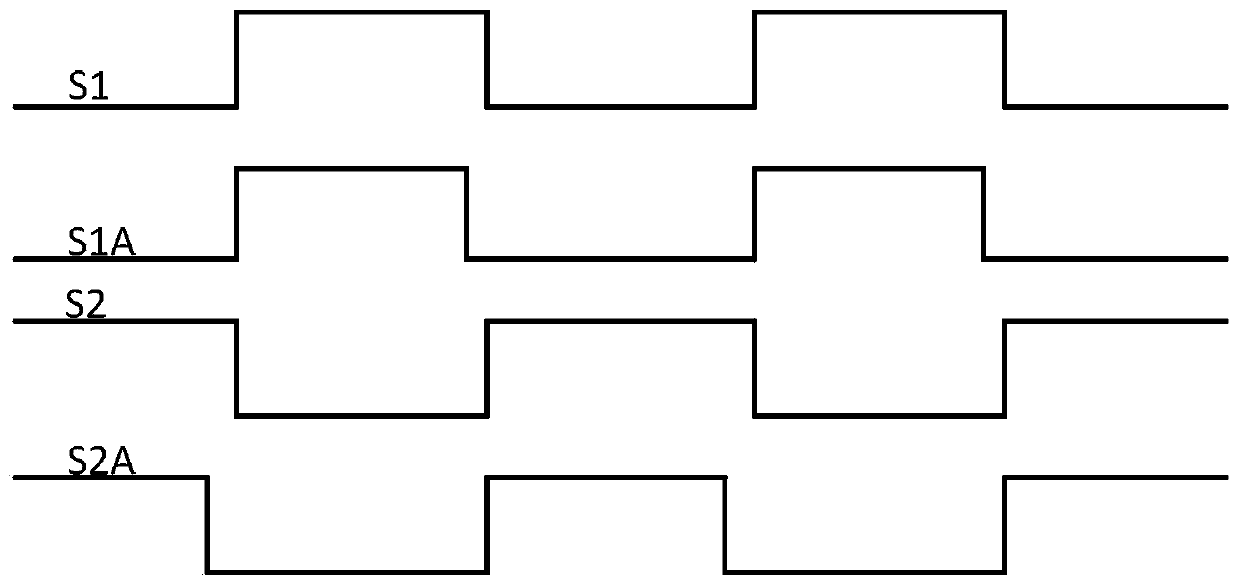

[0014] Such as figure 2 As shown, in the present invention, timing S1 and S2 are two non-overlapping clock signals output by two-phase non-overlapping clock generation circuits, and timing S1A and S2A are high-level signals output by two-phase non-overlapping clock generation circuits. A clock signal with a slightly shorter duration than sequences S1 and S2.

[...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More