Extensible reconfigurable multi-core processor connection method

A multi-core processor and connection method technology, which is applied to the architecture with a single central processor, electrical digital data processing, instruments, etc. Great flexibility and the effect of improving the utilization area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] In order to facilitate those skilled in the art to better understand the present invention, the present invention will be described in further detail below in conjunction with the accompanying drawings and specific embodiments. The following is only exemplary and does not limit the protection scope of the present invention.

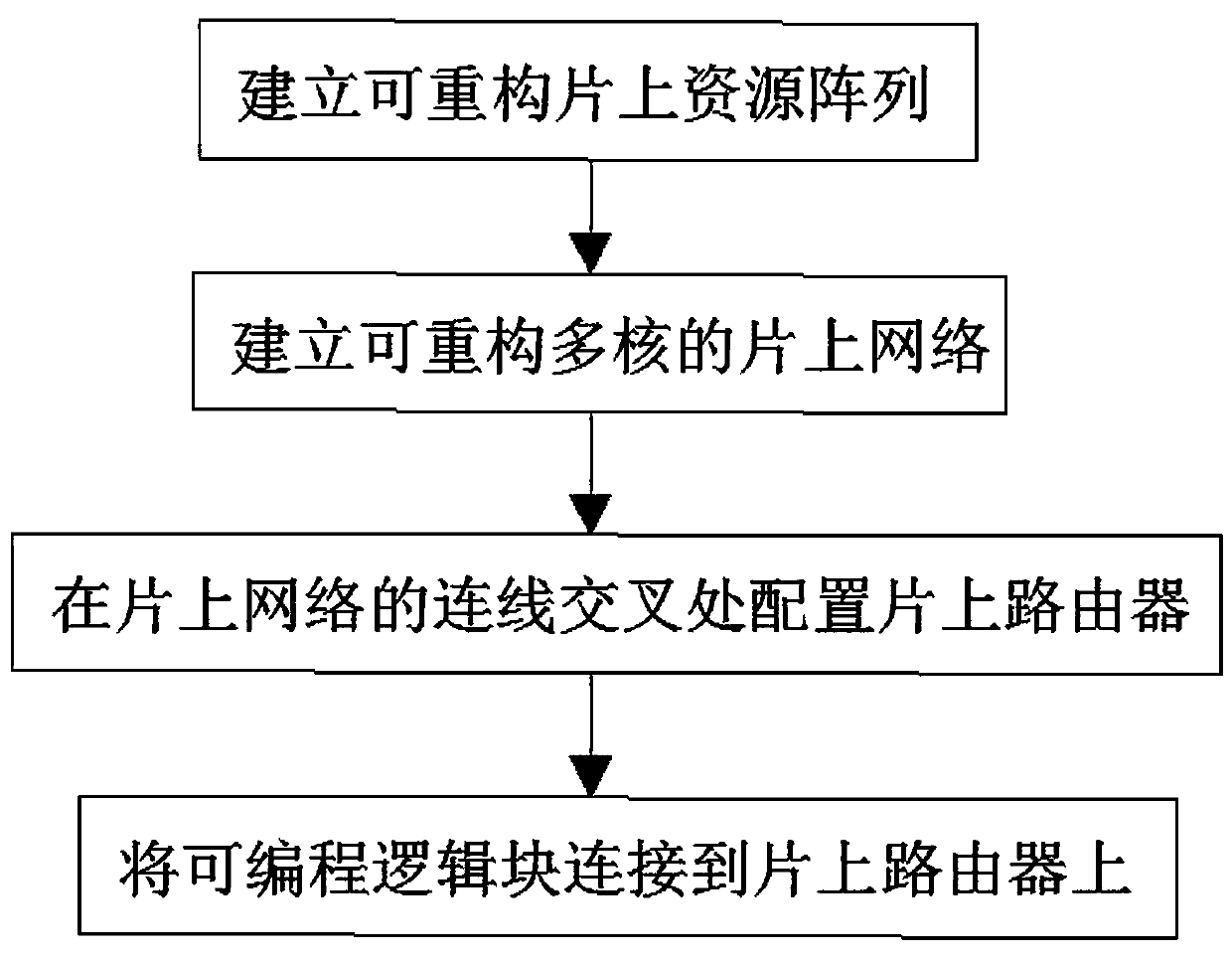

[0028] Such as figure 1 As shown, a scalable reconfigurable multi-core processor connection method described in the present invention includes the following steps:

[0029] S1. Establish a reconfigurable on-chip resource array

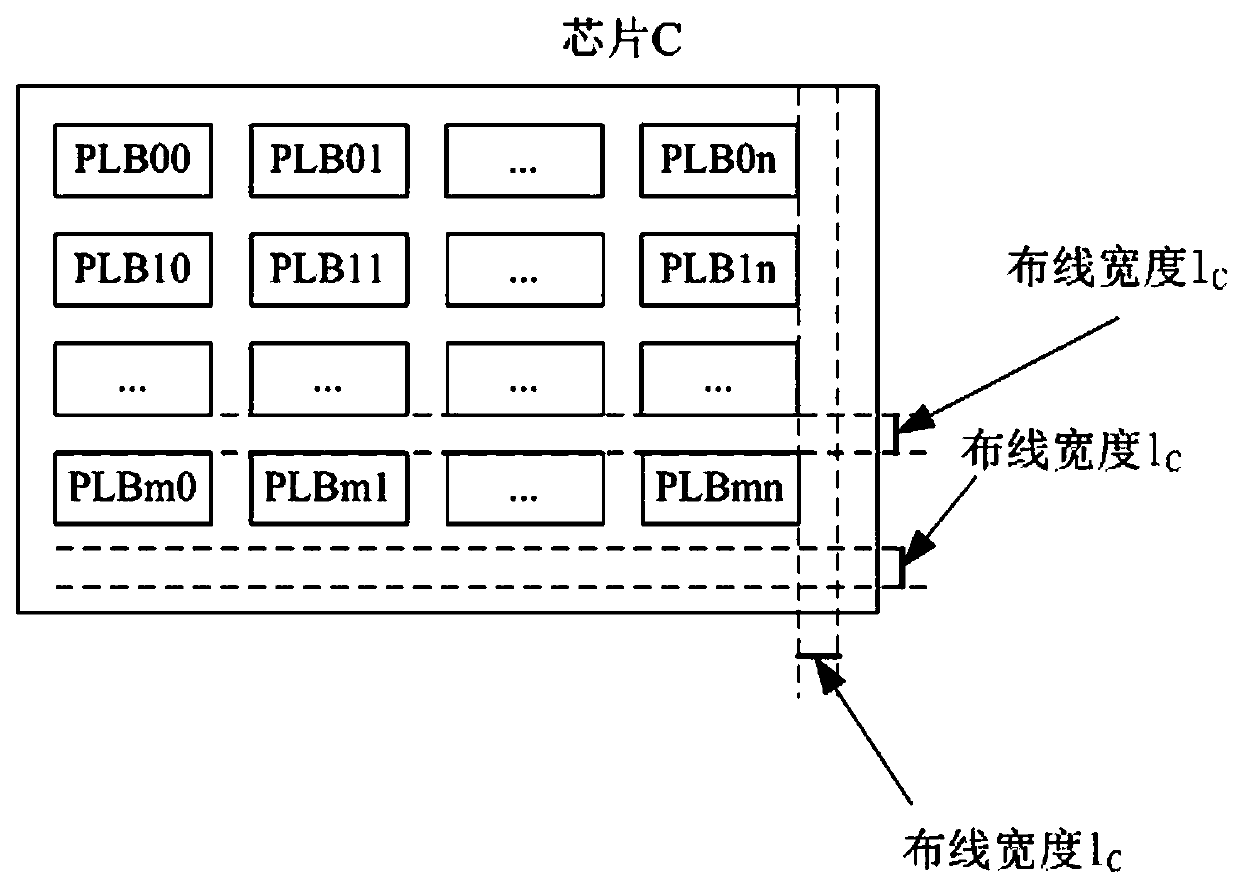

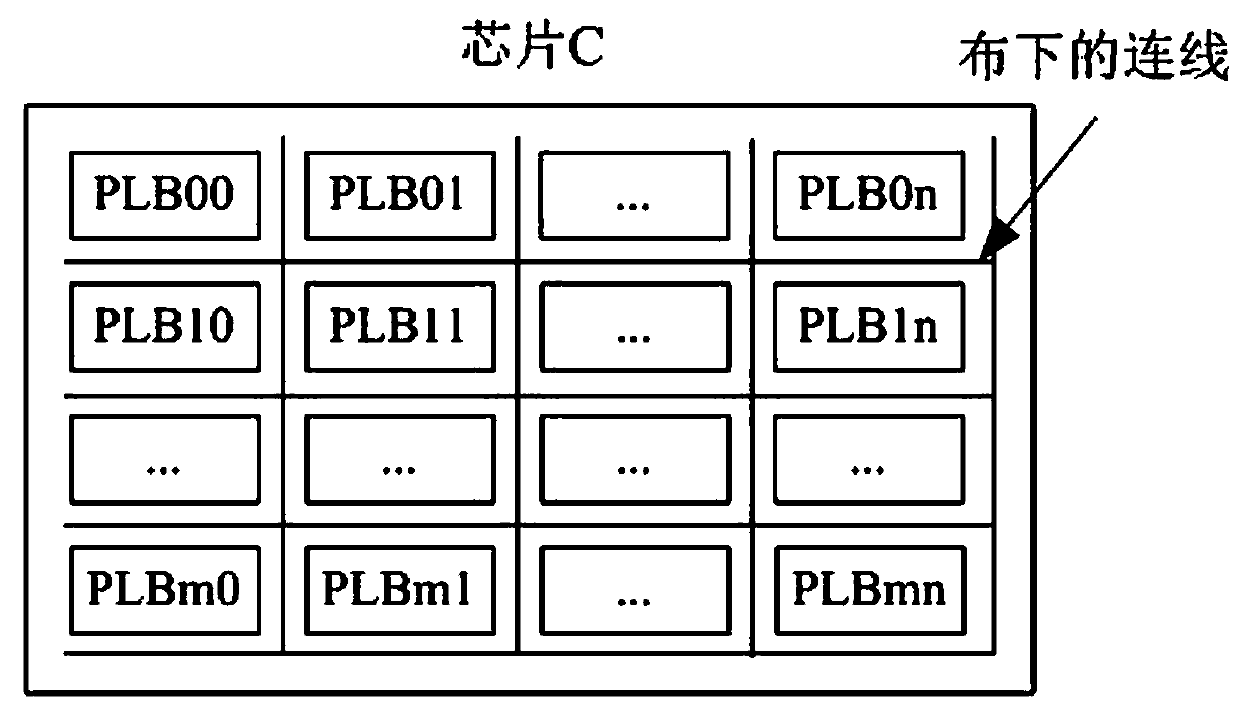

[0030] For a chip with reconfigurable resources, let the chip be chip C, and each basic reconfigurable unit is called a programmable logic block (Programmable Logic Block, PLB), and all programmable logic blocks are arranged in rows and columns on the chip On C, it is assumed that there are (m+1) rows and (n+1) columns of programmable logic blocks on chip C. A wiring space is reserved between adjacent programmable logic b...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More