Chip batch production testing system

A test system and chip technology, applied in automated test systems, electronic circuit tests, etc., can solve problems such as inconvenient analysis, increased chip test costs, lack of data log information, etc., to achieve convenient online debugging and save chip mass production test costs , The effect of shortening the development time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

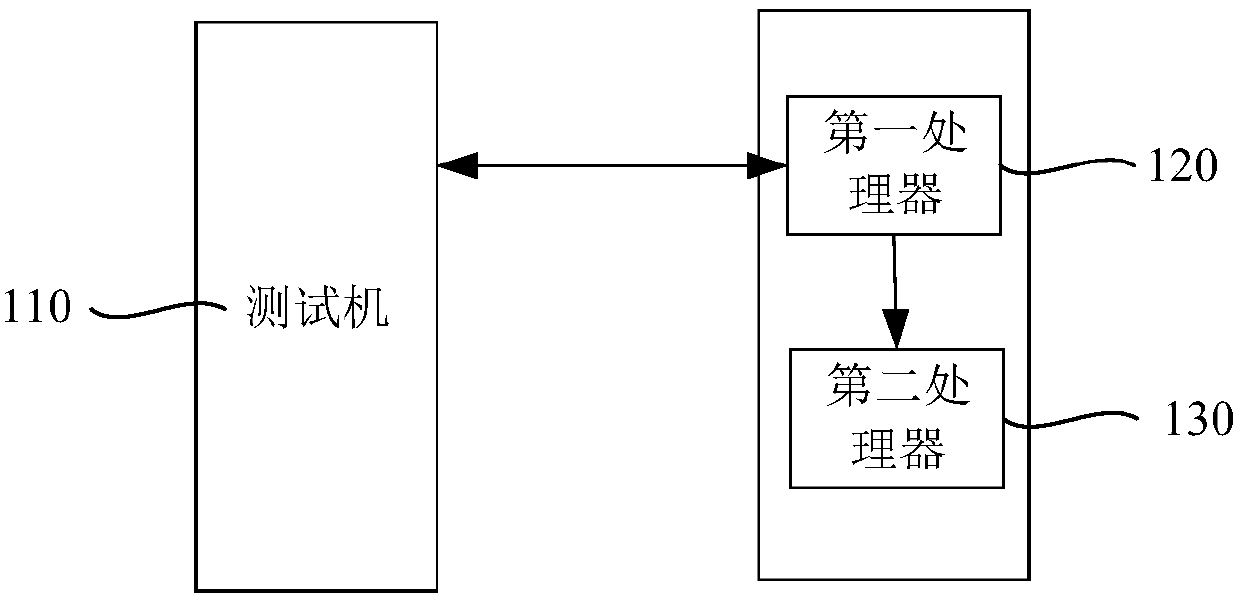

[0033] See figure 1 , figure 1 It is a schematic diagram of a chip mass production testing system provided by an embodiment of the present invention. Specifically, the testing system may include: a testing machine 110; a first processor 120, electrically connected to the testing machine 110, configured to receive control instructions of the testing machine 110, configure the chip to be tested according to the control instructions and The configuration result is sent to the testing machine 110; the second processor 130 is electrically connected to the first processor 120 for configuring and testing the chip under test according to the test vector file sent by the first processor 120 ;

[0034] Wherein, the testing machine 110 is used to complete the test of the first test vector of the chip under test, and the test machine 110 cooperates with the first processor 120 to complete the second test vector of the chip under test The first processor 120 cooperates with the second p...

Embodiment 2

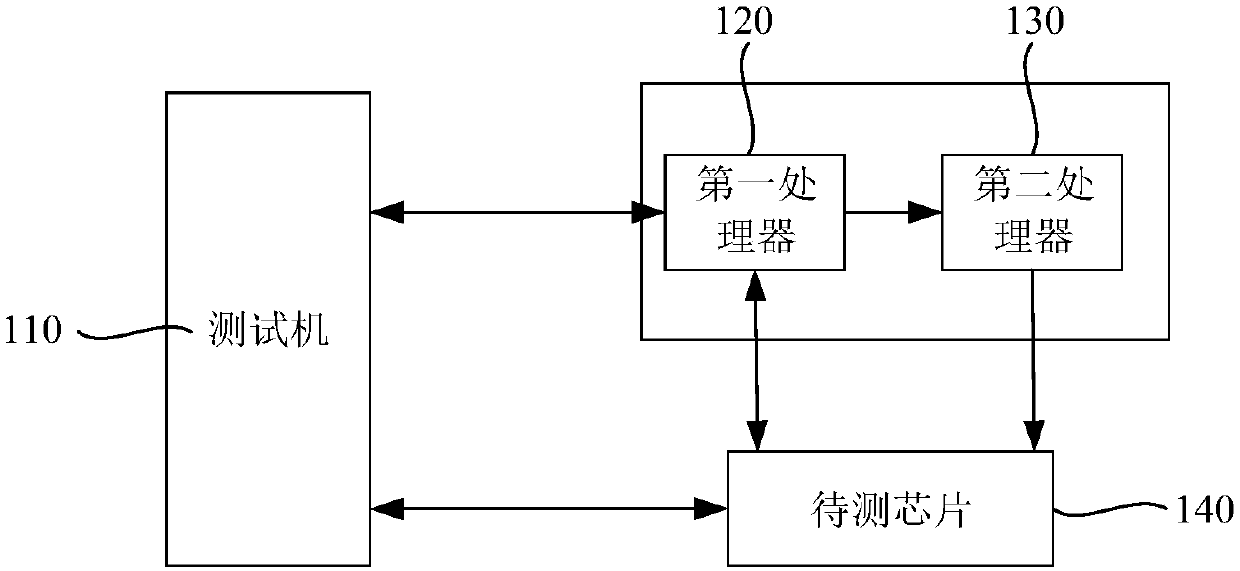

[0047] See figure 2 , figure 2It is a schematic diagram of another chip mass production testing system provided by the embodiment of the present invention. This embodiment introduces the test system proposed by the present invention in detail on the basis of the above embodiments. The testing system includes a testing machine 110 , a first processor 120 and a second processor 130 . The first processor 120 is electrically connected to the testing machine 110 and receives control instructions sent by the testing machine 110 . The second processor 130 is electrically connected to the first processor 120 and receives data information sent by the first processor 120 . Testing machine 110 carries out some direct current (Direct Current, be called for short DC), alternating current (Alternative Current, be called for short AC) parameter test of chip 140 to be tested, wherein, testing machine 110 alone completes the test of open short circuit, leakage current and quiescent working...

Embodiment 3

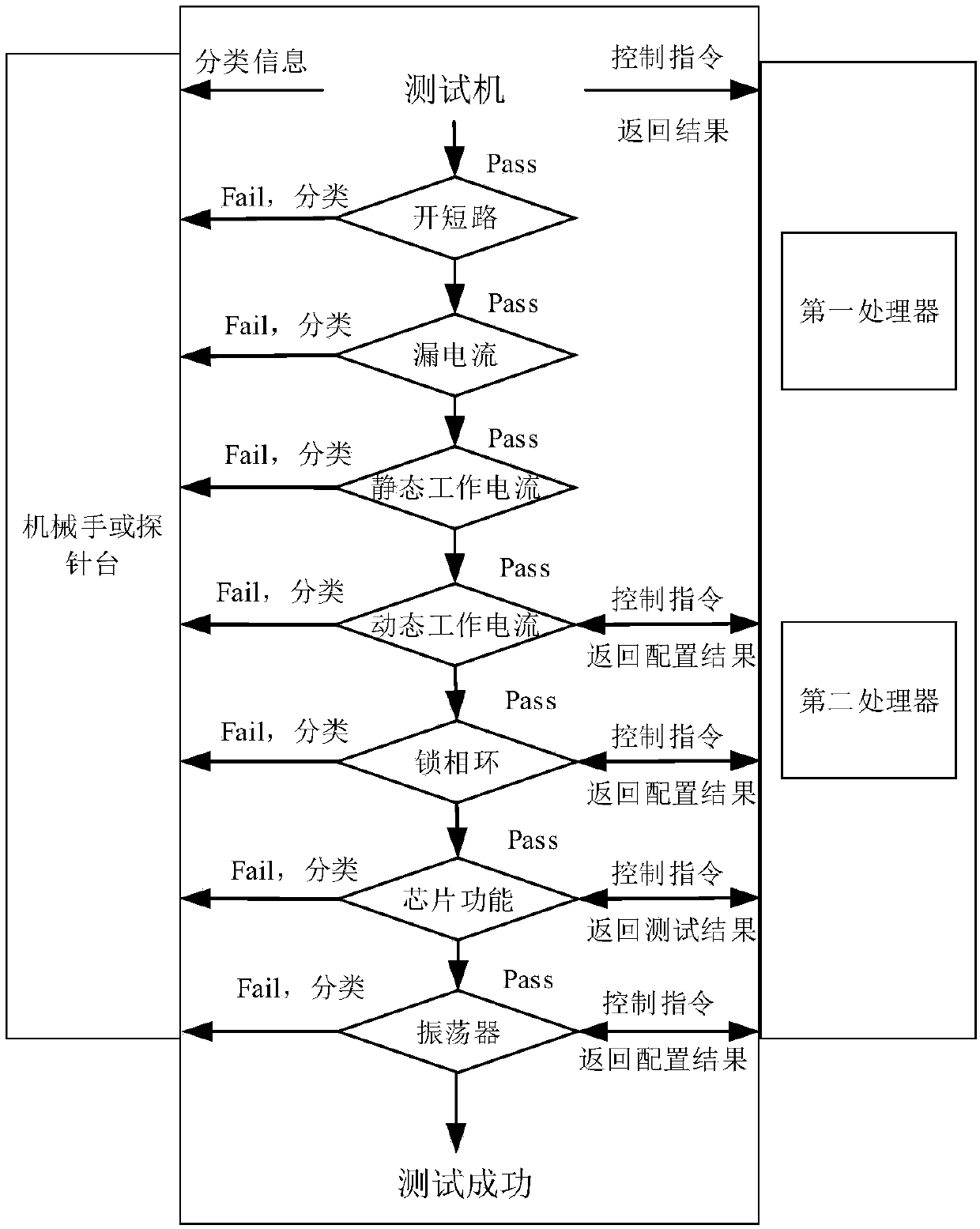

[0050] See Figure 3a ~ Figure 3b , Figure 3a A schematic flow chart of a chip mass production testing method provided by an embodiment of the present invention; Figure 3b It is a schematic flowchart of another chip mass production testing method provided by the embodiment of the present invention. This embodiment describes in detail the actual workflow of the testing method proposed by the present invention on the basis of the above embodiments. details as follows:

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com