Method and system for optimizing chip area and power consumption

A chip area and optimization method technology, applied in the direction of instruments, input/output to record carrier, calculation, etc., can solve the problems of register waste, chip area resource waste, execution unit limitation, etc., to improve performance and power consumption ratio, ensure Effects of functional correctness, area and power reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] The present invention will be described in detail below with reference to the accompanying drawings and examples. It should be noted that, in the case of no conflict, the embodiments in the present application and the features in the embodiments can be combined with each other.

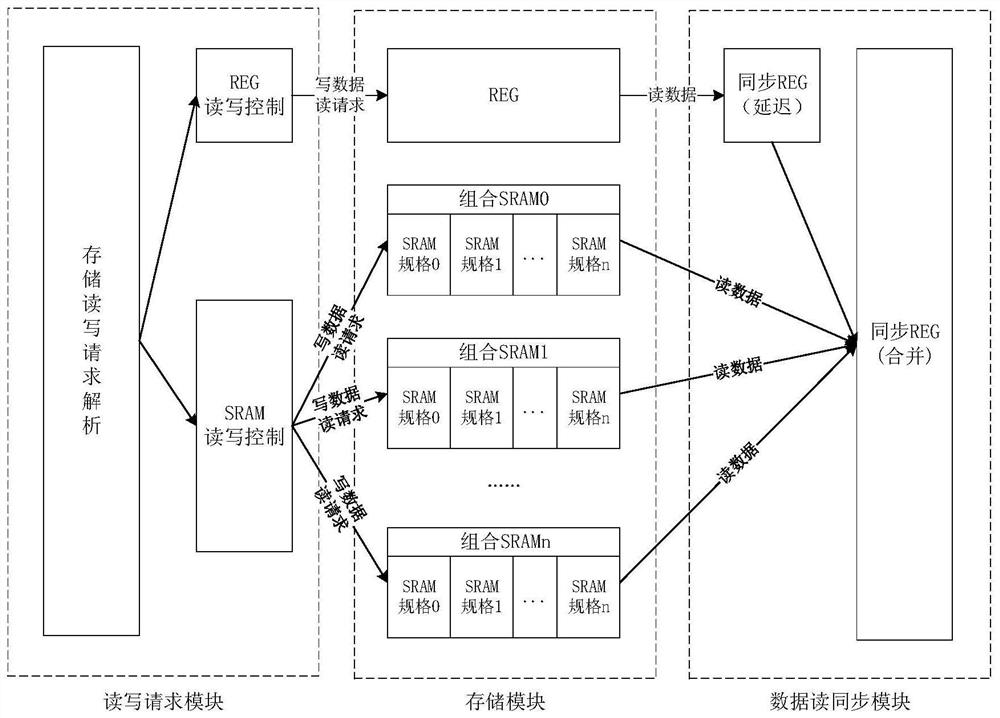

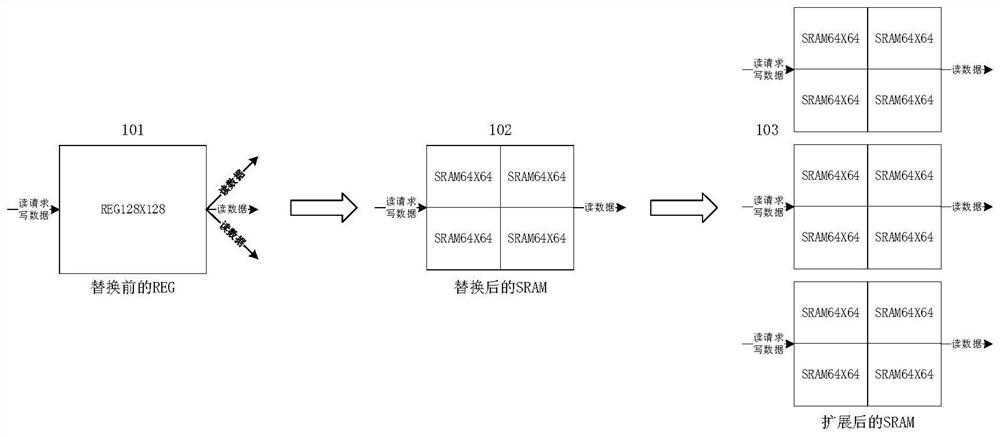

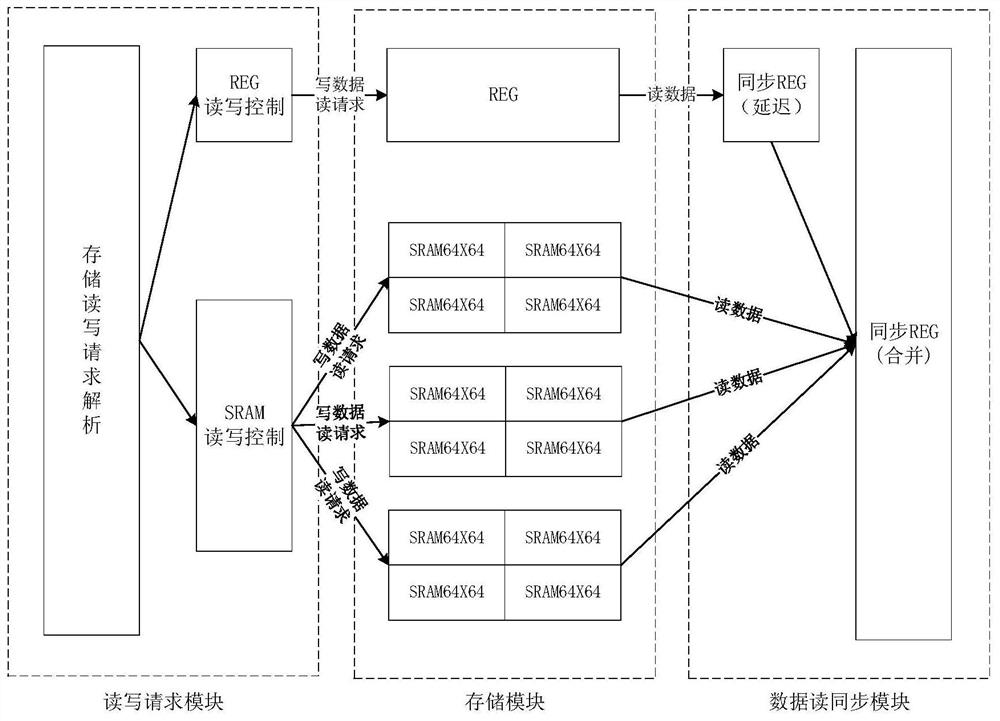

[0038] Such as figure 1 As shown, it is a schematic diagram of an example result of a chip area and power consumption optimization system of the present invention. A chip area and power consumption optimization system of the present invention includes: a read-write request module, a storage module and a data synchronization module. The main function of the read and write request module is to analyze the read and write requests, send the requests to the register and the SRAM read and write control module, and analyze the number of reads and writes in a single clock cycle of the register. The write data to the combined SRAM0-n is consistent, While read requests are independent. The main functio...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More