PCIE (Peripheral Component Interconnect Express) BOX board with PCIE card and GPU (Graphics Processing Unit) hyperoperation function

A function, PCA9555 technology, applied in the field of server BOX board design, can solve the problems of lower board performance, poor heat dissipation, and reduced board use space

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] The specific structure of the PCIE BOX board described in the present invention will be described below through an embodiment.

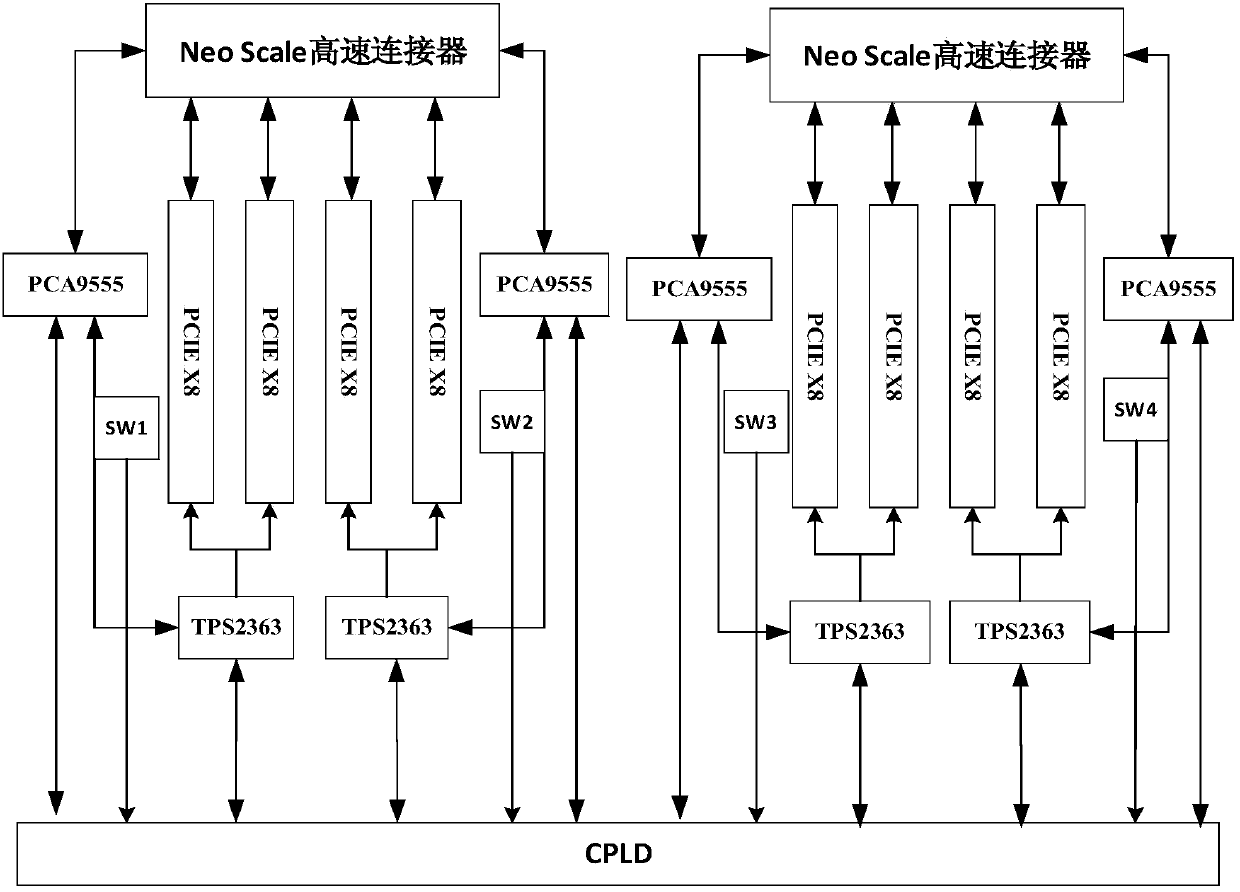

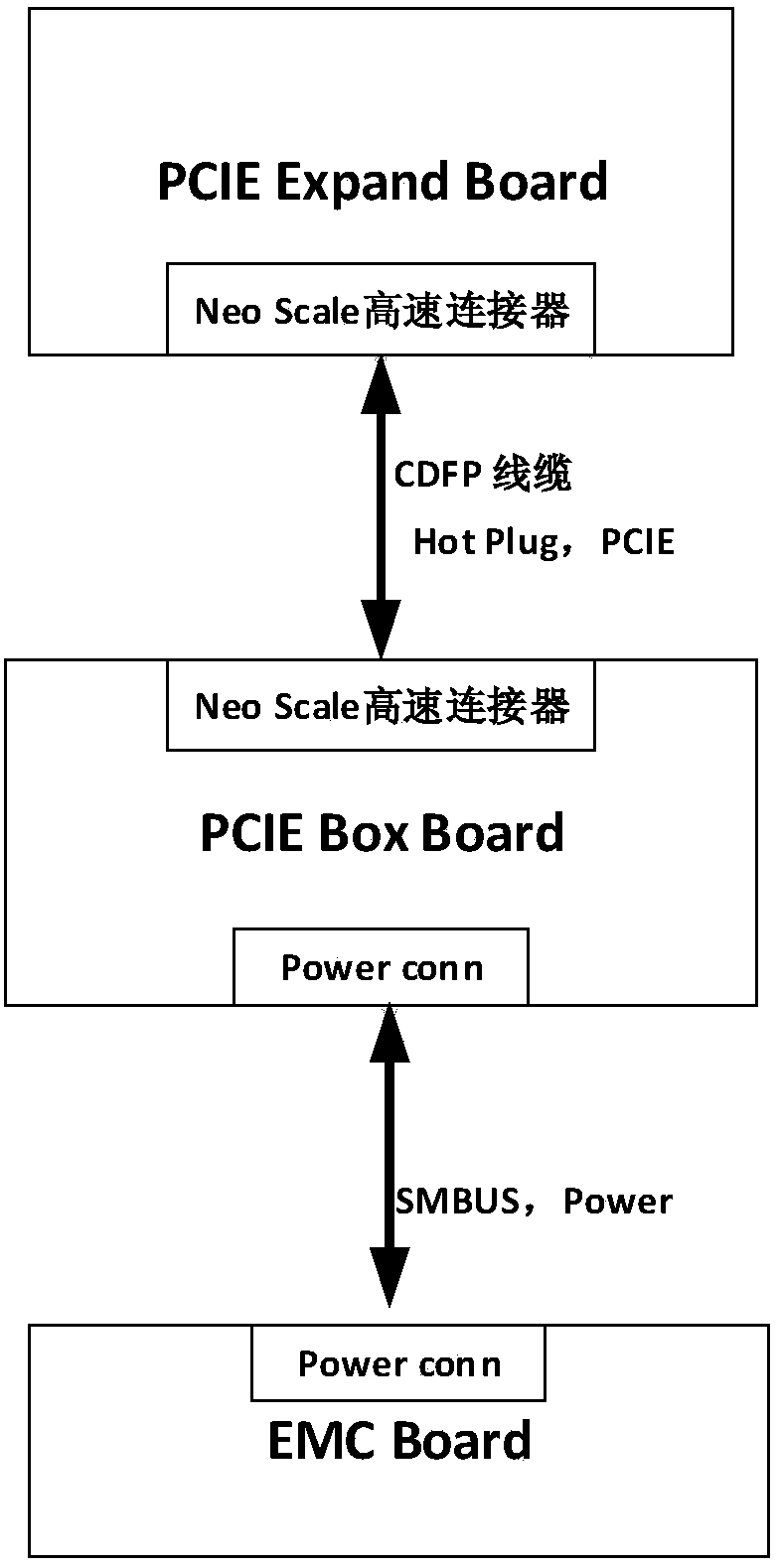

[0019] The specific implementation scheme that the PCIE BOX board technology of the present invention realizes is as attached figure 1 shown (Switch5-Switch8 not shown); BOX and PCIE Expand card, EMC board connection block diagram as attached figure 2 shown.

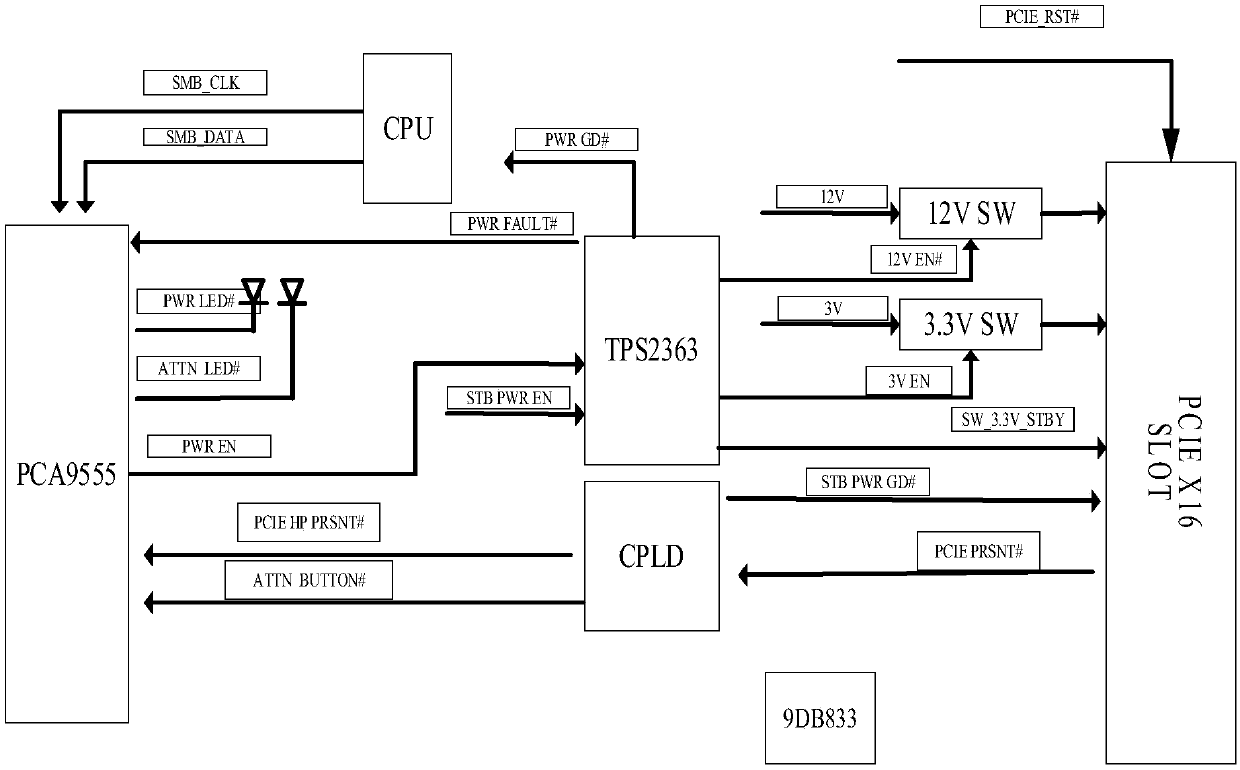

[0020] BOX board power supply mainly includes P12V, P3V3, P3V3_STBY. P12V power comes from the EMC board; P12V_STBY uses the P12V obtained from the soft start line, and P12V generates P3V3 and P3V3_STBY power through the power chip.

[0021] There are three main functions of the BOX board, specifically the PCIE hot-swappable function, the Switch switches PCIEX8 to PCIEX16 line, and the GPU card can be inserted to realize data acceleration calculation, and the BMC (Baseboard Management Controller) chip of the EMC board monitors the BOX board through the SMBUS bus card function. Let's...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com