An anti-dpa attack method using clock disorder technology and chaotic trigger

A technology using clocks and flip-flops, applied in the field of anti-DPA attack, can solve the problems of increased production cost, increased circuit area or power consumption, etc., to achieve high security, weakened correlation, and weakened attack strength.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

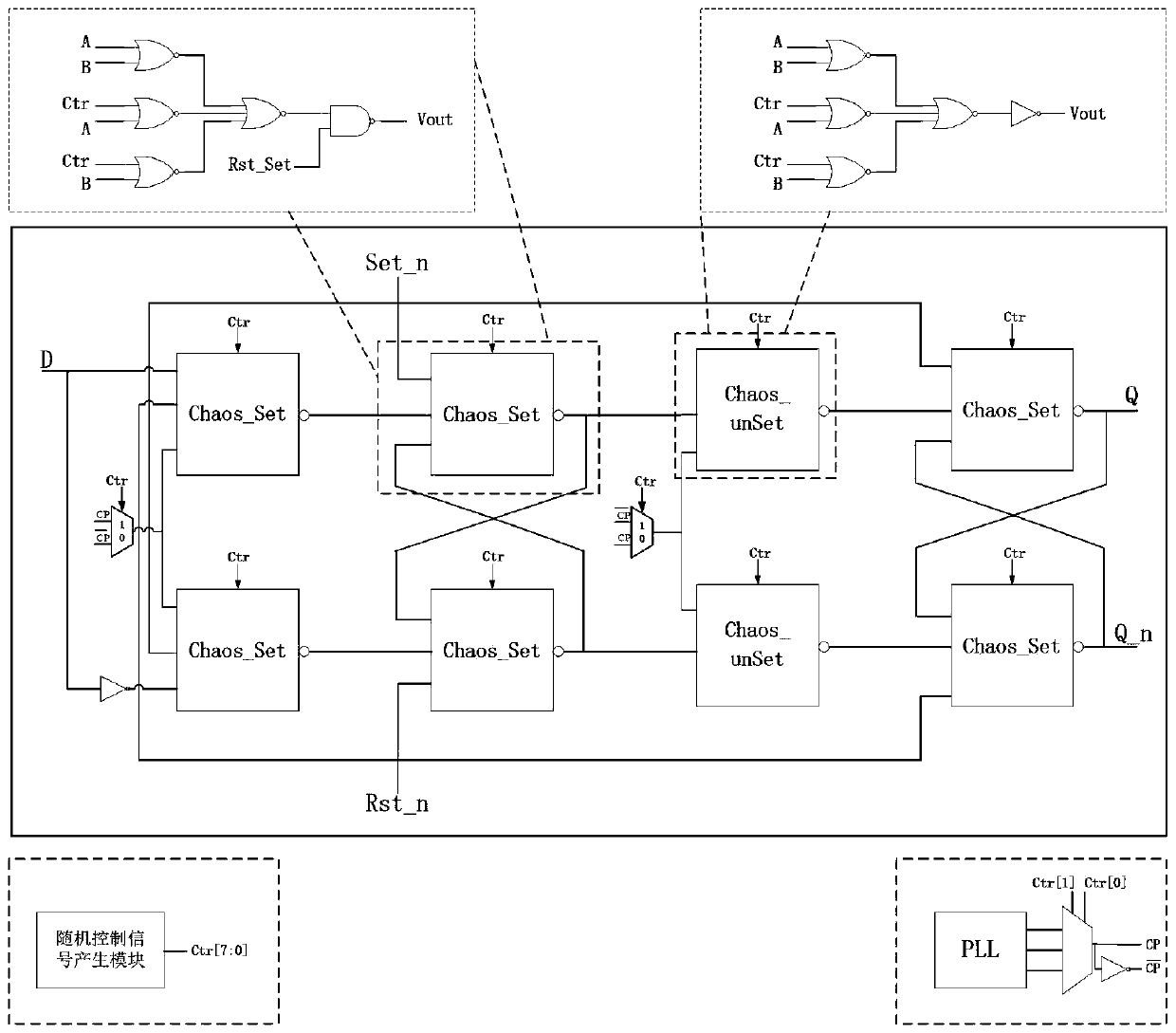

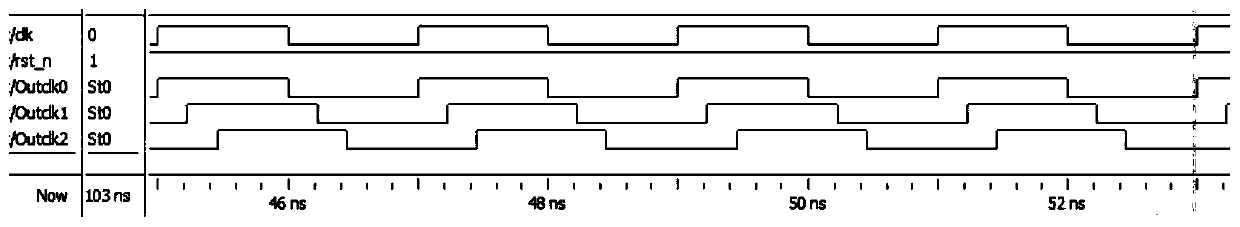

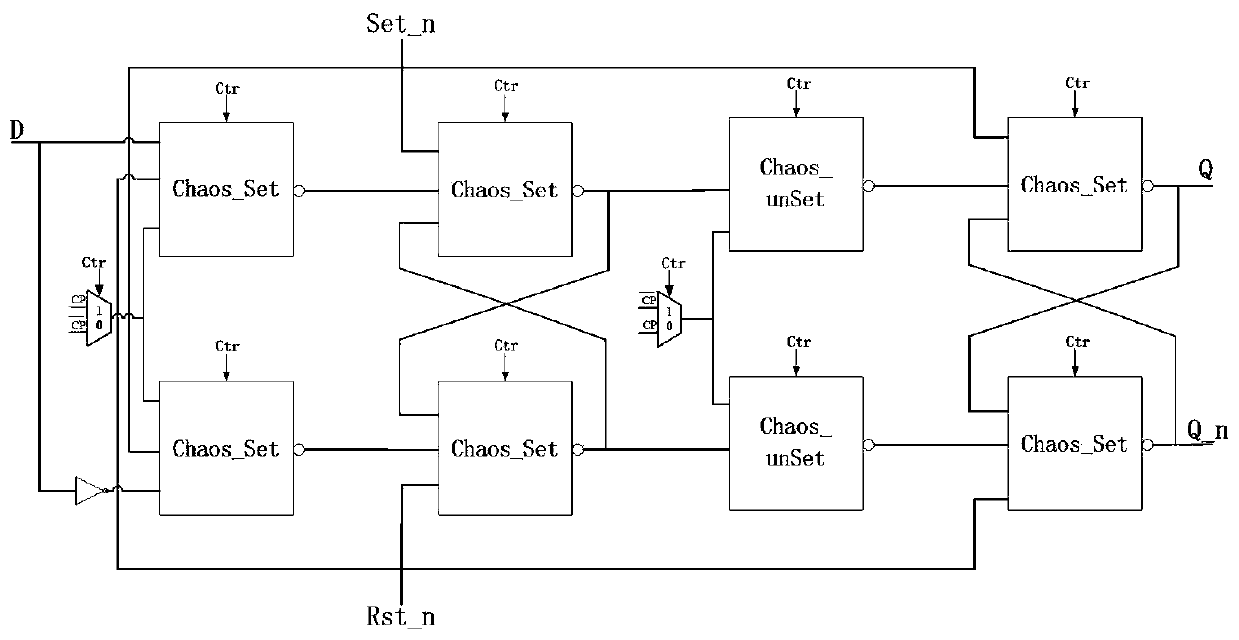

[0025] This embodiment provides an anti-DPA attack method using clock out-of-sequence technology and chaotic triggers. The general schematic diagram of the method is as follows figure 1As shown, at the beginning of each encryption operation, an 8-bit random control signal is generated by the random control signal generation module, and one bit of the generated 8-bit random control signal is used when the chaos trigger module is in the reset state The control signal controls the chaotic unit inside the chaotic trigger module, and realizes the internal chaotic unit NAND output under the low level of the control signal, and the chaotic trigger is composed of NAND gates; the internal chaotic unit is realized under the high level of the control signal NOR output, the chaotic flip-flop is composed of NOR gates; thereby realizing the reconstruction of the chaotic flip-flop; when the chaotic flip-flop module is in the reset state, the two least significant bits of the 8-bit random cont...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More