Semiconductor structure and forming method thereof

A technology of semiconductor and gate structure, which is applied in the field of semiconductor structure and its formation, can solve the problems of low breakdown voltage and achieve the effect of increasing breakdown voltage and reducing surface electric field

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

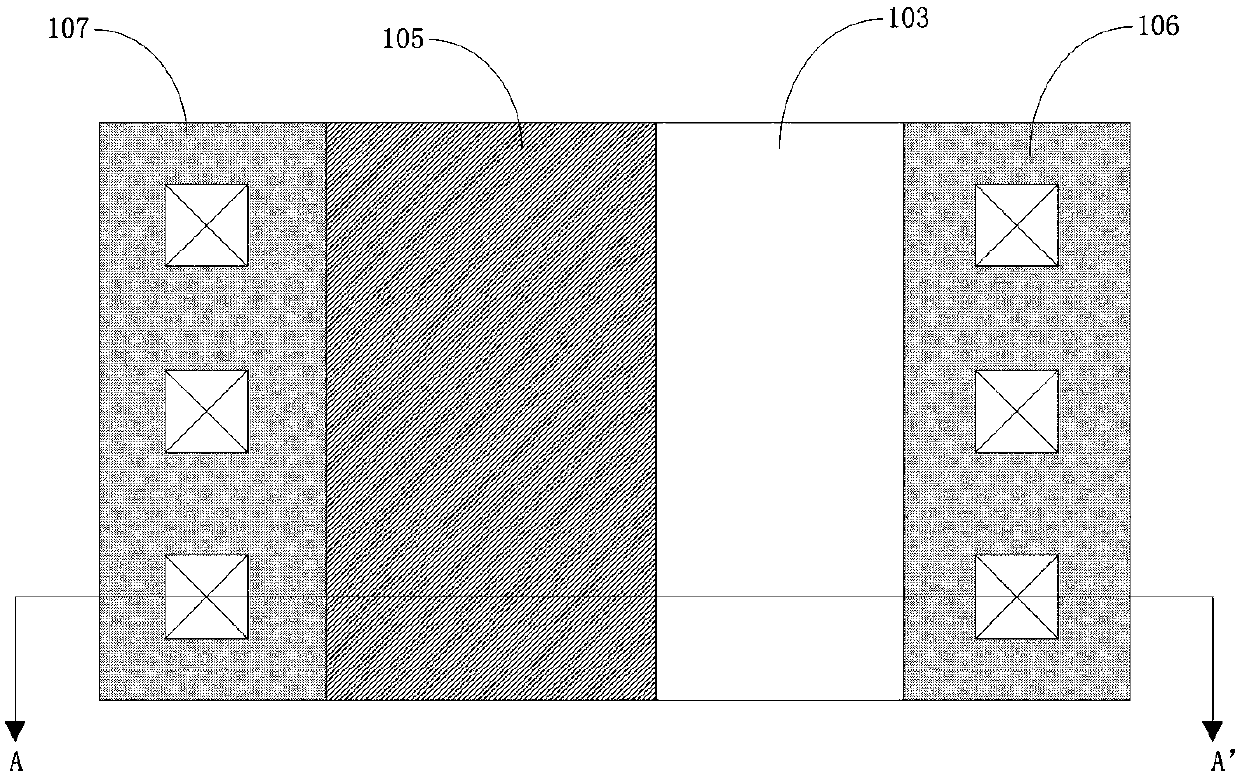

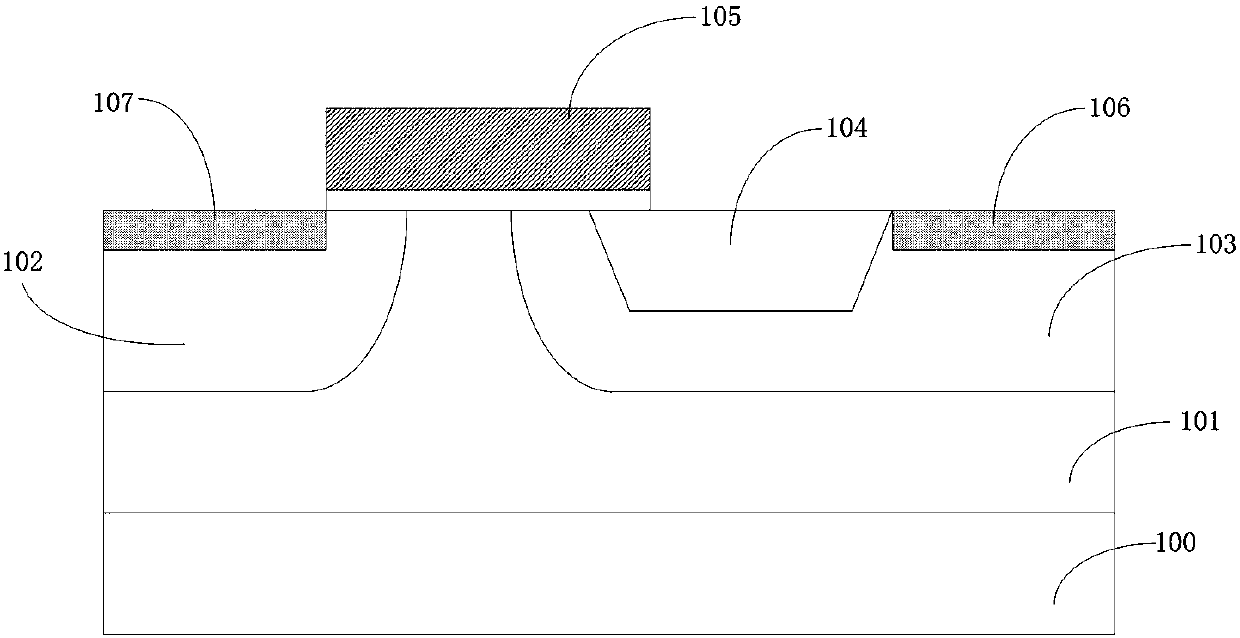

[0027] Please refer to figure 1 with figure 2 ,in figure 2 yes figure 1 Schematic cross-section along line AA'. In the manufacture of the existing P-type LDMOS device, since the active region at the junction of the drain terminal gate and the isolation region has a large surface electric field, the surface electric field limits the breakdown voltage of the P-type LDMOS device. The inventors have found through research that the breakdown voltage of the LDMOS device can be effectively improved by reducing the surface electric field of the active region at the junction of the drain gate and the isolation region.

[0028] To this end, the present invention provides a semiconductor structure and its formation method. By forming interdigitated channel regions and drift regions in the body region, lateral loss is formed between the channel extension region and the drift region on the channel region. do. The lateral depletion extends to the entire active region at the junction ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More