LDMOS structure in ultrahigh voltage BCD technology

An ultra-high voltage, process technology, applied in the direction of electrical components, circuits, semiconductor devices, etc., to achieve low gate parasitic resistance, increase switching frequency, and reduce parasitic resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

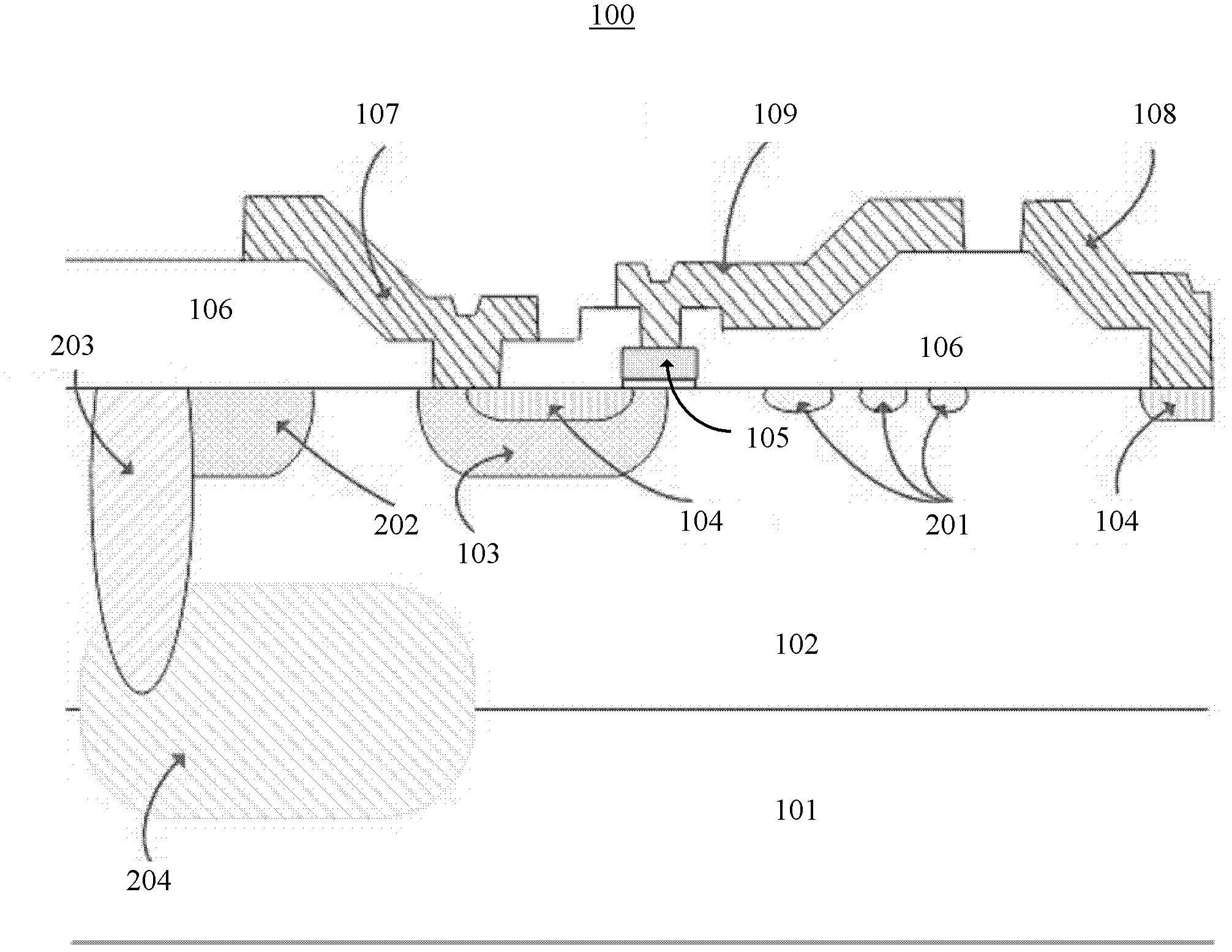

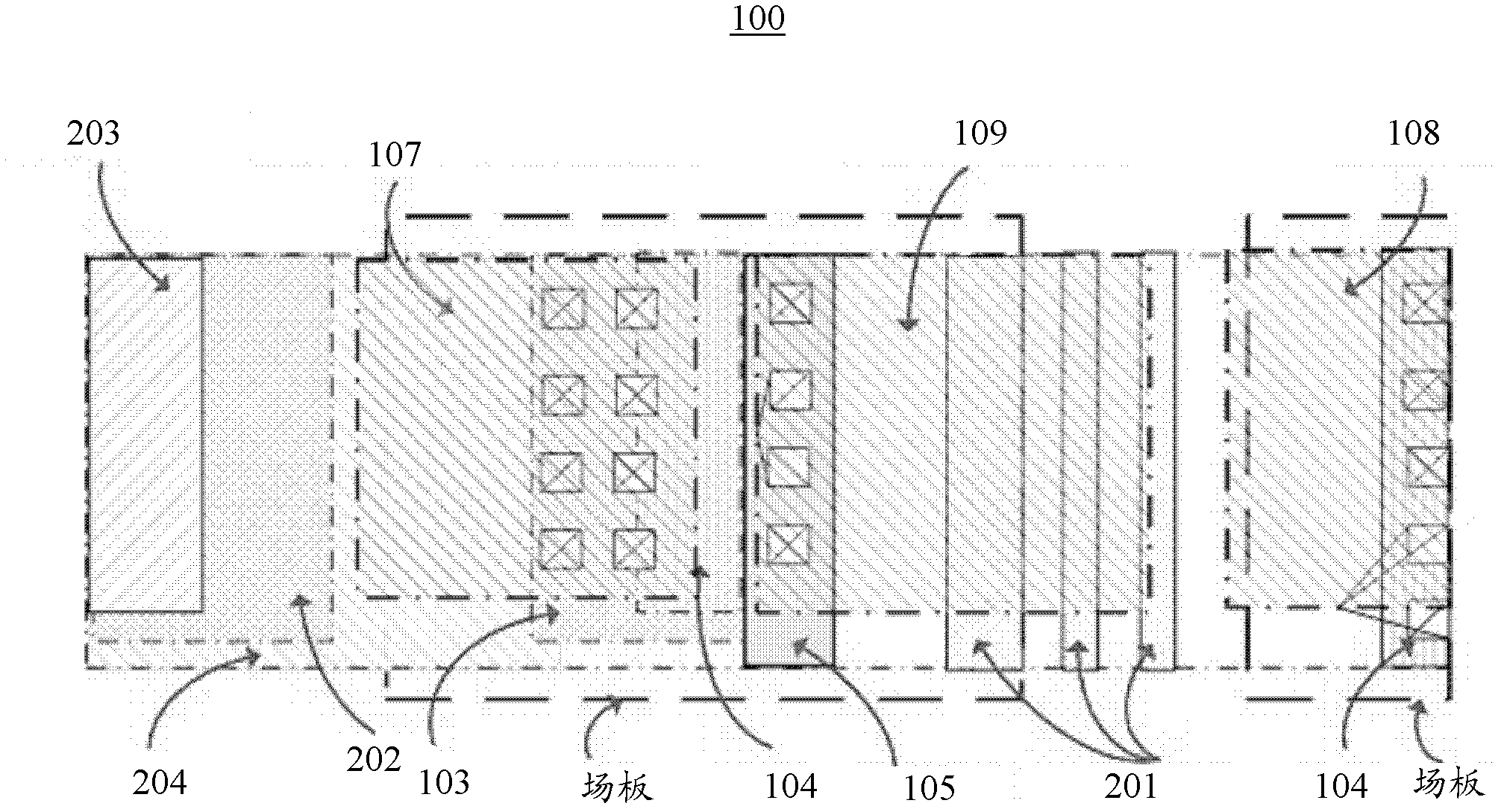

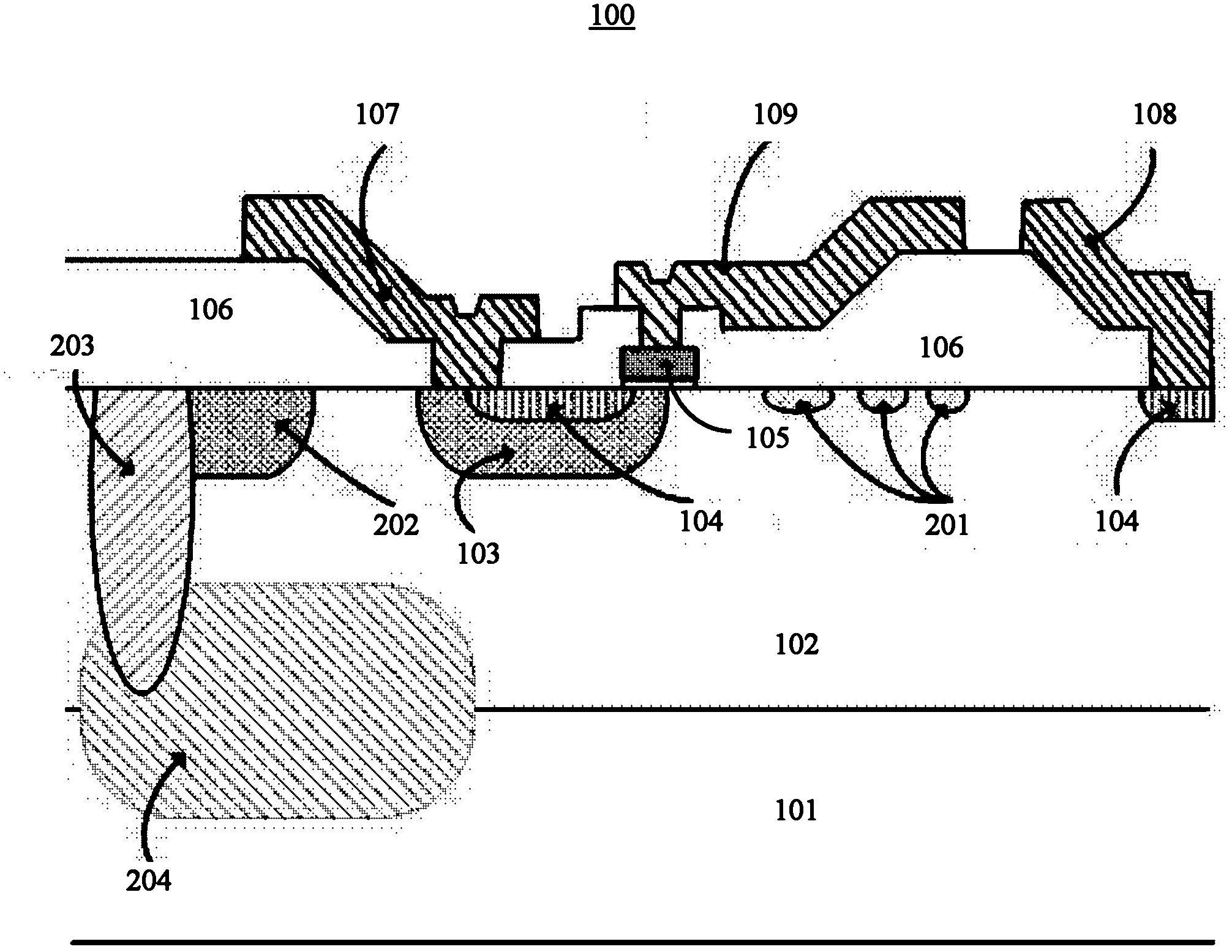

[0028] The present invention will be further described below in conjunction with specific embodiment and accompanying drawing, set forth more details in the following description so as to fully understand the present invention, but the present invention can obviously be implemented in many other ways different from this description, Those skilled in the art can make similar promotions and deductions based on actual application situations without violating the connotation of the present invention, so the content of this specific embodiment should not limit the protection scope of the present invention.

[0029] The present invention is applicable to various ultra-high voltage LDMOS gate metals, not limited to the LDMOS structure shown in this embodiment.

[0030] When the ultra-high voltage LDMOS structure is used in high-frequency switching applications, high breakdown voltage in the off state and low on-resistance in the on-state are the basic requirements. To obtain low on-re...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More