FFT reuse method

A technology of multiplexing processing and data, applied in the field of signal processing, can solve the problems of occupied resources, fast and difficult parallel processing operation, and achieve the effect of balancing contradictions, optimizing the occupation of logic resources, and reducing the complexity of system processing.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

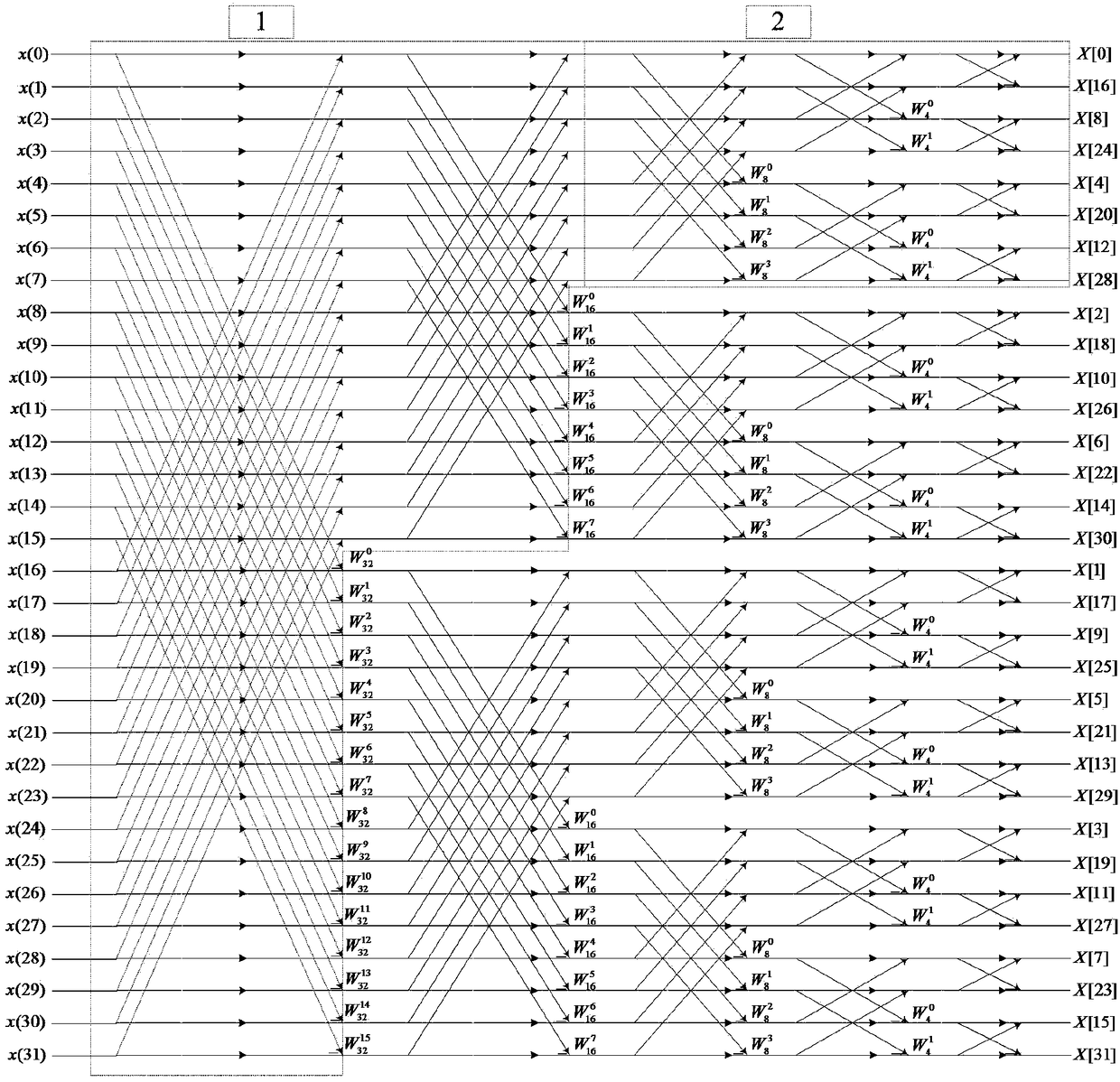

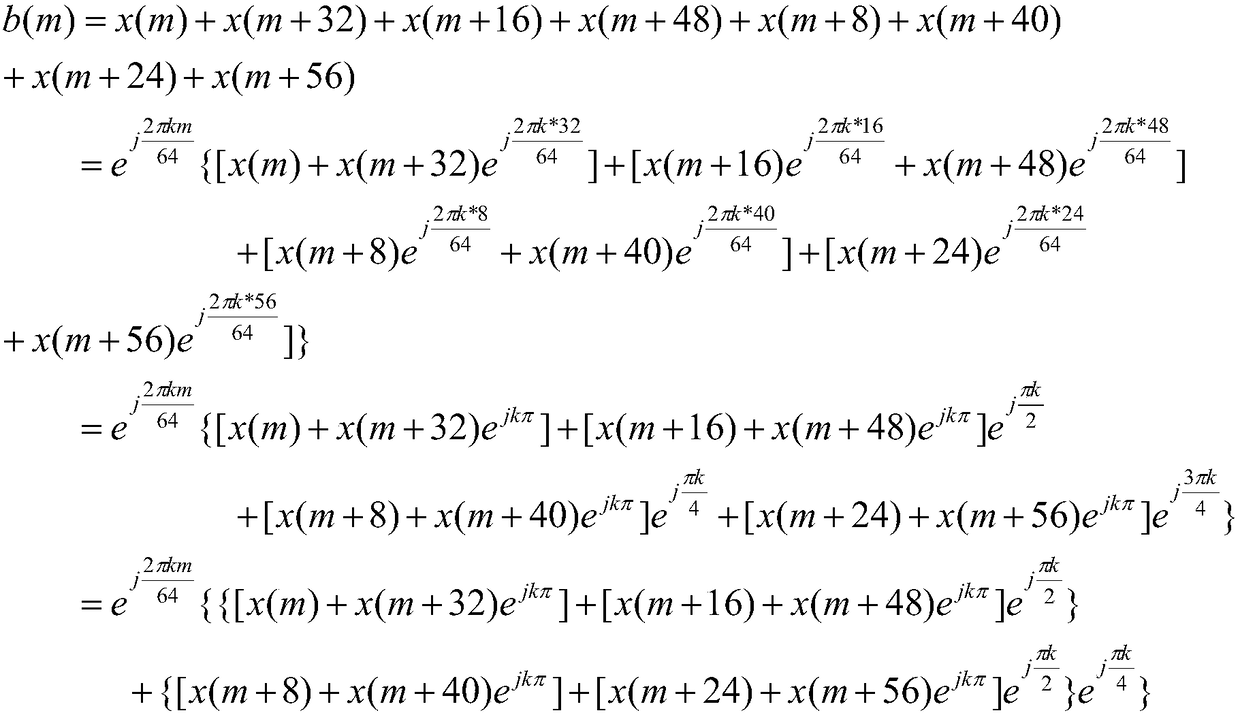

[0036] Set a 64-channel filter bank (K=64), the high-speed signal sampling rate fs is 2.6GHz, the external AD is divided into 8 phases (8-fold extraction, D=8) and enters the FPGA, and the data rate of each phase is 325MHz, that is, the FPGA runs The rate is 325MHz; the filter bank output rate fo=fs / 64=40.625MHz, the multiplexing multiple of each phase data=fpga operation rate / output rate=325 / 40.625=8, that is, 8 times multiplexing; the specific steps are as follows:

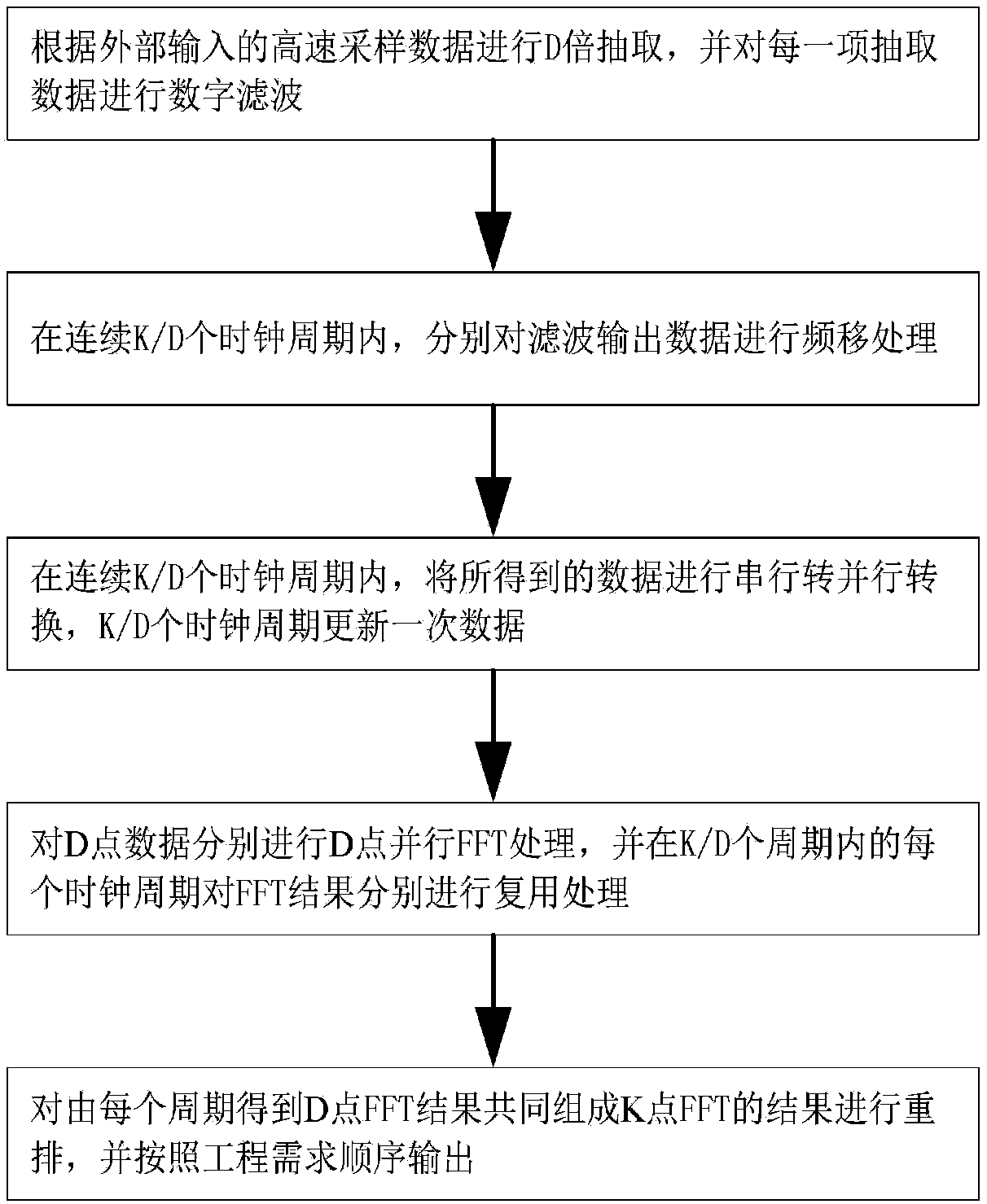

[0037] Step 1, perform D-fold extraction according to the high-speed sampling data input from the outside, and perform digital filtering on each item of extracted data;

[0038] Step 11, first divide the input 2.6GHz high-speed sampling data into 8 phases and perform FPGA acquisition and latching;

[0039] Step 12, each phase data is extracted by 8 times;

[0040] Step 13, prepare for equivalent extraction of the FIR low-pass filter coefficients according to the 8-fold extraction sampling data;

[0041] Step 1...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More