Bonding alignment precision detection method and semiconductor device

A detection method and technology of alignment accuracy, applied in the direction of semiconductor devices, semiconductor/solid-state device parts, semiconductor/solid-state device testing/measurement, etc. drop etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

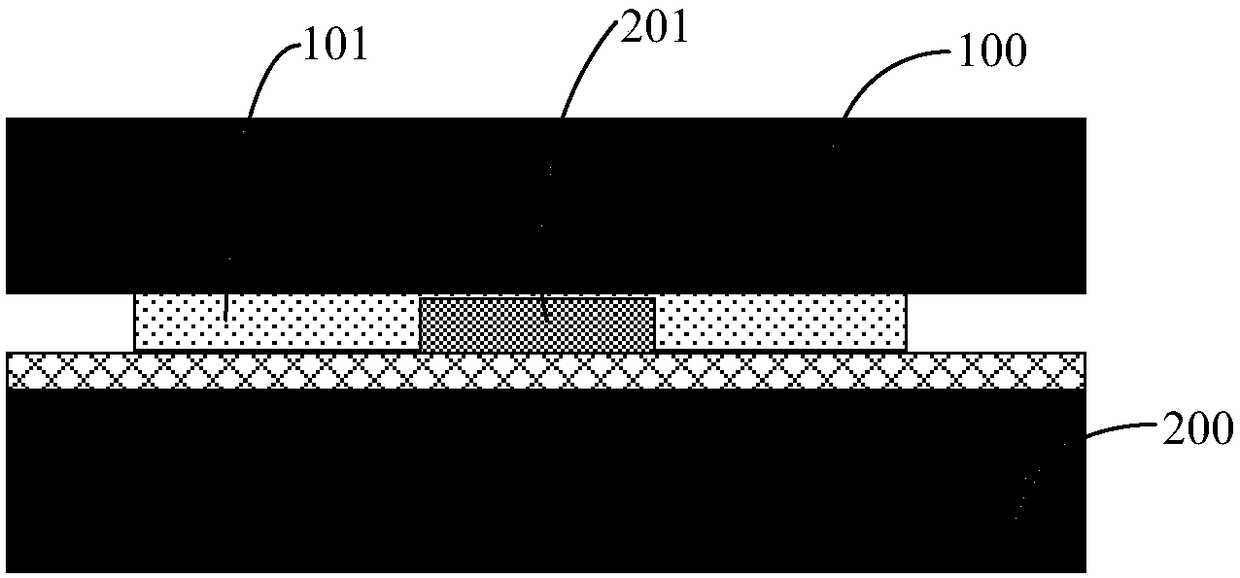

[0068] In order to solve the above technical problems, the present invention provides a detection method of bonding alignment accuracy, such as image 3 As shown, it mainly includes the following steps:

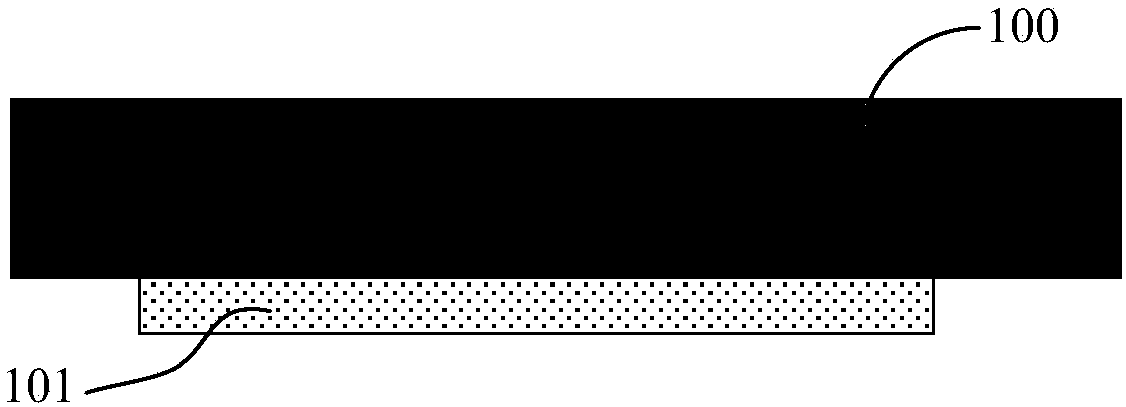

[0069] Step S1, providing a first device wafer, forming a first alignment mark on the first device wafer, wherein the shape of the first alignment mark is a ring;

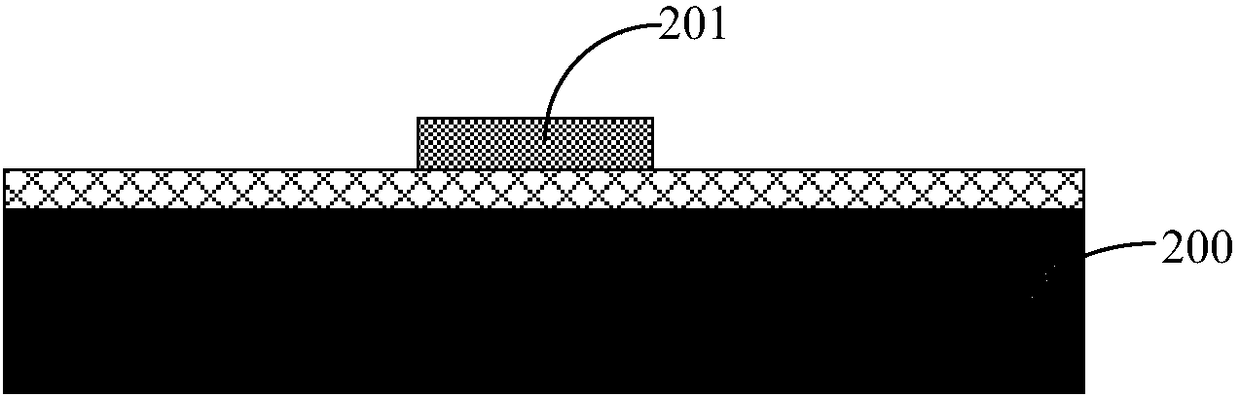

[0070] Step S2, providing a second device wafer, and forming a second alignment mark on the second device wafer;

[0071] Step S3, forming a dielectric layer to cover the surface of the second device wafer on which the second alignment mark is formed, and the surface of the dielectric layer is flush with the surface of the second alignment mark;

[0072] Step S4, forming a dummy bonding layer surrounding the second alignment mark on the dielectric layer;

[0073] Step S5, bonding the first device wafer and the second device wafer, wherein the first alignment mark and the dummy bonding layer are aligned and bonde...

Embodiment 2

[0146] The present invention also provides a semiconductor device, which can detect the bonding alignment accuracy of the semiconductor device by using the detection method of the first embodiment.

[0147] Such as Figure 2G and Figure 2H As shown, the semiconductor device mainly includes:

[0148] A first device wafer 300, on which a first alignment mark 3021 is formed, wherein the shape of the first alignment mark 3021 is ring-shaped;

[0149] A second device wafer 400, on which a second alignment mark 4021 is formed;

[0150] A dielectric layer 403 is formed on the surface of the second device wafer 400 on which the second alignment mark 4021 is formed, and the surface of the dielectric layer 403 is flush with the surface of the second alignment mark 4021;

[0151] A dummy bonding layer surrounding the second alignment mark 4021 is formed on the dielectric layer 403;

[0152] The first device wafer 300 and the second device wafer 400 are bonded, wherein the first alig...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More