Wafer level metal shielded packaging structure and manufacturing method thereof

A technology of metal shielding and packaging structure, which is applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., and can solve the problems of increasing operation restrictions, increasing production costs, and tediousness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

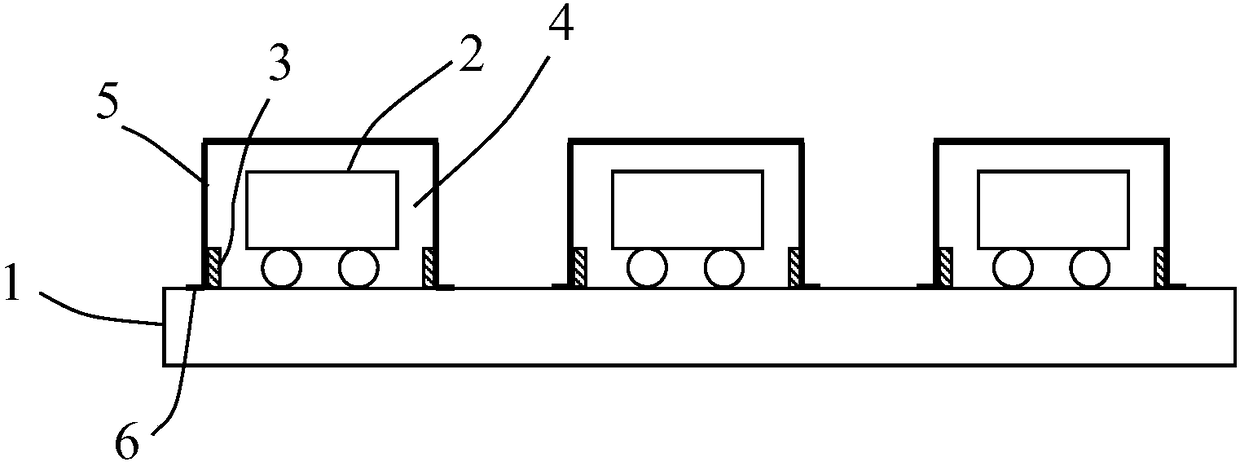

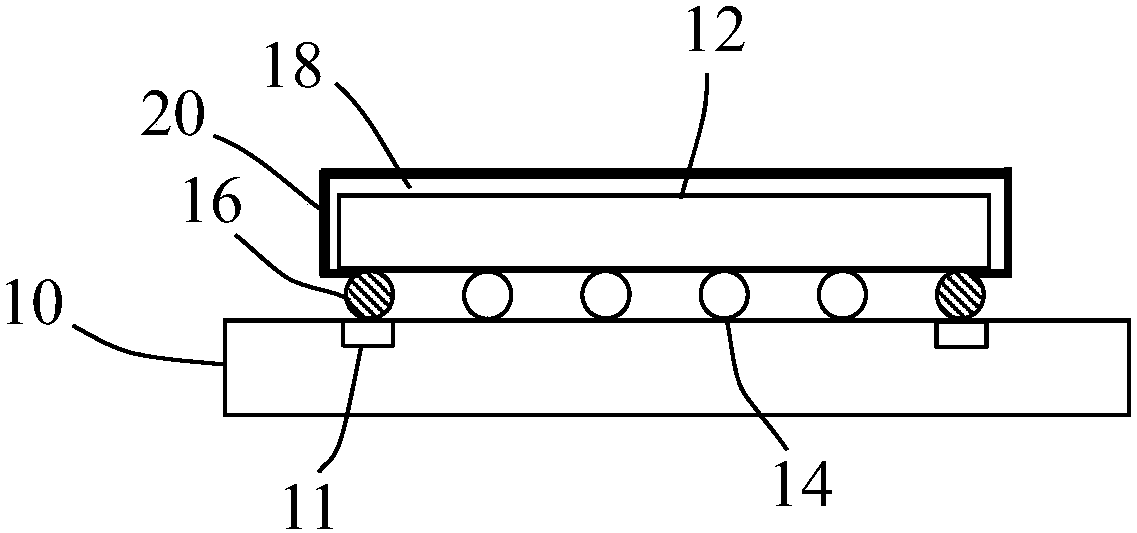

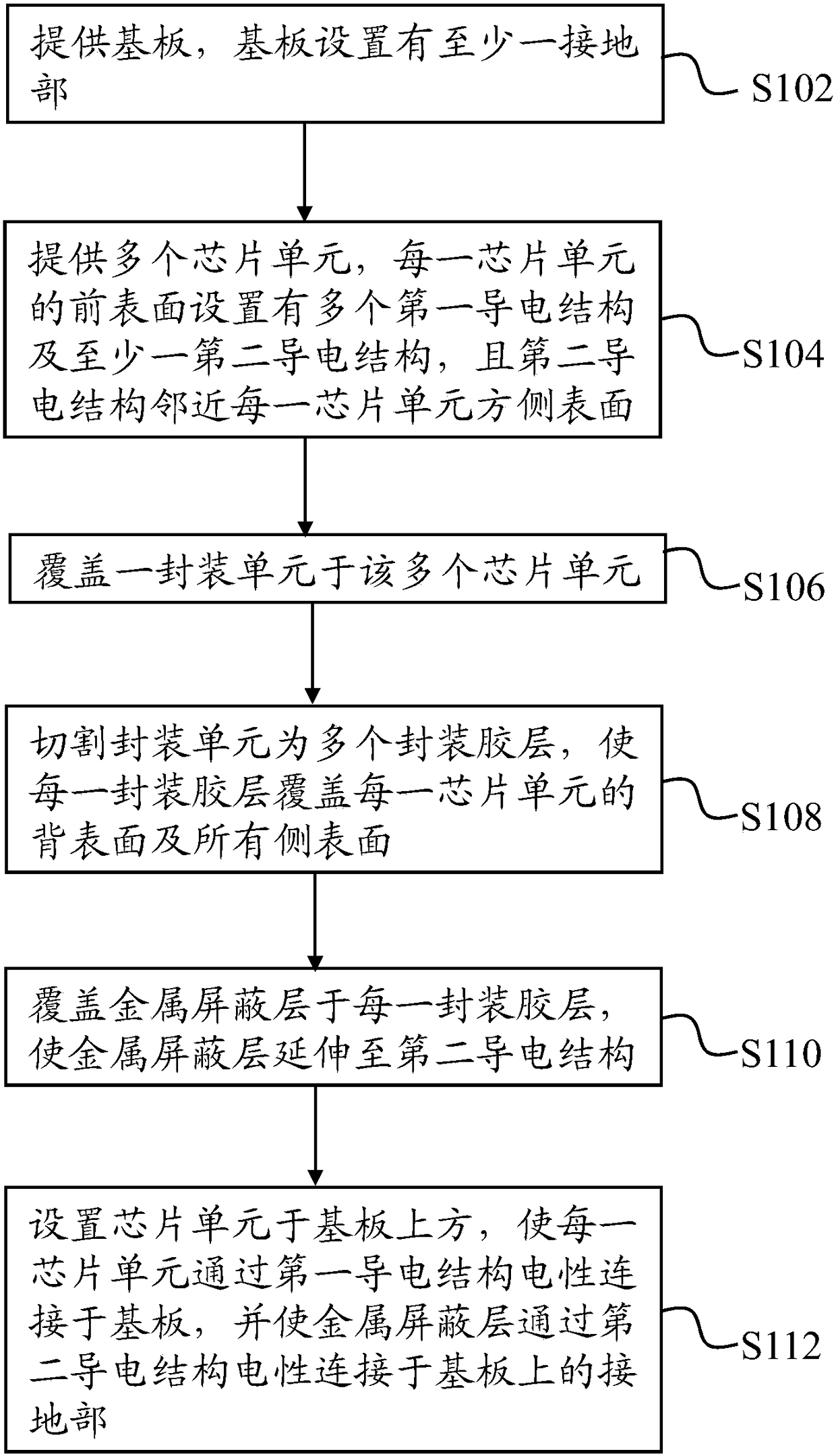

[0016] Such as figure 2 Shown is a cross-sectional view of a wafer-level metal shield package structure according to an embodiment of the present invention. The wafer-level metal-shielded packaging structure includes a substrate 10 , a chip unit 12 , a first conductive structure 14 , a second conductive structure 16 , a packaging adhesive layer 18 and a metal shielding layer 20 .

[0017] Wherein, the substrate 10 can be a printed circuit board or a silicon wafer substrate, and has a plurality of ground portions 11 on its surface. The chip unit 12 is arranged above the substrate 10, and it can be a fan-in structure or a fan-out structure; here, the lower surface of the chip unit 12 is defined as the front surface, the upper surface of the chip unit 12 is the back surface, and The surface is a side surface. The first conductive structure 14 is arranged on the surface of the substrate 10 and is located on the front surface of the chip unit 12. The first conductive structure 1...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More