Wafer packaging method and packaging structure

A wafer packaging and packaging layer technology, which is applied in the manufacturing of electrical components, electric solid-state devices, semiconductor/solid-state devices, etc., can solve the problems of large volume and thickness of packaging structures, being easily affected by external magnetic fields, and complex packaging methods. Achieve good process compatibility, good insulation effect, and simplify the packaging method.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0035] Embodiment 1 provides a wafer packaging method, comprising the following steps:

[0036] S01: Provide a device wafer, in which a plurality of first chips are formed, and first electrodes are formed on the first chips;

[0037] S02: Forming a first dielectric layer and a first conductive bump on the device wafer, the first dielectric layer and the first conductive bump being flush with the surface on a side away from the first chip;

[0038] S03: providing a plurality of second chips, on which second electrodes are formed;

[0039] S04: forming a second dielectric layer and a second conductive bump on the second chip, where the second dielectric layer and the second conductive bump are flush with the surface on a side away from the second chip;

[0040] S05: Bond the second dielectric layer to the first dielectric layer, and align and bond the second conductive bump to the first conductive bump, so that the second chip is bonded to the on the device wafer;

[0041] S0...

Embodiment 2

[0079] This embodiment provides a wafer packaging structure, Figure 13 It shows a schematic cross-sectional structure diagram of a wafer packaging structure in Embodiment 2, please refer to Figure 13 , the wafer package structure, comprising:

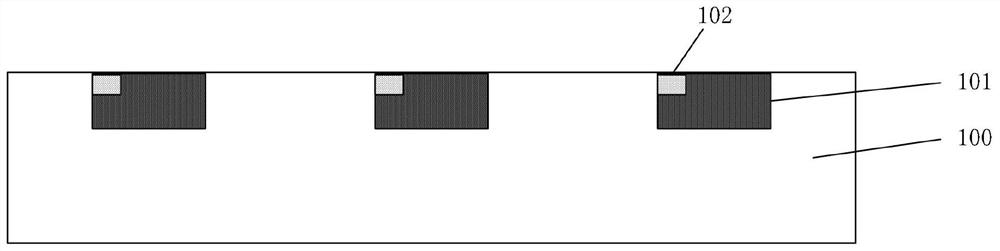

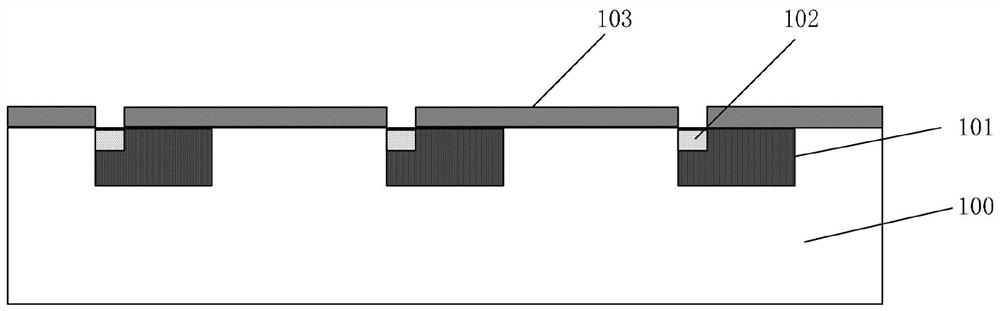

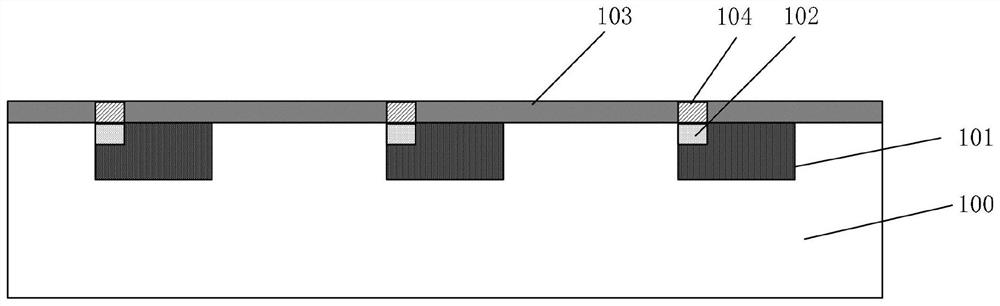

[0080] A device wafer 100, wherein a plurality of first chips 101 are formed in the device wafer 100, and first electrodes 102 are formed on the surface of the first chips 101;

[0081] a first conductive bump 104, disposed on the first electrode 102;

[0082] The first dielectric layer 103 is formed on the first chip 101, the side surface of the first dielectric layer 103 away from the first chip 101 and the first conductive bump 104 away from the first chip 101 one side of the surface is flush;

[0083] a second chip 202, on which a second electrode 203 is formed;

[0084] a second conductive bump 205, the second conductive bump 205 is disposed on the second electrode 203, and the second conductive bump 205 is bonded to the firs...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More