Dynamic random access memory

A technology of dynamic random access and memory, applied in the field of semiconductors, can solve problems such as errors, achieve the effect of reducing soft errors and increasing manufacturing costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

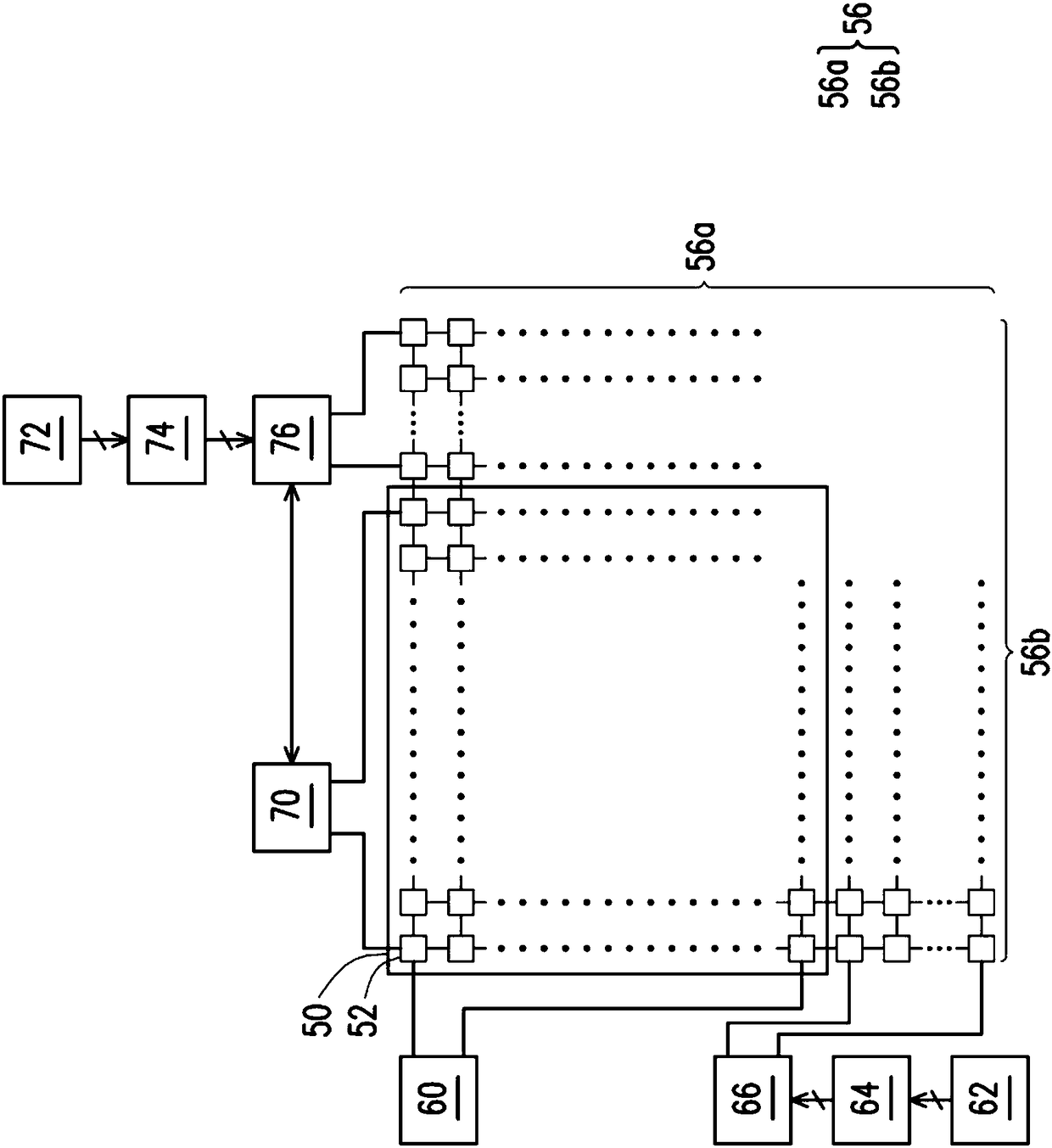

[0029] Generally, the architecture of a Dynamic Random Access Memory (DRAM) includes a main block composed of a memory cell array, and also includes redundant element units. The redundant element unit generally includes a plurality of redundant memory cells (redundant cells), a decoder (decoder), a fuse (e-fuse), and a latch (latch) and other blocks. For the plurality of memory cells of the memory cell array of the main block, for example, after the manufacturing is completed or any time to be tested, the test procedure will be started. After testing, when it is found that at least one memory cell cannot store data correctly, these memory cells are regarded as damaged memory cells (defective cell(s)), and their data addresses will use fuses to store the corresponding row address and column address. When the dynamic random access memory is in normal use, the address information stored in the fuse will be downloaded to the latch block, and then the decoder will activate the cor...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More