Configurable network-on-chip fault tolerance method

An on-chip network, fault-tolerant mechanism technology, applied in the field of fault-tolerance, can solve the problems of high delay and high power consumption of fault-tolerant strategies, and achieve the effect of improving reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

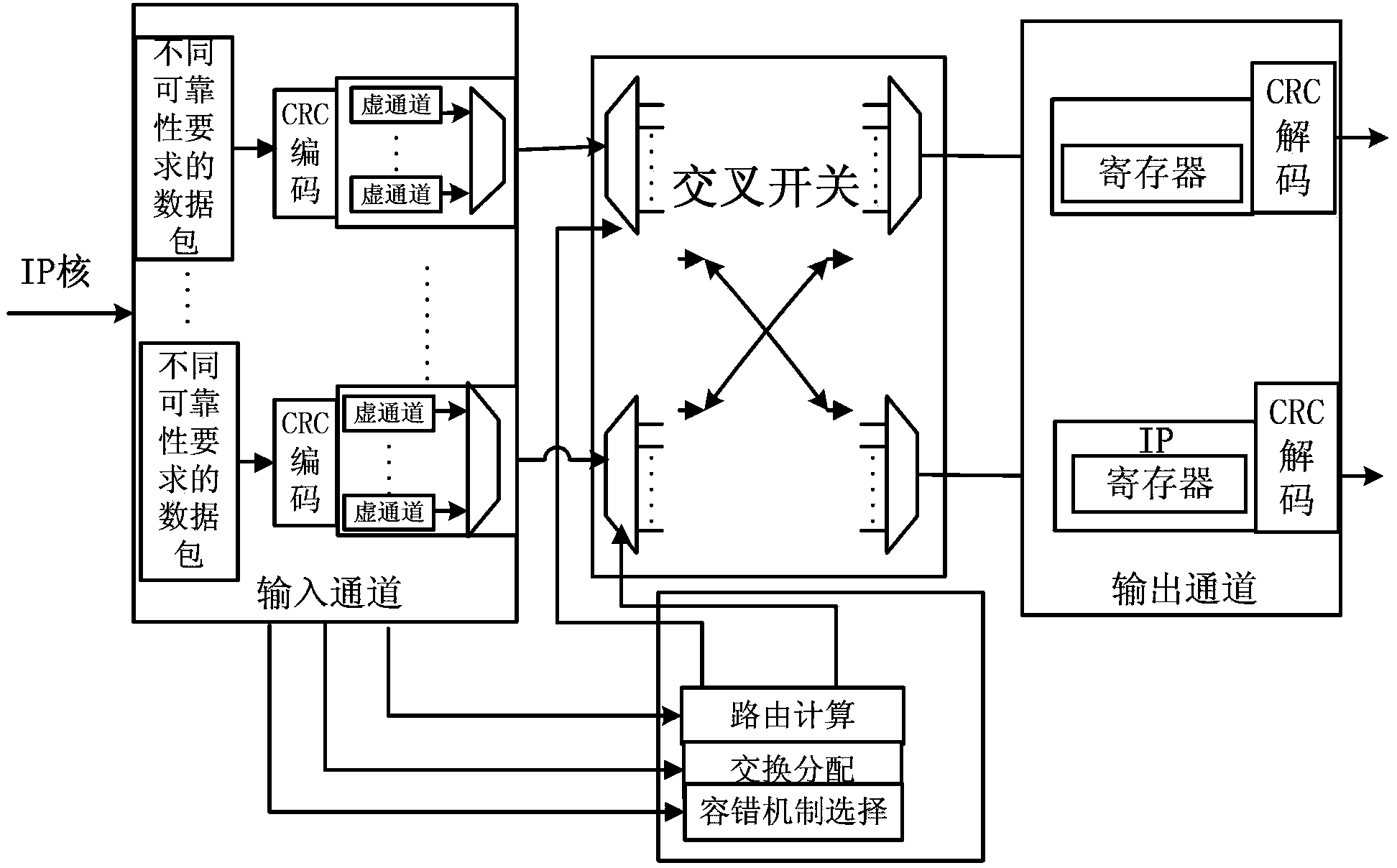

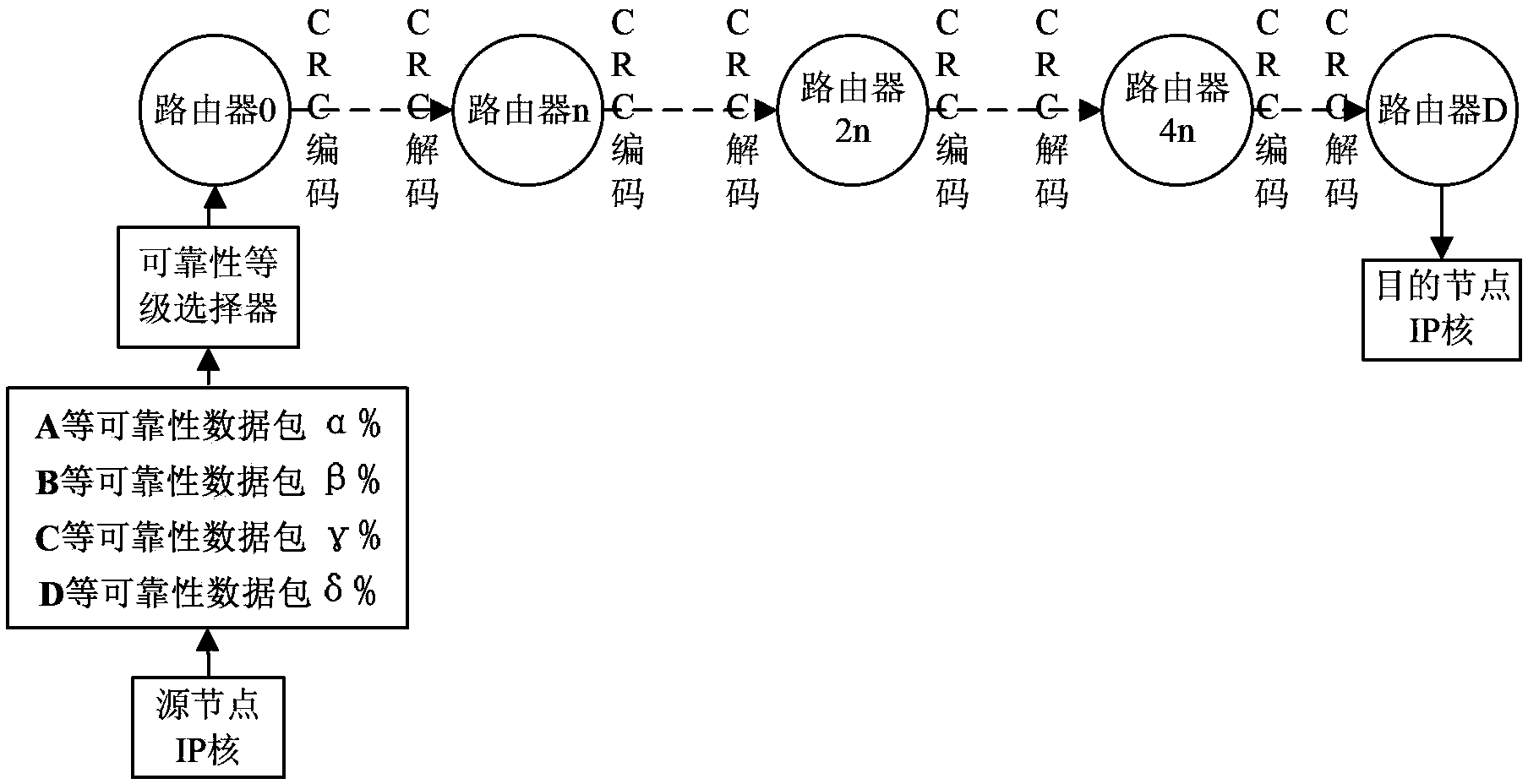

[0023] Specific implementation mode one, the following combination Figure 1 to Figure 5 Describe this embodiment, the configurable network-on-chip fault-tolerant method described in this embodiment is implemented based on a router, and the router includes a CRC encoding module, a CRC decoding module and a fault-tolerant mechanism selection module. In the input channel, different reliability The data packet enters the virtual channel after being encoded by the CRC encoding module. In the output channel, the data packet output by the register is decoded by the CRC decoding module and then output. The fault tolerance mechanism selection module controls the selection of the crossbar according to the format of different reliability data packets in the input channel. the corresponding transport mechanism;

[0024] The configurable on-chip network fault tolerance method based on the above router is:

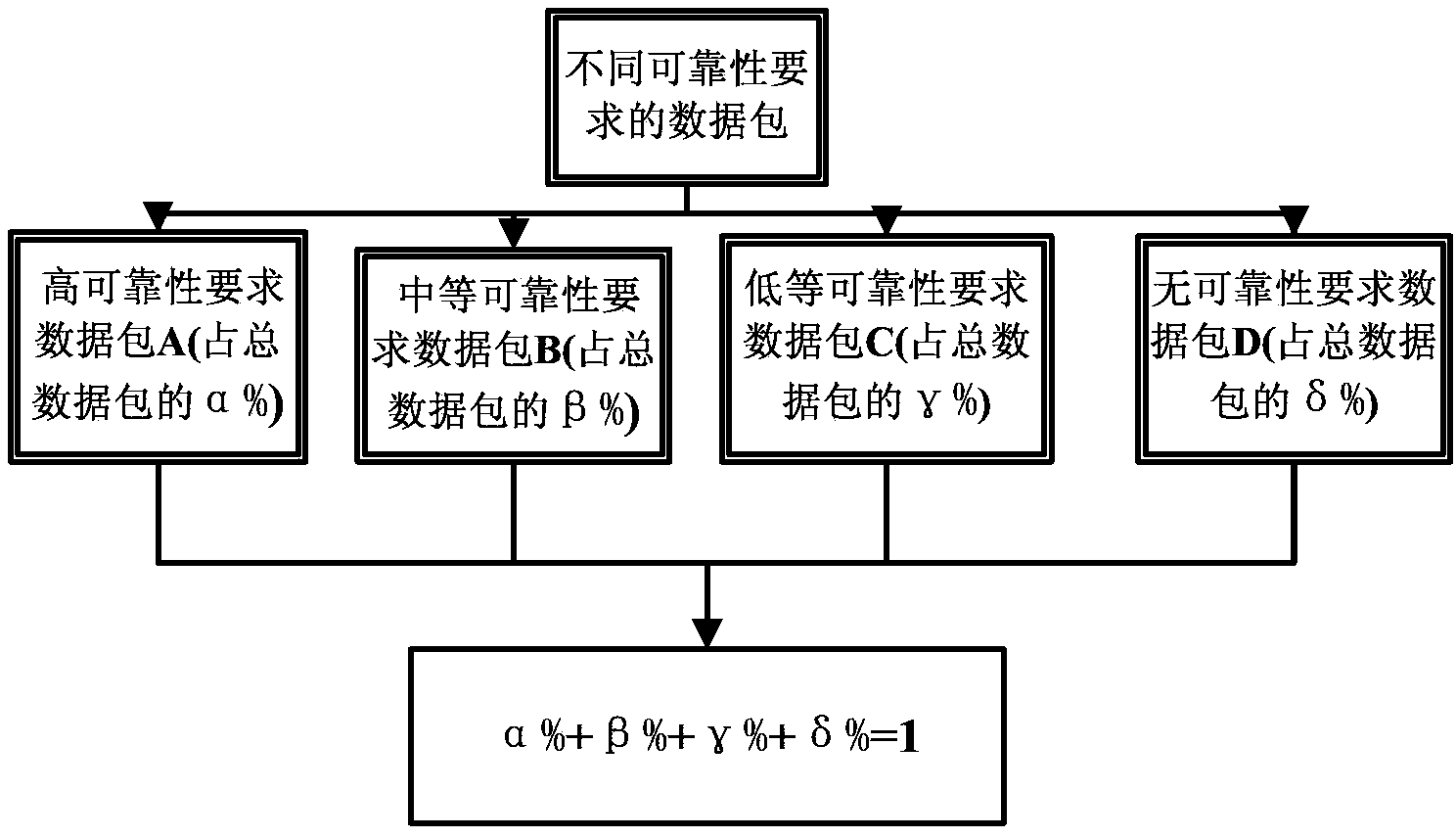

[0025] The source node sends different reliability data packets to the reliabilit...

specific Embodiment approach 2

[0035] Specific embodiment two: combine Image 6 Describe this implementation mode, this implementation mode is a further limitation of the configurable network-on-chip fault-tolerant method described in the specific embodiment one, A-level reliability fault-tolerant strategy, which includes the following steps:

[0036] Step 1: Redundant backups are set for the header flakes, data flakes and tail flakes of data packet A required for high reliability of α%;

[0037] Step 2: Carry out CRC encoding to the redundant backup described in step 1 into the original data packet;

[0038] Step 3: Set up a redundant backup for the original data packet, and use the End-and-Hop data transmission mechanism for data transmission;

[0039] Step 4: Select a routing algorithm to transmit the original data packet and redundant backup:

[0040] Use the XY routing algorithm to transmit the original data packet, and use the YX routing algorithm to transmit the redundant backup data packet;

[00...

specific Embodiment approach 3

[0045] Specific embodiment three: combine Figure 7 Describe this implementation mode, this implementation mode is a further limitation of the configurable network-on-chip fault-tolerant method described in the specific embodiment one, the B-level reliability fault-tolerant strategy, which includes the following steps:

[0046] Step 1: The medium reliability of β% requires the data chip of data packet B to be set as redundant backup;

[0047] Step 2: Carry out CRC encoding to the redundant backup described in step 1 into the original data packet;

[0048] Step 3: Set up a redundant backup for the original data packet, and use the Hop-by-Hop data transmission mechanism for data transmission;

[0049] Step 4: Select a routing algorithm to transmit the original data packet and redundant backup:

[0050] Use the XY routing algorithm to transmit the original data packet, and use the YX routing algorithm to transmit the redundant backup data packet;

[0051] Step five: set a pari...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More