Polysilicon dummy gate electrostatic discharge device with increased sustain voltage and manufacturing method thereof

A technology of maintaining voltage and electrostatic discharge, which is applied in the fields of electric solid-state devices, semiconductor/solid-state device manufacturing, electrical components, etc. Effects of ESD Robustness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] The present invention will be further described below in conjunction with the accompanying drawings and embodiments.

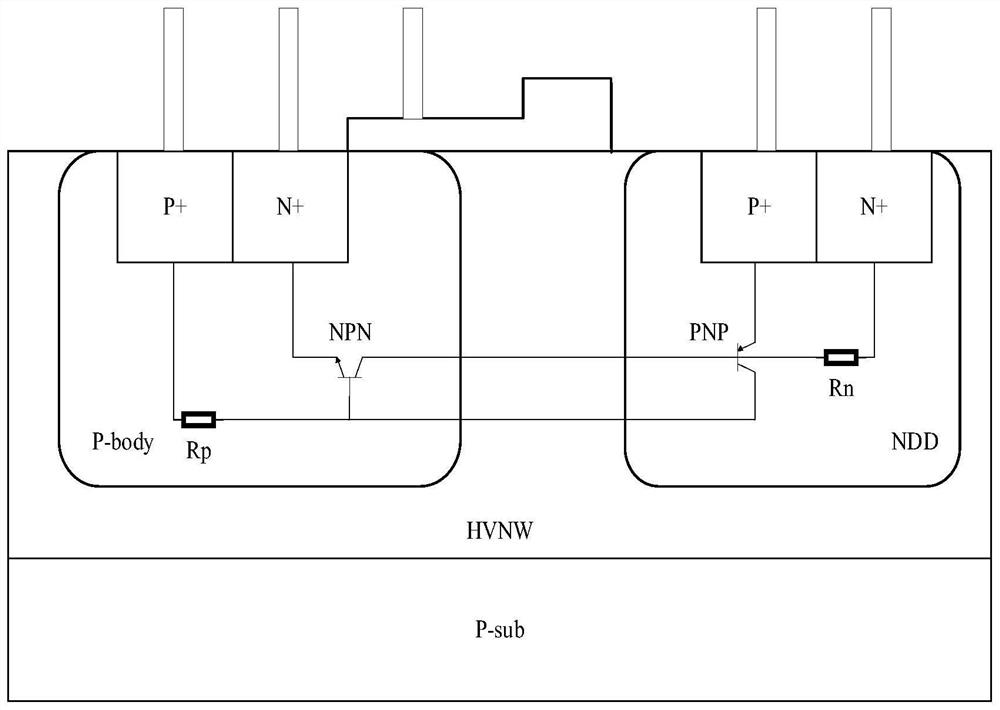

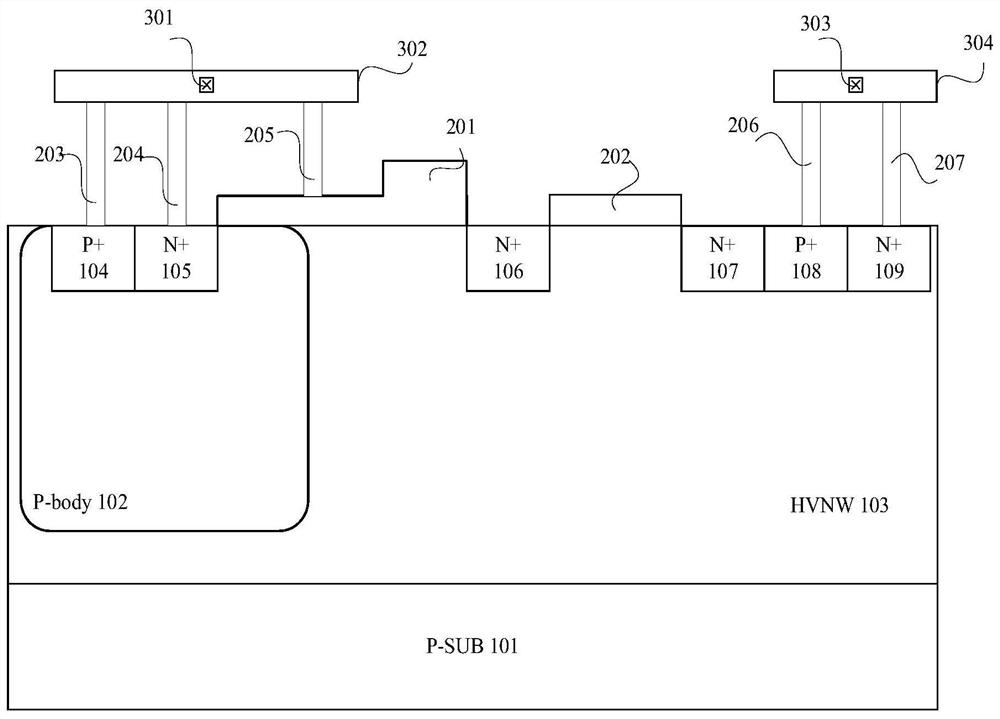

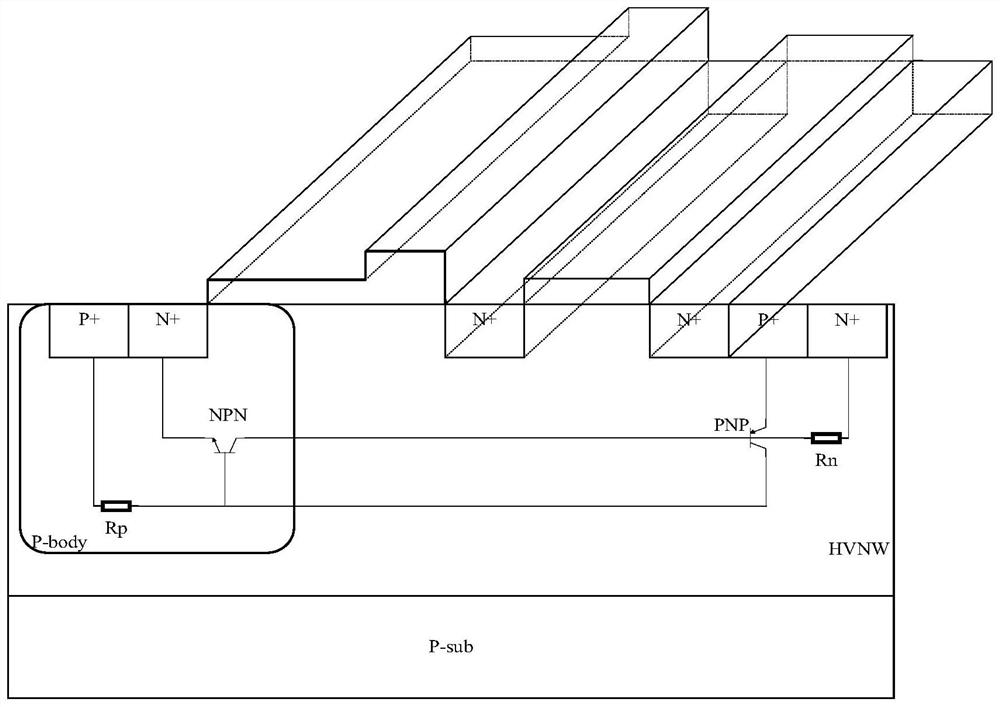

[0033] Such as figure 2 , image 3 As shown, a polysilicon dummy gate ESD device with increased sustain voltage includes substrate P-SUB101, P-body region 102, HVNW region 103, first P+ implantation region 104, first N+ implantation region 105, second N+ implanted region 106, third N+ implanted region 107, second P+ implanted region 108, fourth N+ implanted region 109, first polysilicon gate 201, second polysilicon dummy gate 202, the substrate P-SUB 101 A HVNW region 103 is arranged in the middle, and a P-body region 102 is arranged in the left half of the HVNW region 103. In the P-body region 102, a first P+ implantation region 104, a first N+ implantation region 105, and a A polysilicon gate 201 spans the junction of the P-body region 102 and the HVNW region 103, and the second N+ implantation region 106 and the second polysilicon dummy gate 202 a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More